【开源】DA14580-GPIO实验教程——疯壳·ARM双处理器开发板系列

目录

第一节 LED硬件电路

第二节 GPIO寄存器

2.1 GPIO引脚介绍

2.2寄存器介绍

2.2.1 P0数据寄存器

2.2.2 P0设置数据寄存器

2.2.3 P0复位数据寄存器

2.2.4 P00模式寄存器

2.2.5 P1~P3的寄存器配置

2.3 寄存器配置讲解

第三节 GPIO实验

- LED硬件电路

板子中有一个可控LED,接在DA14580的P24引脚,LED串联1K的限流电阻,如下图所示:

第二节 GPIO寄存器

2.1 GPIO引脚介绍

DA14580的I/O引脚功能可以通过软件配置,分为4组,分别为Port0、Port1、Port2、Port3,其中Port2只在QFN40与QFN48封装的芯片中,Port3只在QFN48封装的芯片中。

Port0有8个引脚,Port1有6个引脚(其中包括DEBUG引脚SW_CLK与SWDIO),Port2有10个引脚,Port3有8个引脚;

每个引脚都可以选择上拉或者下拉25KOhm的电阻;

每个引脚上拉电压在VBAT3V(降压模式)与VBAT1V(升压模式)两者可选;

4路模数转换的引脚固定分配为Port0中的0:3引脚;

当系统进入睡眠模式时,引脚保持最后的状态。

2.2寄存器介绍

2.2.1 P0数据寄存器

15:8位:保留不使用;

7:0位:写该寄存器则设置P0输出寄存器的值,读该寄存器则返回P0口的值。

2.2.2 P0设置数据寄存器

15:8位:保留不使用;

7:0位:写’1’到对应位则对应的引脚置’1’,写’0’无效,读该寄存器则返回0。

2.2.3 P0复位数据寄存器

15:8位:保留不使用;

7:0位:写’1’到对应位则对应的引脚置’0’,写’0’无效,读该寄存器则返回0。

2.2.4 P00模式寄存器

15:10位:保留不使用;

9:8位:设置引脚的上拉、下拉电阻的模式,00为输入,无电阻;01为输入,上拉电阻;10为输入,下拉电阻;11为输出,无电阻;在ADC模式中该位的设置无效。

7:5位:保留不使用;

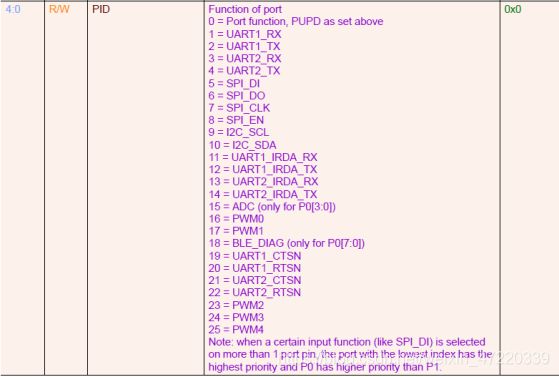

4:0位:设置引脚功能,0~25分别对应不同的功能,具体看上图,注:当一个输入功能设置为多个引脚时,引脚序号越低优先级越高,即优先选用序号低的引脚设置为该功能。P0的优先级比P1的高。

2.2.5 P1~P3的寄存器配置

参照P0寄存器的配置,需要注意的是P14与P15两个引脚模式的默认值是1,即默认上拉电阻。

注:P14与P15为SWD调试接口的时钟与数据接口,在使用Jlink调试过程中不要使用这两个引脚。

2.3 寄存器配置讲解

#define P0_DATA_REG (* ( volatile uint16*)0x50003000)

#define P0_SET_DATA_REG (* ( volatile uint16*)0x50003002)

#define P0_RESET_DATA_REG (* ( volatile uint16*)0x50003004)

#define P00_MODE_REG (* ( volatile uint16*)0x50003006)

#define P01_MODE_REG (* ( volatile uint16*)0x50003008)

#define P02_MODE_REG (* ( volatile uint16*)0x5000300A)

#define P03_MODE_REG (* ( volatile uint16*)0x5000300C)

#define P04_MODE_REG (* ( volatile uint16*)0x5000300E)

#define P05_MODE_REG (* ( volatile uint16*)0x50003010)

#define P06_MODE_REG (* ( volatile uint16*)0x50003012)

#define P07_MODE_REG (* ( volatile uint16*)0x50003014)

如果对P0整体操作,可以使用P0_DATA_REG寄存器,若使P0[7:0] = 0xaa,因为以上宏定义是定义的地址,则寄存器操作为P0_DATA_REG=0xaa;

如果要读取P0的状态值,则通过读取P0_DATA_REG寄存器,P0_STATUS = P0_DATA_REG,若要读取某一位的状态值,则通过与操作之后返回逻辑值即可。

作为输出时P0_DATA_REG适合对整体P0口操作,而对于某一位进行操作则需要经过一些逻辑操作保持其它位的值不变,不是很方便。而P0_SET_DATA_REG和P0_RESET_DATA_REG这两个寄存器对位操作就十分方便。对某一位置’0’或置’1’只需对应位赋1,其它位赋0即可,因为该寄存器忽视写0操作。若使P00 = 1,P01 = 0则P0_SET_DATA_REG =0x01; P0_RESET _DATA_REG=0x02;

P0[x]_MODE_REG是P0口某一位的操作模式的设置寄存器,例如配置P00为输入口,不上拉电阻,P01为I2C_SDA,P02为输出口,则

P00_ MODE _DATA_REG=0x00;

P01_ MODE _DATA_REG=0x0a;

P02_ MODE _DATA_REG=0x30;

第三节 GPIO实验

实验需要使用的模块有:手机开发板底板,Jlink调试工具,杜邦线、3.7V锂电池或Mocro USB线。

使用JLINK通过杜邦线连接手机蓝牙位于手机主控底板,连接方式如下:

将JLINK插上电脑的USB接口,连接好之后给手机主控底板供电,详细的介绍可以参考《如何上电》教程,路径为:..\WT_Mobile\0.从这里开始\0.开机测试。

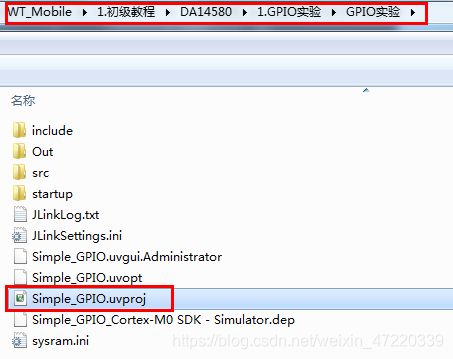

打开GPIO实验的Keil工程Simple_GPIO.uvproj,位于目录:..\WT_Mobile\1.初级教程\DA14580\1.GPIO实验\GPIO实验。如下图所示: