FPGA刷题P4:使用8-3优先编码器实现16-4优先编码器、 使用3-8译码器实现全减器、 实现3-8译码器、使用3-8译码器实现逻辑函数、数据选择器实现逻辑电路

P1~3大家可以进去我主页自行寻找就不放链接了,下面继续分享牛客网Verilog题目解析

目录

使用8-3优先编码器实现16-4优先编码器

使用3-8译码器实现全减器

实现3-8译码器

使用3-8译码器实现逻辑函数

数据选择器实现逻辑电路

使用8-3优先编码器实现16-4优先编码器

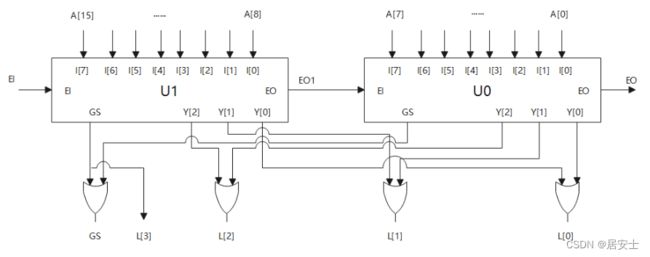

这个题8-3优先编码器代码已经给出了,需要我们通过例化已有代码,实现16-4编码器,可以理解为2块8-3优先编码器并联起来了,电路连接图如下:

我们可以参考电路图写代码:

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);

assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];

assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

//assign GS = EI&(| I);

endmodule

module encoder_164(

input [15:0] A ,

input EI ,

output wire [3:0] L ,

output wire GS ,

output wire EO

);

//例化

wire EO1 ;

wire [2:0] Y0 ;

wire [2:0] Y1 ;

wire GS0 ;

encoder_83 U0(

.I (A[7:0]),//输入低8位

.EI (EO1 ),

.Y (Y0 ),

.GS (GS0 ),

.EO (EO )

);

encoder_83 U1(

.I (A[15:8]),//输入高8位

.EI (EI ),

.Y (Y1 ),

.GS (GS1 ),

.EO (EO1 )

);

//将2块8-3 并联起来

assign L[3] = GS1;

assign L[2] = Y1[2] | Y0[2];

assign L[1] = Y1[1] | Y0[1];

assign L[0] = Y1[0] | Y0[0];

assign GS = GS1 | GS0;

endmodule使用3-8译码器实现全减器

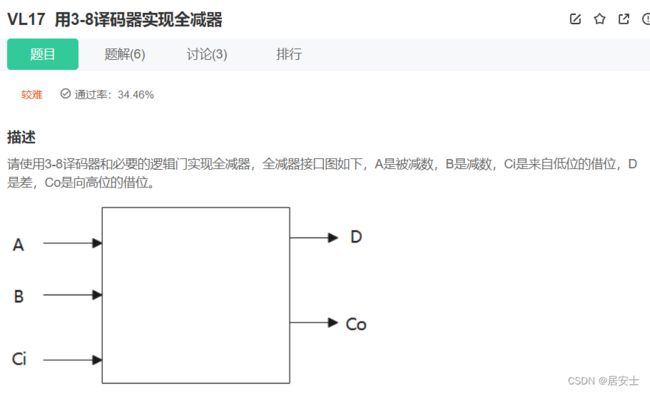

这个题首先写出全减器的真值表:

由真值表可得出,输出D的逻辑表达式用最小项表示为:

D = m1+m2+m4+m7

输出Co的逻辑表达式用最小项表示为:

Co = m1+m2++m3+m7

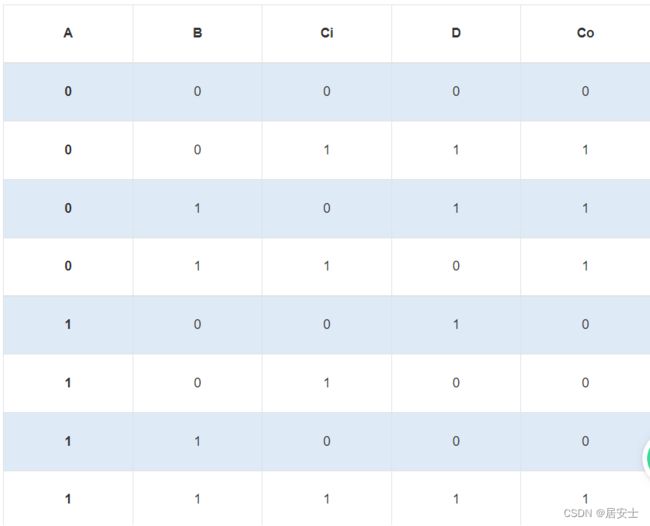

由于译码器的输出为最小项取反,下面需要将表达式中的最小项转换为最小项取反的形式。根据反演定理,转换结果如下:

D = ~(非m1非m2非m3非m7)

Co=~(非m1非m2非m3非m7)

由上式可知,采用与非门即可实现该电路的组合逻辑输出。关键电路如下:

根据电路写代码:

module decoder_38(

input E ,

input A0 ,

input A1 ,

input A2 ,

output reg Y0n ,

output reg Y1n ,

output reg Y2n ,

output reg Y3n ,

output reg Y4n ,

output reg Y5n ,

output reg Y6n ,

output reg Y7n

);

always @(*)begin

if(!E)begin

Y0n = 1'b1;

Y1n = 1'b1;

Y2n = 1'b1;

Y3n = 1'b1;

Y4n = 1'b1;

Y5n = 1'b1;

Y6n = 1'b1;

Y7n = 1'b1;

end

else begin

case({A2,A1,A0})

3'b000 : begin

Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b001 : begin

Y0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b010 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b011 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b100 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b101 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;

end

3'b110 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;

end

3'b111 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;

end

default: begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

endcase

end

end

endmodule

module decoder1(

input A ,

input B ,

input Ci ,

output wire D ,

output wire Co

);

wire Y0_n ;

wire Y1_n ;

wire Y2_n ;

wire Y3_n ;

wire Y4_n ;

wire Y5_n ;

wire Y6_n ;

wire Y7_n ;

decoder_38 U0(

.E (1'b1),

.A0 (Ci ),

.A1 (B ),

.A2 (A ),

.Y0n (Y0_n),

.Y1n (Y1_n),

.Y2n (Y2_n),

.Y3n (Y3_n),

.Y4n (Y4_n),

.Y5n (Y5_n),

.Y6n (Y6_n),

.Y7n (Y7_n)

);

assign D = ~(Y1_n & Y2_n & Y4_n & Y7_n);

assign Co = ~(Y1_n & Y2_n & Y3_n & Y7_n);

endmodule实现3-8译码器

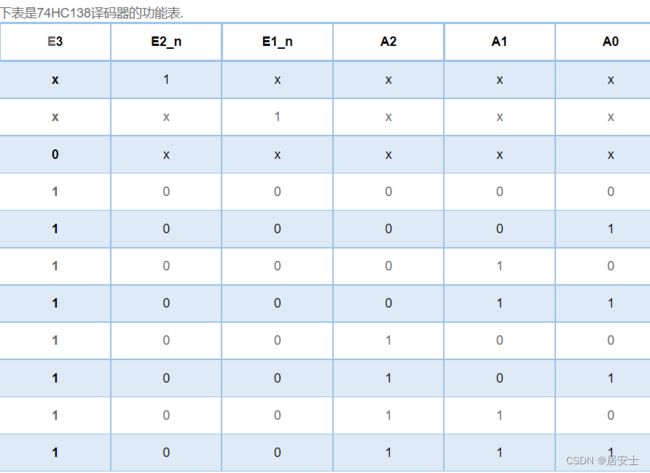

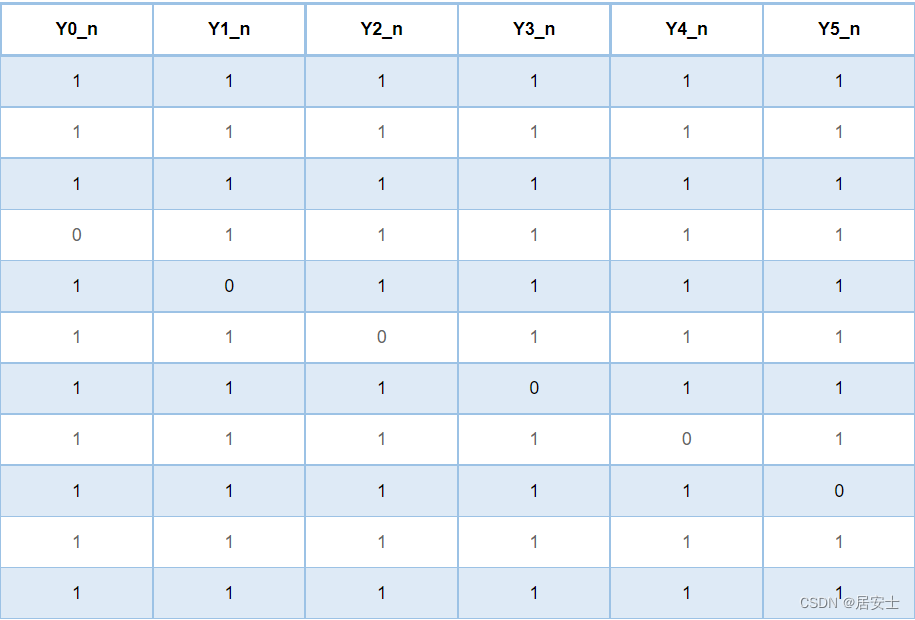

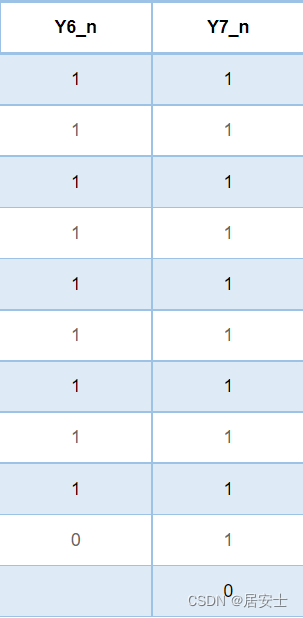

这个题根据真值表写一个3-8译码器,代码如下:

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

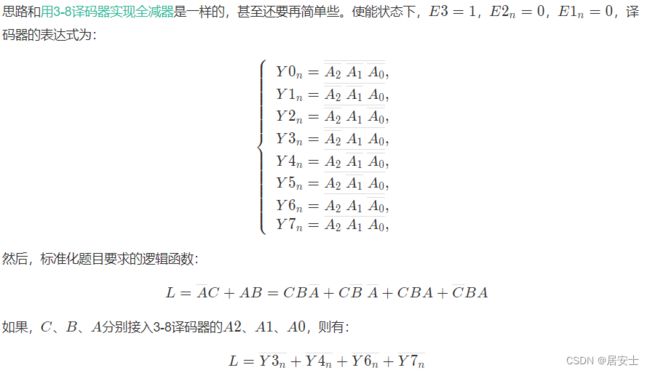

endmodule使用3-8译码器实现逻辑函数

这一题在上一题的基础上,要求实现:

![]()

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire [7:0] Y;

assign L = ~Y[3] + ~Y[4] + ~Y[6] + ~Y[7];

decoder_38 myDecoder(

.E1_n( 0 ),

.E2_n( 0 ),

.E3 ( 1 ),

.A0 ( A ),

.A1 ( B ),

.A2 ( C ),

.Y0_n(Y[0]),

.Y1_n(Y[1]),

.Y2_n(Y[2]),

.Y3_n(Y[3]),

.Y4_n(Y[4]),

.Y5_n(Y[5]),

.Y6_n(Y[6]),

.Y7_n(Y[7])

);

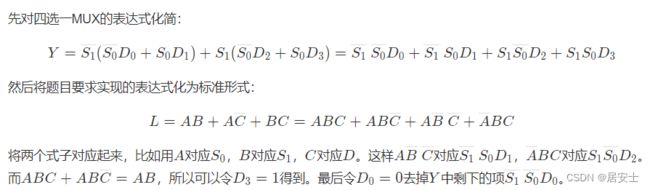

endmodule数据选择器实现逻辑电路

然后我们例化时,直接例化进去即可,代码如下:

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

module sel_exp(

input A ,

input B ,

input C ,

output wire L

);

data_sel U0(

.S0 (B),

.S1 (A),

.D0 (0),

.D1 (C),

.D2 (~C),

.D3 (1),

.Y (L)

);

endmodule