VHDL之package

Pacakge

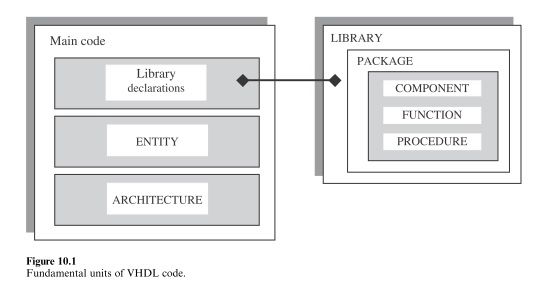

Frequently used pieces of VHDL code are usually written in the form of COMPONENTS, FUNCTIONS, or PROCEDURES. Such codes are then placed inside a PACKAGE and compiled into the destination LIBRARY.

1 Syntax

Besides COMPONENTS, FUNCTIONS, and PROCEDURES, it can also contain TYPE and CONSTANT definitions, among others. Its syntax is presented below.

PACKAGE package_name IS (declarations) END package_name; [PACKAGE BODY package_name IS (FUNCTION and PROCEDURE descriptions) END package_name;]

2 Simple Package

It shows a PACKAGE called my_package. It contains only TYPE and CONSTANT declarations, so a PACKAGE BODY is not necessary.

1 ------------------------------------------------ 2 LIBRARY ieee; 3 USE ieee.std_logic_1164.all; 4 ------------------------------------------------ 5 PACKAGE my_package IS 6 TYPE state IS (st1, st2, st3, st4); 7 TYPE color IS (red, green, blue); 8 CONSTANT vec: STD_LOGIC_VECTOR(7 DOWNTO 0) := "11111111"; 9 END my_package; 10 ------------------------------------------------

The PACKAGE above can now be compiled, becoming then part of our work LIBRARY (or any other). To make use of it in a VHDL code, we have to add a new USE clause to the main code (USE work.my_package.all), as shown below.

1 ------------------------------------ 2 LIBRARY ieee; 3 USE ieee.std_logic_1164.all; 4 USE work.my_package.all; 5 ------------------------------------ 6 ENTITY... 7 ... 8 ARCHITECTURE... 9 ... 10 ------------------------------------

3 Package in ASIC

In ASIC design, use ieee.std_logic_1164, and ieee.numeric_std, NEVER use ieee.std_logic_arith

numeric_std defines numeric types and arithmetic functions for use with synthesis tools.

- two numeric types are defined: UNSIGNED, SIGNED (represents a SIGNED number in vector form)

- base element type is type STD_LOGIC. The leftmost bit is treated as the most significant bit.

- signed vectors are represented in two's complement form.

- contains overloaded arithmetic operators on the SIGNED and UNSIGNED types.

- contains useful type conversions functions.