FPGA--VGA显示实验之Verilog代码描述(时钟模块)

在前一章中我们简单了解了关于VGA接口与协议的内容,这篇文章,我们将立足于实践来介绍一个显示系统的各个部件。

从上图可以看出,我们这个系统包含了三个组件:

- 时钟产生部件:clk_gen

- VGA控制部件:vga_ctrl

- 图像数据生成部件:vga_pic

时钟产生部件功能

我们可以看到,时钟产生部件的主要功能是其余两个部件需要的时钟,这也是最简单的一个部件。

PLL IP核例化过程

由于我们使用的FPGA的时钟基频是50M赫兹,而VGA时序的像素频率需要通过计算得出,因此我们要先计算出我们的像素时钟频率:(参见上节的计算公式)

像素时钟频率大约为25MHZ,因此我们需要对基础时钟进行二分频,具体的做法可以使用Verilog描述分频,或者使用PLL锁相环的IP核进行分频。从实用的角度我们选择后者。

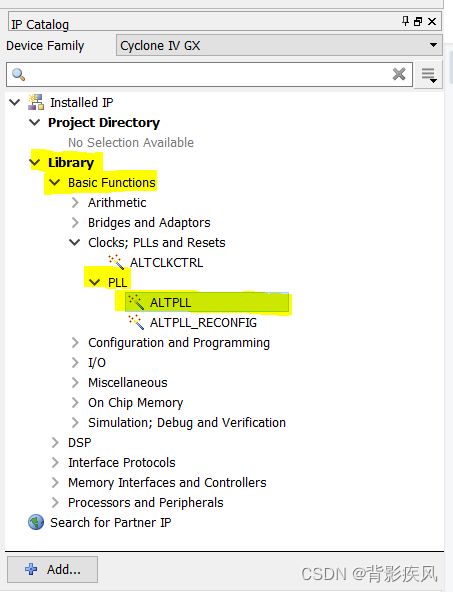

各位看官请看图例:

这时将目光转向右边栏:

之后我们便开始进行配置:

填写我们的PLL部件的名字与存储位置,下面开始PLL的参数配置(Parameter Settings):

相信各位英语水平都比我好,其实这些参数配置看一眼就知道是在干嘛,就是有一些基础知识需要我来补充一下:

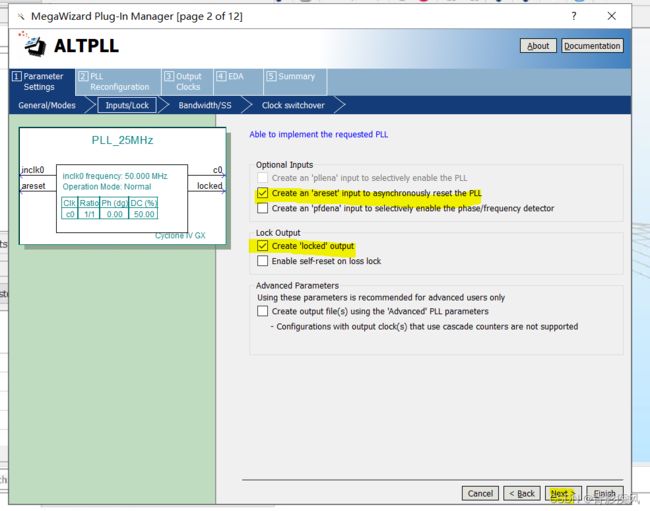

首先就是PLL的结构,左上角给了我们一个PLL模块的模型,输入引脚有两个,分别为输入时钟,复位;输出引脚为 时钟输出(c0,名称可以在右下角改)、锁定引脚Locked。

很多同学有疑问,Locked引脚有啥用?

PLL锁相环是由鉴频(FD)鉴相(PD)器、环路滤波器(LF)、以及压控振荡器(VCO)组成的闭环控制系统,参考频率输入后,由 鉴频鉴相器 和需要的输出的频率进行比较,输出的差值通过环路滤波器以电压形式驱动压控振荡器控制输出频率大小。

闭环系统在达到稳态前会经历一段不怎么稳定的过渡态,Locked引脚在过渡态时为低电平,在输出稳定后为高电平。这便是Locked引脚的作用。

回到配置清单,我们看到,选项一要求我们填写我们使用FPGA的速度等级;选项二要求我们填写输入PLL的频率是多少;选项三让我们选择我们要生成的PLL类型,很明显我们只能默认;选项四为PLL的四种输出类型:

这个页面是让我们选择PLL的输入与输出引脚,一般情况下,我们都会选择创建一个复位引脚和Locked引脚,点击Next。

上图主要是配置扩展频谱时钟和带宽,属于PLL器件的高级特性,在这里我们不使用,选择auto即可点击next进行下一步的配置。

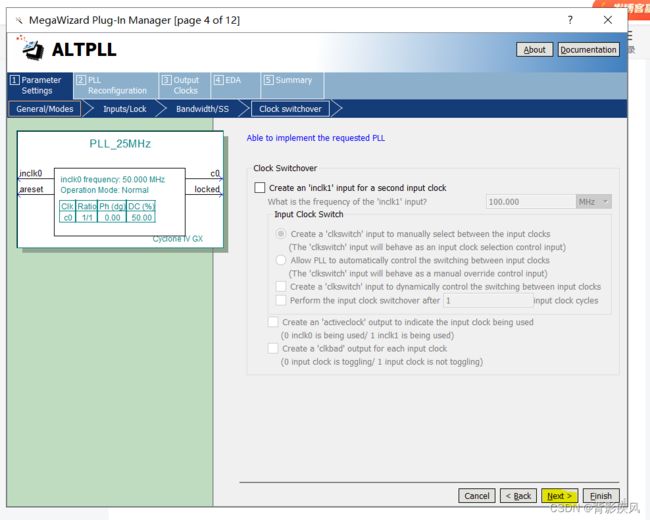

这是参数配置的最后一步,主要是配置PLL的时钟切换功能,利用简单的英语知识可以知道,如果配置了这项功能,那么我们可以切换PLL的输入时钟,对于我们这个项目而言,我们使用一个50MHZ的基频即可,无需配置,直接点击next。

下面我们就进入到了下一项:Dynami Reconfigration,即动态重配置功能,配置该项功能后PLL可以通过输入引脚对参数进行实时的配置,属于高级特性,咱们目前也用不上,所以直接点击next。

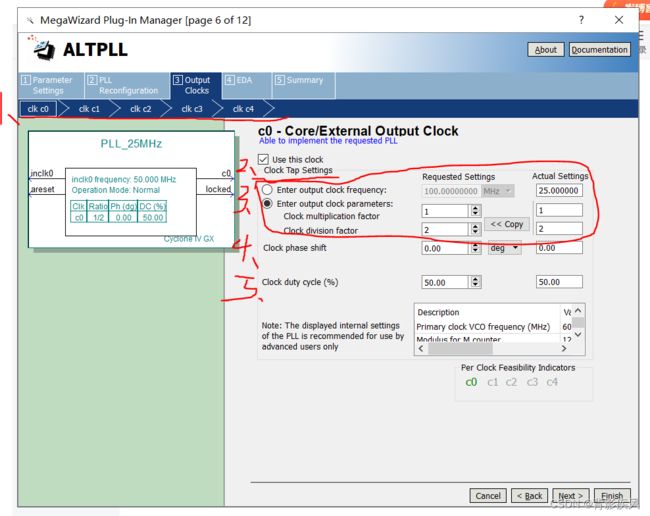

这页的配置是我们的重头戏,即配置PLL的分频与倍频参数;这部分的配置共包含了五页,这意味着咱们的PLL最多可以配置五路的输出,而且每一路的输出都是可编程的,只要勾选了选项2,那么这个输出引脚就会被使能。

这页的配置是我们的重头戏,即配置PLL的分频与倍频参数;这部分的配置共包含了五页,这意味着咱们的PLL最多可以配置五路的输出,而且每一路的输出都是可编程的,只要勾选了选项2,那么这个输出引脚就会被使能。

选项三是配置输出频率的,第一个子选项是直接输入配置的方式,只要在Requested Settings选项中直接输入需要的频率就可以了。相对地,第二个子选项是通过配置 倍频因子和分频因子来配置输出频率,两个选项的最终结构都可以在Actual Settings 选项框中看到。

选项四是配置相移角度的,这个我们的输出和输入同相,故配置为零。

选项五是配置输出占空比的,这个我们默认50%,配置好后我们点击next即可。

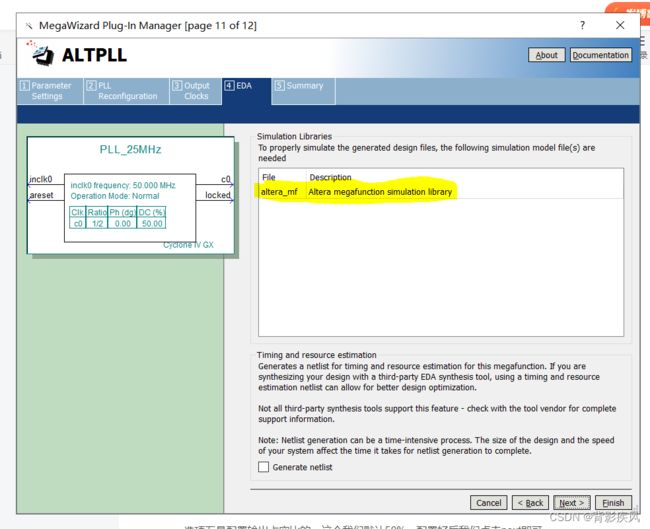

接下来我们开始配置EDA项,此项主要面对仿真,没有什么需要特别配置的地方,但是却有一个值得注意的点:它提示我们在仿真PLL IP核时需要添加的Alter 仿真库。因为我们使用EDA工具生成的IP核是相当于一个黑箱,里面怎么样是未知的,当我们使用Modlesim进行单独的仿真时,就需要添加Alter的仿真库才能进行仿真,需要添加什么库呢?就是黄色标记的库。

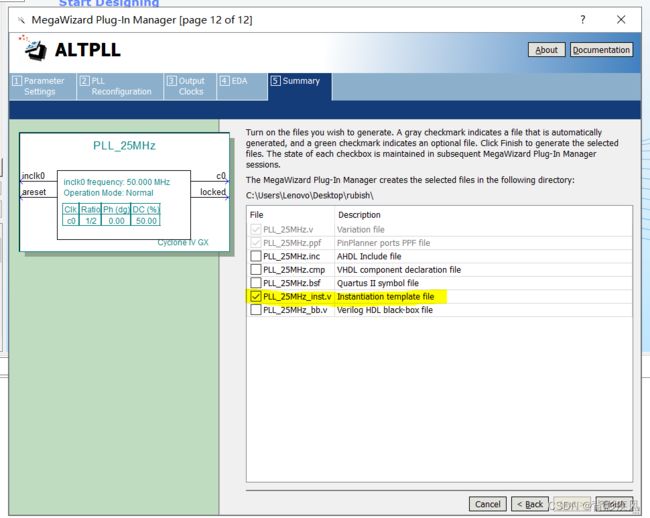

最后一项是总体设置(Summary),具体配置生成的文件,其中我们可以看到开头两项是默认勾选的,其实有了这两项就已经足够了,但我们可以把倒数第二项实例化模板一起勾选上,其余的可以都不用勾选。

下面的是PLL.v的内容,即原模块代码,注意一般只适用于同一家的编译器:

// megafunction wizard: %ALTPLL%

// GENERATION: STANDARD

// VERSION: WM1.0

// MODULE: altpll

// ============================================================

// File Name: PLL_25MHz.v

// Megafunction Name(s):

// altpll

//

// Simulation Library Files(s):

// altera_mf

// ============================================================

// ************************************************************

// THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

//

// 14.1.0 Build 186 12/03/2014 SJ Full Version

// ************************************************************

//Copyright (C) 1991-2014 Altera Corporation. All rights reserved.

//Your use of Altera Corporation's design tools, logic functions

//and other software and tools, and its AMPP partner logic

//functions, and any output files from any of the foregoing

//(including device programming or simulation files), and any

//associated documentation or information are expressly subject

//to the terms and conditions of the Altera Program License

//Subscription Agreement, the Altera Quartus II License Agreement,

//the Altera MegaCore Function License Agreement, or other

//applicable license agreement, including, without limitation,

//that your use is for the sole purpose of programming logic

//devices manufactured by Altera and sold by Altera or its

//authorized distributors. Please refer to the applicable

//agreement for further details.

// synopsys translate_off

`timescale 1 ps / 1 ps

// synopsys translate_on

module PLL_25MHz (

areset,

inclk0,

c0,

locked);

input areset;

input inclk0;

output c0;

output locked;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_off

`endif

tri0 areset;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_on

`endif

wire [0:0] sub_wire2 = 1'h0;

wire [4:0] sub_wire3;

wire sub_wire5;

wire sub_wire0 = inclk0;

wire [1:0] sub_wire1 = {sub_wire2, sub_wire0};

wire [0:0] sub_wire4 = sub_wire3[0:0];

wire c0 = sub_wire4;

wire locked = sub_wire5;

altpll altpll_component (

.areset (areset),

.inclk (sub_wire1),

.clk (sub_wire3),

.locked (sub_wire5),

.activeclock (),

.clkbad (),

.clkena ({6{1'b1}}),

.clkloss (),

.clkswitch (1'b0),

.configupdate (1'b0),

.enable0 (),

.enable1 (),

.extclk (),

.extclkena ({4{1'b1}}),

.fbin (1'b1),

.fbmimicbidir (),

.fbout (),

.fref (),

.icdrclk (),

.pfdena (1'b1),

.phasecounterselect ({4{1'b1}}),

.phasedone (),

.phasestep (1'b1),

.phaseupdown (1'b1),

.pllena (1'b1),

.scanaclr (1'b0),

.scanclk (1'b0),

.scanclkena (1'b1),

.scandata (1'b0),

.scandataout (),

.scandone (),

.scanread (1'b0),

.scanwrite (1'b0),

.sclkout0 (),

.sclkout1 (),

.vcooverrange (),

.vcounderrange ());

defparam

altpll_component.bandwidth_type = "AUTO",

altpll_component.clk0_divide_by = 2,

altpll_component.clk0_duty_cycle = 50,

altpll_component.clk0_multiply_by = 1,

altpll_component.clk0_phase_shift = "0",

altpll_component.compensate_clock = "CLK0",

altpll_component.inclk0_input_frequency = 20000,

altpll_component.intended_device_family = "Cyclone IV GX",

altpll_component.lpm_hint = "CBX_MODULE_PREFIX=PLL_25MHz",

altpll_component.lpm_type = "altpll",

altpll_component.operation_mode = "NORMAL",

altpll_component.pll_type = "AUTO",

altpll_component.port_activeclock = "PORT_UNUSED",

altpll_component.port_areset = "PORT_USED",

altpll_component.port_clkbad0 = "PORT_UNUSED",

altpll_component.port_clkbad1 = "PORT_UNUSED",

altpll_component.port_clkloss = "PORT_UNUSED",

altpll_component.port_clkswitch = "PORT_UNUSED",

altpll_component.port_configupdate = "PORT_UNUSED",

altpll_component.port_fbin = "PORT_UNUSED",

altpll_component.port_inclk0 = "PORT_USED",

altpll_component.port_inclk1 = "PORT_UNUSED",

altpll_component.port_locked = "PORT_USED",

altpll_component.port_pfdena = "PORT_UNUSED",

altpll_component.port_phasecounterselect = "PORT_UNUSED",

altpll_component.port_phasedone = "PORT_UNUSED",

altpll_component.port_phasestep = "PORT_UNUSED",

altpll_component.port_phaseupdown = "PORT_UNUSED",

altpll_component.port_pllena = "PORT_UNUSED",

altpll_component.port_scanaclr = "PORT_UNUSED",

altpll_component.port_scanclk = "PORT_UNUSED",

altpll_component.port_scanclkena = "PORT_UNUSED",

altpll_component.port_scandata = "PORT_UNUSED",

altpll_component.port_scandataout = "PORT_UNUSED",

altpll_component.port_scandone = "PORT_UNUSED",

altpll_component.port_scanread = "PORT_UNUSED",

altpll_component.port_scanwrite = "PORT_UNUSED",

altpll_component.port_clk0 = "PORT_USED",

altpll_component.port_clk1 = "PORT_UNUSED",

altpll_component.port_clk2 = "PORT_UNUSED",

altpll_component.port_clk3 = "PORT_UNUSED",

altpll_component.port_clk4 = "PORT_UNUSED",

altpll_component.port_clk5 = "PORT_UNUSED",

altpll_component.port_clkena0 = "PORT_UNUSED",

altpll_component.port_clkena1 = "PORT_UNUSED",

altpll_component.port_clkena2 = "PORT_UNUSED",

altpll_component.port_clkena3 = "PORT_UNUSED",

altpll_component.port_clkena4 = "PORT_UNUSED",

altpll_component.port_clkena5 = "PORT_UNUSED",

altpll_component.port_extclk0 = "PORT_UNUSED",

altpll_component.port_extclk1 = "PORT_UNUSED",

altpll_component.port_extclk2 = "PORT_UNUSED",

altpll_component.port_extclk3 = "PORT_UNUSED",

altpll_component.self_reset_on_loss_lock = "OFF",

altpll_component.width_clock = 5;

endmodule

// ============================================================

// CNX file retrieval info

// ============================================================

// Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0"

// Retrieval info: PRIVATE: BANDWIDTH STRING "1.000"

// Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "1"

// Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz"

// Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low"

// Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1"

// Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0"

// Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0"

// Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0"

// Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "0"

// Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0"

// Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0"

// Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0"

// Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0"

// Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "c0"

// Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "8"

// Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "2"

// Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000"

// Retrieval info: PRIVATE: EFF_OUTPUT_FREQ_VALUE0 STRING "25.000000"

// Retrieval info: PRIVATE: EXPLICIT_SWITCHOVER_COUNTER STRING "0"

// Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0"

// Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1"

// Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "0"

// Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0"

// Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575"

// Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1"

// Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000"

// Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz"

// Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "100.000"

// Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1"

// Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1"

// Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz"

// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV GX"

// Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1"

// Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "1"

// Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1"

// Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available"

// Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0"

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg"

// Retrieval info: PRIVATE: MIG_DEVICE_SPEED_GRADE STRING "Any"

// Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0"

// Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1"

// Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1"

// Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "10.00000000"

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "0"

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz"

// Retrieval info: PRIVATE: PHASE_RECONFIG_FEATURE_ENABLED STRING "1"

// Retrieval info: PRIVATE: PHASE_RECONFIG_INPUTS_CHECK STRING "0"

// Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "0.00000000"

// Retrieval info: PRIVATE: PHASE_SHIFT_STEP_ENABLED_CHECK STRING "0"

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "deg"

// Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "1"

// Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1"

// Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_FBMIMIC_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0"

// Retrieval info: PRIVATE: RECONFIG_FILE STRING "PLL_25MHz.mif"

// Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0"

// Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "1"

// Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0"

// Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0"

// Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0"

// Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000"

// Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz"

// Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500"

// Retrieval info: PRIVATE: SPREAD_USE STRING "0"

// Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0"

// Retrieval info: PRIVATE: STICKY_CLK0 STRING "1"

// Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1"

// Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1"

// Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"

// Retrieval info: PRIVATE: USE_CLK0 STRING "1"

// Retrieval info: PRIVATE: USE_CLKENA0 STRING "0"

// Retrieval info: PRIVATE: USE_MIL_SPEED_GRADE NUMERIC "0"

// Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0"

// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all

// Retrieval info: CONSTANT: BANDWIDTH_TYPE STRING "AUTO"

// Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "2"

// Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50"

// Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "1"

// Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "0"

// Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0"

// Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000"

// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV GX"

// Retrieval info: CONSTANT: LPM_TYPE STRING "altpll"

// Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL"

// Retrieval info: CONSTANT: PLL_TYPE STRING "AUTO"

// Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CONFIGUPDATE STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PHASECOUNTERSELECT STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PHASEDONE STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PHASESTEP STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PHASEUPDOWN STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANCLKENA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: SELF_RESET_ON_LOSS_LOCK STRING "OFF"

// Retrieval info: CONSTANT: WIDTH_CLOCK NUMERIC "5"

// Retrieval info: USED_PORT: @clk 0 0 5 0 OUTPUT_CLK_EXT VCC "@clk[4..0]"

// Retrieval info: USED_PORT: areset 0 0 0 0 INPUT GND "areset"

// Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0"

// Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0"

// Retrieval info: USED_PORT: locked 0 0 0 0 OUTPUT GND "locked"

// Retrieval info: CONNECT: @areset 0 0 0 0 areset 0 0 0 0

// Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0

// Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0

// Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0

// Retrieval info: CONNECT: locked 0 0 0 0 @locked 0 0 0 0

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz.ppf TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz.inc FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz.cmp FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz.bsf FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz_inst.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL PLL_25MHz_bb.v FALSE

// Retrieval info: LIB_FILE: altera_mf

// Retrieval info: CBX_MODULE_PREFIX: ON

下面的是实例化文件的内容,方便我们的使用

PLL_25MHz PLL_25MHz_inst (

.areset ( areset_sig ),

.inclk0 ( inclk0_sig ),

.c0 ( c0_sig ),

.locked ( locked_sig )

);

至此,我们的PLL模块就已经配置完成了!

下一步,我们将编写我们的时序控制器代码!