【牛客网刷题】VL8-VL10 generate for语句、比较数大小、function的使用

写在前面

本系列博客记录牛客网刷题记录

日拱一卒,功不唐捐!

目录

VL8 使用generate for语句简化代码

题目描述

输入描述

输出描述

RTL 设计

testbench 设计

仿真测试

VL9 使用子模块实现三输入数的大小比较

题目描述

输入描述

输出描述

题目分析

RTL 设计

testbench 设计

仿真测试

VL10 使用函数实现数据大小端转换

题目描述

输入描述

输出描述

RTL 设计

testbench 设计

仿真测试

VL8 使用generate for语句简化代码

题目描述

在某个module中包含了很多相似的连续赋值语句,请使用generata…for语句编写代码,替代该语句,要求不能改变原module的功能。

使用Verilog HDL实现以上功能并编写testbench验证。

module template_module(

input [7:0] data_in,

output [7:0] data_out

);

assign data_out [0] = data_in [7];

assign data_out [1] = data_in [6];

assign data_out [2] = data_in [5];

assign data_out [3] = data_in [4];

assign data_out [4] = data_in [3];

assign data_out [5] = data_in [2];

assign data_out [6] = data_in [1];

assign data_out [7] = data_in [0];

endmodule输入描述

data_in:8bit位宽的无符号数

输出描述

data_out:8bit位宽的无符号数

RTL 设计

`timescale 1ns/1ns

module gen_for_module(

input [7:0] data_in,

output [7:0] data_out

);

generate

genvar i;

for (i=0;i<8;i=i+1) begin

assign data_out[i] = data_in[7-i];

end

endgenerate

endmoduletestbench 设计

`timescale 1ns/1ns

module tb_gen_for_module();

reg [7:0] data_in;

wire [7:0] data_out;

gen_for_module inst_gen_for_module (

.data_in(data_in),

.data_out(data_out)

);

initial begin

data_in <= 8'd1;

#10

data_in <= 8'd2;

#10

data_in <= 8'd3;

#10

data_in <= 8'd4;

#10

data_in <= 8'd5;

#10

data_in <= 8'd6;

#10

data_in <= 8'd7;

$finish;

end

//verdi

initial begin

$fsdbDumpfile("tb_gen_for_module.fsdb");

$fsdbDumpvars(0);

end

endmodule仿真测试

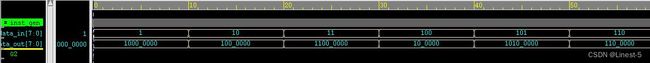

从仿真图可以看到,根据输入的八位宽数据,按照位倒转输出。

VL9 使用子模块实现三输入数的大小比较

题目描述

在数字芯片设计中,通常把完成特定功能且相对独立的代码编写成子模块,在需要的时候再在主模块中例化使用,以提高代码的可复用性和设计的层次性,方便后续的修改。

请编写一个子模块,将输入两个8bit位宽的变量data_a,data_b,并输出data_a,data_b之中较小的数。并在主模块中例化,实现输出三个8bit输入信号的最小值的功能。

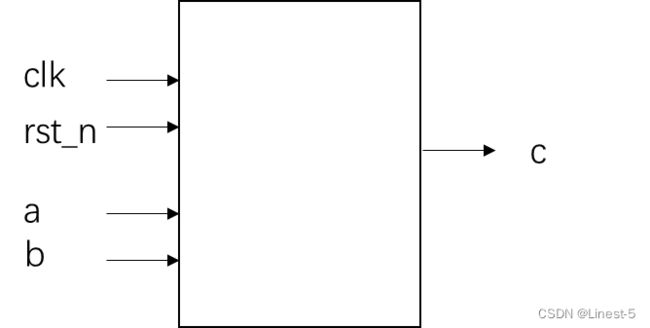

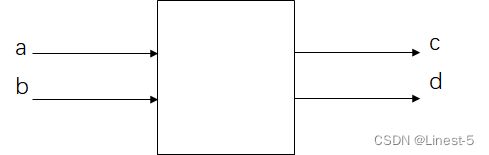

子模块的信号接口图如下:

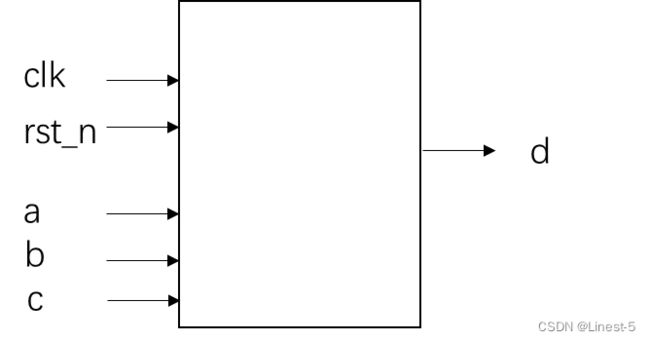

主模块的信号接口图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述

clk:系统时钟

rst_n:异步复位信号,低电平有效

a,b,c:8bit位宽的无符号数

输出描述

d:8bit位宽的无符号数,表示a,b,c中的最小值

题目分析

题目的要求是定义子模块,在顶层中例化子模块,这样的好处是可以简化代码量,因为有些功能描述是重复的。基本思路就是设计一个子模块,其作用为比较两个输出值的较小值并输出,因为在顶层中例化两次子模块即可实现三输入数据输出最小值了。

RTL 设计

将子模块和顶层模块写在同一个.v文件中。

`timescale 1ns/1ns

module main_mod(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

input [7:0] c,

output [7:0] d

);

reg [7:0] c_reg;

wire [7:0] min;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

c_reg <= 'd0;

end

else begin

c_reg <= c;

end

end

compare_min compare_min_inst1 (

.clk (clk),

.rst_n (rst_n),

.a (a),

.b (b),

.c (min)

);

compare_min compare_min_inst2 (

.clk (clk),

.rst_n (rst_n),

.a (min),

.b (c_reg),

.c (d)

);

endmodule

module compare_min(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output reg [7:0] c

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

c <= 8'd0;

end

else if (a < b) begin

c <= a;

end

else begin

c <= b;

end

end

endmoduletestbench 设计

`timescale 1ns/1ns

module tb_main_mod();

reg clk;

reg rst_n;

reg [7:0] a;

reg [7:0] b;

reg [7:0] c;

wire [7:0] d;

initial begin

clk = 'd1;

rst_n <= 'd0;

a <= 'd0;

b <= 'd0;

c <= 'd0;

#20

rst_n <= 'd1;

#200

$finsih;

end

always #5 clk = ~clk;

always #10 a <= {$random} % 9'd256;

always #10 b <= {$random} % 9'd256;

always #10 c <= {$random} % 9'd256;

main_mod inst_main_mod (

.clk (clk),

.rst_n (rst_n),

.a (a),

.b (b),

.c (c),

.d (d)

);

//verdi

initial begin

$fsdbDumpfile("tb_main_mod.fsdb");

$fsdbDumpvars(0);

end

endmodule仿真测试

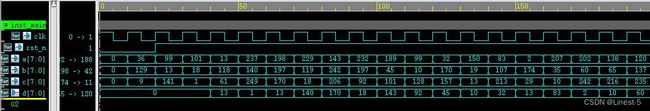

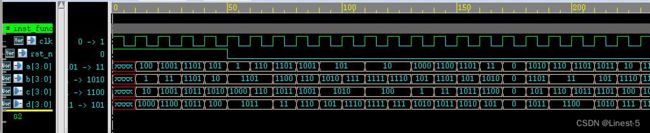

因为三个输入数据经过两次比较例化才得到最小值,所以最终得到的最小值数需要延后两拍输出。

VL10 使用函数实现数据大小端转换

题目描述

在数字芯片设计中,经常把实现特定功能的模块编写成函数,在需要的时候再在主模块中调用,以提高代码的复用性和提高设计的层次,分别后续的修改。

请用函数实现一个4bit数据大小端转换的功能。实现对两个不同的输入分别转换并输出。

程序的接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述

clk:系统时钟

rst_n:异步复位信号,低电平有效

a,b:4bit位宽的无符号数

输出描述

c,d:8bit位宽的无符号数

RTL 设计

`timescale 1ns/1ns

module function_mod(

input clk,

input rst_n,

input [3:0] a,

input [3:0] b,

output [3:0] c,

output [3:0] d

);

assign c = swtich(a);

assign d = swtich(b);

function [3:0] swtich;

input [3:0] x;

integer i;

begin

for (i=0;i<4;i=i+1) begin

swtich[i] = x[3-i];

end

end

endfunction

endmoduletestbench 设计

`timescale 1ns/1ns

module tb_function_mod();

reg clk;

reg rst_n;

reg [3:0] a;

reg [3:0] b;

wire [3:0] c;

wire [3:0] d;

initial begin

clk = 'd1;

rst_n <= 'd1;

#50

rst_n <= 'd0;

#200

$finish;

end

always #5 clk = ~clk;

always #10 a <= {$random} % 'd16;

always #10 b <= {$random} % 'd16;

function_mod inst_function_mod (

.clk(clk),

.rst_n(rst_n),

.a(a),

.b(b),

.c(c),

.d(d)

);

//verdi

initial begin

$fsdbDumpfile("tb_function_mod.fsdb");

$fsdbDumpvars(0);

end

endmodule仿真测试

仿真结果正常。