本文已收录到 GitHub · AndroidFamily,有 Android 进阶知识体系,欢迎 Star。技术和职场问题,请关注公众号 [彭旭锐] 进 Android 面试交流群。

前言

大家好,我是小彭。

在计算机组成原理中的众多概念中,开发者接触得最多的还是内存、硬盘、虚拟内存、CPU 缓存这些概念。这些概念有一个更为抽象的表示 —— 存储器,它是冯 · 诺依曼计算机体系中的五大组件之一,用于存储程序和数据。

在这个系列中,我将从存储器的金字塔结构展开,围绕 CPU 高速缓存、内存、硬盘、虚拟内存等内容逐步带你深入理解计算机中。

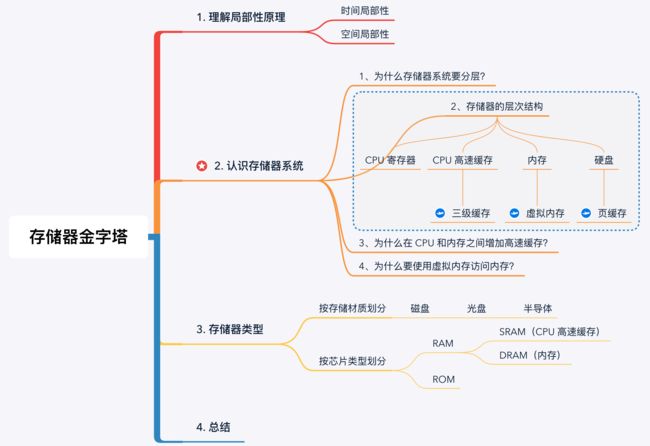

学习路线图:

1. 局部性原理

局部性原理是用于制定存储器系统数据管理策略的一个理论基础,我们可以分为 2 个维度来理解:

- 1、时间局部性(Temporal Locality): 时间局部性表示一个指令或数据被访问过后,在短时间内有很大概率会再次访问。例如,在程序中的一些函数、循环语句或者变量往往会在短时间内被多次调用;

- 2、空间局部性(Spatial Locality): 空间局部性表示一个指令或数据被访问过之后,与它相邻地址的数据有很大概率也会被访问。 例如,在程序中访问了数据的首项元素之后,往往也会访问继续后续的元素。

在计算机组成原理中,很多策略中都会体现到局部性原理,我们在学习中可以有意识地关联起来。例如在管理 CPU 高速缓存时,除了可以将当前正在访问的内存数据加到到缓存中,还可以把相邻内存的数据一并缓存起来(即 CPU 缓存行),也能够提高缓存命中率。

2. 认识存储器系统

2.1 为什么存储器系统要分层?

小伙伴们应该都知道内存和硬盘都是存储器设备。其实,在 CPU 内部中的寄存器和 CPU L1/L2/L3 缓存也同样是存储设备,而且它们的访问速度比内存和硬盘快几个数量级。那么,为什么要使用内存和硬盘,直接扩大 CPU 的存储能力不行吗?这就要提到存储器的 3 个主要的性能指标: 速度 + 容量 + 每位价格。

一般来说,存储器的容量越大则速度越低,速度越高则价格越高。想要获得一个同时满足容量大、速度高且价格低的 “神奇存储器” 是很难实现的。因此,现代计算机系统会采用分层架构,以满足整个系统在容量、速度和价格上最大的性价比。

2.2 存储器的层次结构

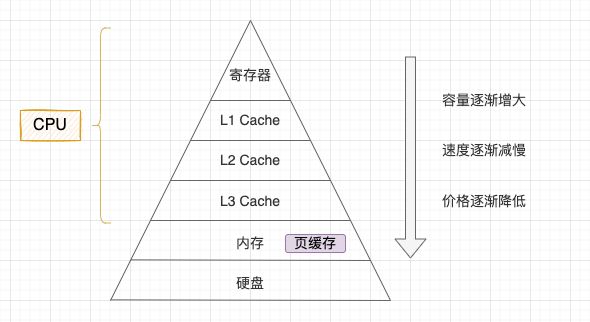

在现代计算机系统中,一般采用 “CPU 寄存器 - CPU 高速缓存 - 内存 - 硬盘” 四级存储器结构。自上而下容量逐渐增大,速度逐渐减慢,单位价格也逐渐降低。

- 1、CPU 寄存器: 存储 CPU 正在使用的数据或指令。寄存器是最靠近 CPU 控制器和运算器的存储器,它的速度最快;

- 2、CPU 高速缓存: 存储 CPU 近期要用到的数据和指令。CPU 高速缓存是位于 CPU 和内存中间的一层缓存。缓存和内存之间的数据调动是由硬件自动完成的,对上层是完全透明的。

- 3、内存: 存储正在运行或者将要运行的程序和数据;

- 4、硬盘: 存储暂时不使用或者不能直接使用的程序和数据。硬盘主要解决存储器系统容量不足的问题,硬盘的速度虽然比内存慢,但硬盘的容量可以比内存大很多,而且断电不丢失数据。

存储器金字塔

在此基础上,对各个层级上进行局部优化,就形成了完整的存储器系统:

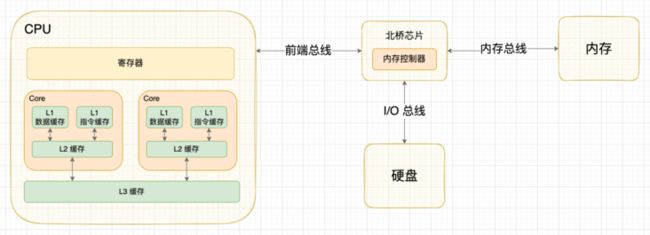

- 优化 1 - CPU 三级缓存: 在 CPU Cache 的概念刚出现时,CPU 和内存之间只有一个缓存,随着芯片集成密度的提高,现代的 CPU Cache 已经普遍采用 L1/L2/L3 多级缓存的结构来改善性能;

- 优化 2 - 虚拟内存: 程序不能直接访问物理地址,而是访问虚拟地址,虚拟地址需要经过地址变换(Address Translation)才能映射到存放数据的物理地址;

- 优化 3 - 页缓存: 为了提高读写效率和保护磁盘,操作系统在文件系统中使用了页缓存机制。

2.3 为什么在 CPU 和内存之间增加高速缓存?

我认为有 2 个原因:

- 原因 1 - 弥补 CPU 和内存的速度差(主要): 由于 CPU 和内存的速度差距太大,为了拉平两者的速度差,现代计算机会在两者之间插入一块速度比内存更快的高速缓存。只要将近期 CPU 要用的信息调入缓存,CPU 便可以直接从缓存中获取信息,从而提高访问速度;

- 原因 2 - 减少 CPU 与 I/O 设备争抢访存: 由于 CPU 和 I/O 设备会竞争同一条内存总线,有可能出现 CPU 等待 I/O 设备访存的情况。而如果 CPU 能直接从缓存中获取数据,就可以减少竞争,提高 CPU 的效率。

关于 CPU 三级高速缓存的更多内容,请关注专栏文章。

CPU 三级缓存

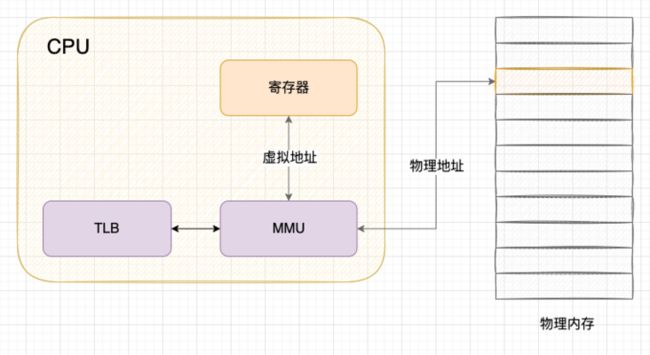

2.4 为什么要使用虚拟内存访问内存?

为了满足系统的多进程需求和大内存需求,操作系统在内存这一层级使用了虚拟内存管理。当物理内存资源不足时,操作系统会按照一定的算法将最近不常用的内存换出(Swap Out)到硬盘上,再把要访问数据从硬盘换入(Swap In)到物理内存上。 至于操作系统如何管理虚拟地址和内存地址之间的关系(段式、页式、段页式),对上层应用完全透明。

关于虚拟内存的更多内容,请关注专栏文章。

3. 存储器类型

这一节,我们来梳理常见的存储器类型。

3.1 按存储材质划分

- 1、磁表面存储器: 在金属或塑料表面涂抹一层磁性材料作为记录介质,用磁头在磁层上进行读写操作。例如磁盘、磁带、软盘等,已经逐渐淘汰。

- 2、光盘存储器: 在金属或塑料表面涂抹一层磁光材料作为记录介质,用激光在磁层上进行读写操作。例如 VCD、DVD 等,已经逐渐淘汰。

- 3、半导体存储器: 由半导体器件组成的存储器,现代的半导体存储器都会用超大规模集成电路技术将存储器制成芯片,具有体积小、功耗低、存取速度快的优点,是目前主流的存储器技术。

提示: 由于磁盘和光盘已经逐渐从历史中淡去,以后我们讨论的存储器都默认表示半导体存储器。

3.2 按芯片类型划分

半导体存储器按照存取方式划分可以分为 2 种:

- 1、RAM(Random-Access Memory 随机存取存储器): 指可以通过指令对任意存储单元进行读写访问的存储器,在断电后会丢失全部信息。RAM 的容量没有 ROM 大,但速度比 ROM 快很多,通常用作计算机主存。

- 2、ROM(Read-Only Memory 只读存储器): 指只能进行读取操作的存储器,断电后信息不丢失。随着半导体技术的发展,在 ROM 的基础上又发展出 EEPROM(电可擦除只读存储器)等技术,它们并不符合 ROM 只读的命名,但由于是在 ROM 上衍生的技术,才沿用了原来的叫法。现在我们更熟悉的 HDD(机械硬盘)和 SSD(固态硬盘) 都是 ROM 的衍生技术。

RAM 又分为 SRAM 和 DRAM 两种实现类型:

1、SRAM(静态 RAM): SRAM 只要在保持通电状态下,内部存储的数据就不会丢失,因此称为 “静态” RAM。

- 优点: 访问速度非常快,通常用作 CPU 的高速缓存;

- 缺点: 在 SRAM 中,仅实现 1 比特容量就需要 6~8 个晶体管组成,所以 SRAM 的存储密度不高。

6 个晶体管组成的 1 比特 SRAM

—— 图片引用自 Wikipedia

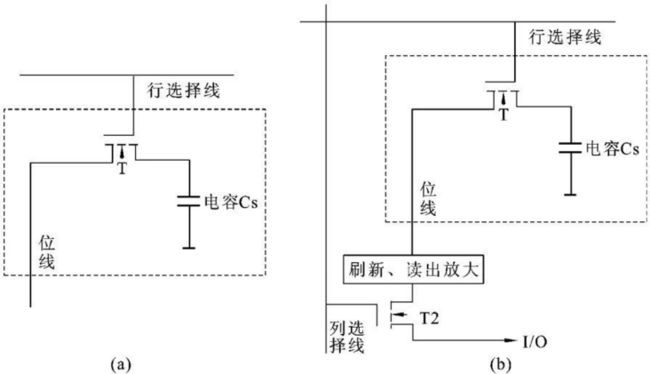

2、DRAM(动态 RAM): DRAM 在保持通电状态下,还需要定时刷新,才能保证内部存储的数据不会丢失,因此称为 “动态” RAM。

- 优点: 实现 1 比特容量只需要 1 个晶体管和 1 个电容组成,所以 DRAM 的存储密度、功耗和价格指标都比 SRAM 优秀的多;

- 缺点: 电容会自然放电,为避免某些长期得不到访问的存储单元丢失数据,必须采用定时刷新的策略。这就导致 DRAM 的数据访问电路和刷新电路都比 SRAM 更复杂,访问时延也更长,因此,DRAM 一般用作计算机主存。

1 个晶体管和 1 个电容组成的 1 比特 DRAM

—— 图片引用自 计算机组成原理教程

3.3 为什么内存的访问速度比 CPU 差这么多?

内存的访问速度受制于 DRAM 的性能瓶颈。

在目前的计算机系统中,计算机内存采用的是基于 DRAM (动态随机存取存储器)芯片的存储器,它的基本单元由一个晶体管 + 一个电容组成,在存储密度、功耗和价格等方面表现优秀。但电容会自然放电,需要定时刷新来保证信息不丢失,因此访问速度受损。而高速缓存是基于 SRAM (静态随机存取存储器)芯片的存储器,它的基本单元由 6~8 个晶体管组成。结构更简单,因此访问速度更快,但存储密度不高。

4. 总结

- 1、局部性原理是计算机存储器系统的基本原理,分为时间局部性和空间局部性;

- 2、现代计算机系统为了寻求容量、速度和价格上最大的性价比会采用分层架构,从 “CPU 寄存器 - CPU 高速缓存 - 内存 - 硬盘”自上而下容量逐渐增大,速度逐渐减慢,单位价格也逐渐降低;

- 3、为了弥补 CPU 和内存的速度差和减少 CPU 与 I/O 设备争抢访存,计算机在 CPU 和内存之间增加高速缓存,一般存在 L1/L2/L3 多级缓存的结构;

- 4、为了满足系统的多进程需求和大内存需求,操作系统在内存这一层级使用了虚拟内存管理;

- 5、内存的访问速度受制于 DRAM 的性能瓶颈。

今天,我们简单提到了 CPU 的三级缓存,下一篇文章我们详细展开讨论,敬请期待。

参考资料

- 深入浅出计算机组成原理(第 35 讲) —— 徐文浩 著,极客时间 出品

- 计算机组成原理教程(第 7 章) —— 尹艳辉 王海文 邢军 著

- 10分钟速成课 计算机科学 —— Carrie Anne 著

- principle of locality —— Wikipedia

- Static random-access memory —— Wikipedia

- Dynamic random-access memory —— Wikipedia