计算机组成原理实验2——ALU的设计

叠甲:本人三本985大二差生,什么都不会,文章都是自己的学习记录,没有任何参考价值,难免有不少错误,请大家轻点喷。

注:实验的quartus实现可联系我提供,实验报告中原理和实现过程已经很清晰,自己实现对学习更有帮助。

计算机组成原理实验二 ALU的设计

一、实验内容

(1)测试加减法器的功能。

(2)设计并实现具有加法、减法、逻辑与、逻辑非功能的8位ALU,算术运算影响结果标志ZF、CF、OF、SF,逻辑运算仅影响ZF标志,验证其正确性。

二、电路设计与实现

(提示:主要包括需求分析、模块划分、引脚组织,以及器件选择、信号命名及电路组成,注意描述分析与设计的过程)

- 加减法器

加减法器直接使用lpm_add_sub模块实现8位有符号加法

如图所示

- ALU

ALU中使用lpm_add_sub模块实现加减功能,lpm_and实现逻辑与功能,lpm_inv实现逻辑非功能。使用lpm_mux模块作为数据选择器

电路如图所示:

三、电路正确性验证

1、电路仿真

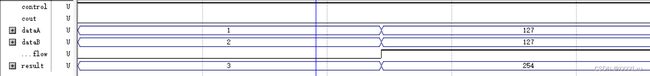

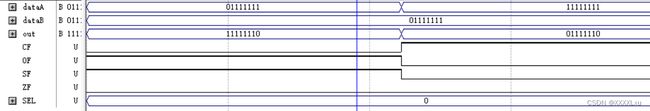

加减法器仿真:

- 加法

两组++

两组--

一组+-

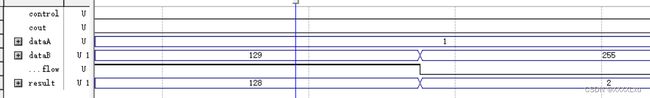

- 减法

两组+-

两组-+

一组++

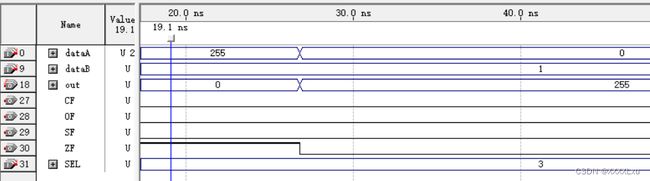

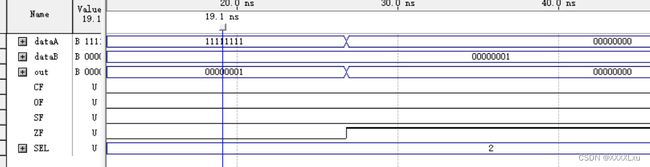

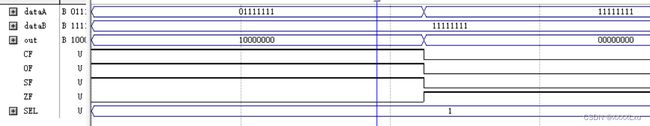

ALU仿真:

- 逻辑非功能

- 逻辑与功能

(3)加法功能

(4)减法功能

2、结果分析

(1)加减法器仿真

加法:

两组++:00000001+00000010=00000011.结果为00000011,符号位为0,结果正确;

01111111+01111111=11111110,符号位变为1,结果溢出,overflow为1

两组--:100000001+10000010=100000011,舍去进位为00000011,符号位为0,错误,overflow为1;

一组+-:加减法时符号位总是不会出错,因此overflow始终为0

减法:

两组+-:00000001-10000001=10000000,符号位为1,错误,overflow为1;

00000001-11111111=00000010,符号位为0,正确,overflow为0

两组-+:10000001-01111111=00000010,符号位为0,错误,overflow为1

10000001-00000001=10000000,符号位为1,正确,overflow为0

两组++;符号位不会溢出,overflow始终为0

(2)ALU仿真

逻辑非功能:逻辑非使得各个位置的0变为1,1变为0,故11111111变为00000000,00000000变为111111111

逻辑与功能:逻辑与使得各个位置上进行与运算,因此11111111与00000001运算结果为00000001,00000000与00000001的运算结果是00000000

对四个标志位的分析:

CF:CF的意义为进位/借位,

在加法中011111111+01111111=11111110,最高位未发生进位,CF为0;11111111+01111111最高位发生了进位,故CF为1;

在减法中01111111-11111111=10000000发生了借位,故CF为1;11111111-11111111=00000000,没发生借位,结果为0;

SF:代表着结果的符号位,

在加法中,011111111+01111111=11111110,符号位1;011111111+011111110=01111110的符号位0;

在减法中,01111111-11111111=10000000,符号位1;11111111-11111111=00000000,符号位0

OF:代表溢出的符号

加法运算中,011111111+01111111=11111110,两个正数相加,得到了负数,说明发生了溢出,故OF为1;111111111+01111111=01111110,符号位正确,说明未溢出,故OF为0

减法运算中,01111111-11111111=10000000,发生溢出,OF为1;11111111-11111111=00000000,不溢出,OF为0;

ZF:判断为0.在逻辑非中,11111111的非为00000000,为0,因此ZF=1;00000000的非不为0,因此ZF=0;

减法运算中,11111111-11111111为0,ZF为1;

四、实验小结

分工:(单人组)

设计总结:把ALU的每个功能所需的部件设计出来,逻辑非用lpm_inv,逻辑与用lpm_and,加减使用lpm_add_sub来实现,最后用选择器选择所需的结果

有待改进之处:走线比较乱

实验体会:选取合适的数据测试是很重要的,有时候设计图是有问题的,但只有少数的数据能找出问题,所以要注重测试