vhdl元件例化语句

在vhdl设计中常常将常用、典型的功能实体放在同一个目录下面,在设计复杂的电路的时候使用这些已经设计好的实例,这样就使设计变得简单了。

关键字:component

8位加法器,使用两个四位加法器实现。

四位加法器实现为adder4.vhd:

----------------------------------------------------------

-- 4 bits adder

----------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder4 is

port(

cin:in std_logic;

a:in std_logic_vector(3 downto 0);

b:in std_logic_vector(3 downto 0);

sum:out std_logic_vector(3 downto 0);

cout:out std_logic

);

end adder4;

architecture behav of adder4 is

signal sint:std_logic_vector(4 downto 0);

signal aa,bb:std_logic_vector(4 downto 0);

begin

--位连接--

aa<='0' & a(3 downto 0);

bb<='0' & b(3 downto 0);

sint<=aa+bb+cin;

sum(3 downto 0)<=sint(3 downto 0);

cout<=sint(4);

end behav;

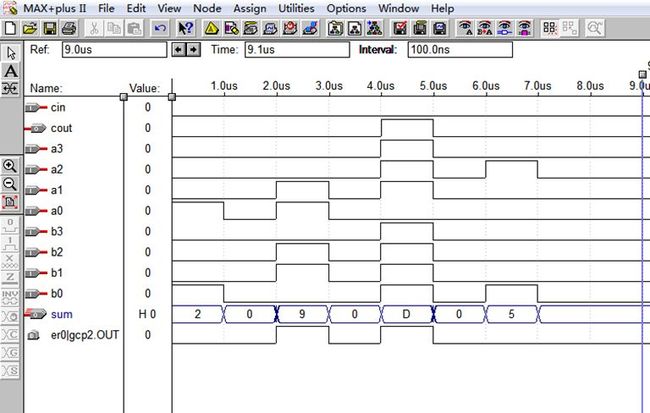

模拟仿真波形如下图所示,仿真了5个加法计算:

1+1

0+0

3+6

1110(B) +1111(B)= (1)1101(B)产生进位count=1

4+1

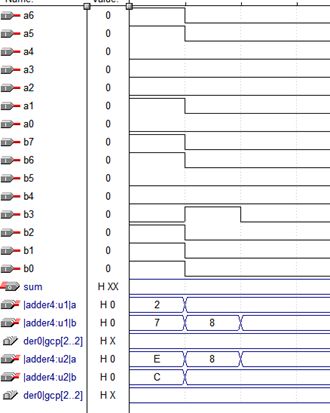

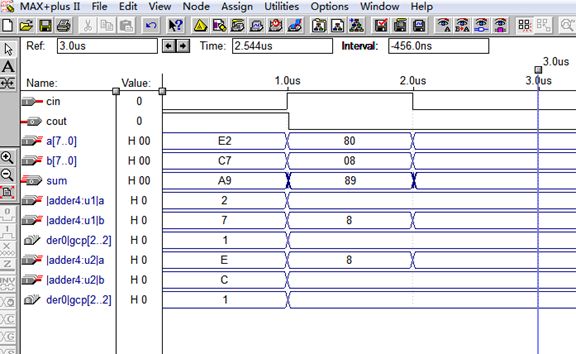

八位加法器实现为adder8.vhd

测试数据加法有两个:

----------------------------------------------------------

-- 4 bits adder

----------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder8 is

port(

cin:in std_logic;

a:in std_logic_vector(7 downto 0);

b:in std_logic_vector(7 downto 0);

sum:out std_logic_vector(7 downto 0);

cout:out std_logic

);

end adder8;

architecture behav of adder8 is

--添加组件和声明--

component adder4

port(

cin:in std_logic;

a:in std_logic_vector(3 downto 0);

b:in std_logic_vector(3 downto 0);

sum:out std_logic_vector(3 downto 0);

cout:out std_logic

);

end component;

signal carry_out:std_logic;

begin

u1:adder4 port map(cin=>cin,a=>a(3 downto 0),b=>b(3 downto 0),sum=>sum(3 downto 0),cout=>carry_out);

u2:adder4 port map(cin=>carry_out,a=>a(7 downto 4),b=>b(7 downto 4),sum=>sum(7 downto 4),cout=>cout);

end behav;

其一是0xe2 + 0xc7 = oxa9进一位cout=1

其二是0x80+0x08 +进位= 0x88有进位故为0x89

测试结果: