【正点原子FPGA连载】 第三章 硬件资源详解 摘自【正点原子】DFZU2EG/4EV MPSoC 之FPGA开发指南V1.0

1)实验平台:正点原子MPSoC开发板

2)平台购买地址:https://detail.tmall.com/item.htm?id=692450874670

3)全套实验源码+手册+视频下载地址: http://www.openedv.com/thread-340252-1-1.html

第三章 硬件资源详解

本章,我们将向大家详细介绍DFZU2EG/4EV MPSoC开发板各部分的硬件原理图,让大家对DFZU2EG/4EV MPSoC开发板的各部分硬件原理有个深入理解,并向大家介绍开发板的使用注意事项,为后面的学习做好准备。

本章包括以下几个部分:

12333.1DFZU2EG/4EV MPSoC开发板的IO分配

3.2DFZU2EG/4EV MPSoC开发板外设详解

3.3开发板使用注意事项

3.4MPSoC的学习方法

3.1DFZU2EG/4EV MPSoC开发板的IO分配

DFZU2EG/4EV MPSoC开发板的主控芯片为Zynq UltraScale+ MPSoC系列的xczu2eg-sfvc784-2和xczu4ev-sfvc784-1,总共有14个用户BANK(这里指有连接外设的BANK,不包BANK224)。这14个BANK中有6个属于PS端,8个属于PL端,不同的BANK上连接有不同的外设。下面我们就来一起看看这些BANK的原理图。

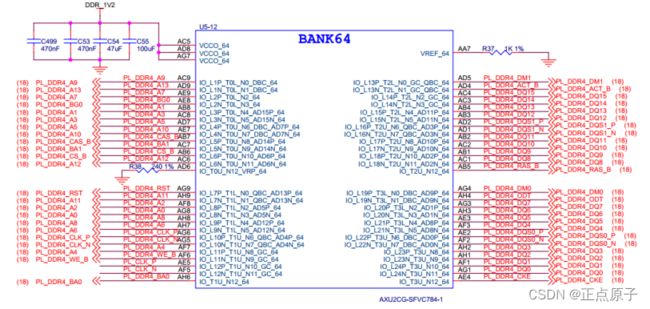

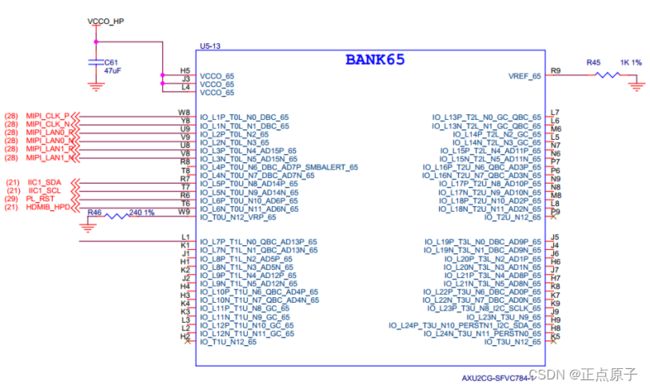

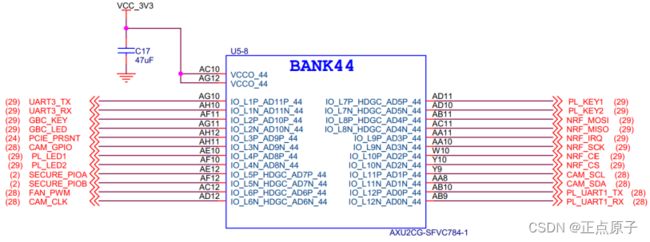

3.1.1PL端的IO分配

Zynq UltraScale+ MPSoC芯片的PL端和普通的FPGA一样,在DFZU2EG/4EV MPSoC开发板中PL端的IO被分成8组也就是8个BANK,同一个BANK中IO供电是相同的,不同的BANK之间供电电压可以不相同。在DFZU2EG/4EV MPSoC开发板中PL端BANK24、BANK44、BANK25以及BANK26都是3.3V电压供电,而BANK64、BANK65是1.2V供电,BANK0、BANK66是1.8V供电。之所以不同BANK之间的供电不同主要和它们连接的外设,即承担的功能有关,遵循的原则就是速度越快电压越低,例如BANK64连接的是DDR4芯片,需要处理高速的数据吞吐,因此它的供电电压较低,为1.2V。各个BANK的原理图如下所示:

图 3.1.8PL端的BANK0

从原理图中可以看出DFZU2EG/4EV MPSoC开发板的PL端引脚是非常多的,为了方便大家查找我们将例程用到的整理成了一张表格,如下表所示:

表 3.1.1 MPSoC PL端IO引脚分配总表

信号名 方向 管脚 端口说明

系统时钟(50Mhz)

sys_clk_p input AE5 系统时钟,频率:100Mhz

sys_clk_n input AF5

PL复位按键

sys_rst_n input AH11 PL复位,低电平有效

2个PL功能按键

key[0] input AD11 PL按键KEY0

key[1] input AD10 PL按键KEY1

3个PL_LED灯

led[0] output AE10 PL_LED0

led[1] output AF10 PL_LED1

UART串口

uart_rxd input AB9 串口接收端

uart_txd output AB10 串口发送端

IIC总线(EEPROM)

iic_scl output G11 IIC时钟信号线

iic_sda inout H12 IIC双向数据线

RGB TFT-LCD接口

lcd_hs output J11 RGB LCD行同步

lcd_vs output K12 RGB LCD场同步

lcd_de output J10 RGB LCD数据使能

lcd_bl output J12 RGB LCD背光控制

lcd_clk output K13 RGB LCD像素时钟

lcd_rst output F10 RGB LCD复位信号

lcd_rgb[0] output W14 RGB LCD蓝色(最低位)

lcd_rgb[1] output Y14 RGB LCD蓝色

lcd_rgb[2] output W13 RGB LCD蓝色

lcd_rgb[3] output Y13 RGB LCD蓝色

lcd_rgb[4] output W12 RGB LCD蓝色

lcd_rgb[5] output Y12 RGB LCD蓝色

lcd_rgb[6] output W11 RGB LCD蓝色

lcd_rgb[7] output AA12 RGB LCD蓝色(最高位)

lcd_rgb[8] output AC14 RGB LCD绿色(最低位)

lcd_rgb[9] output AD15 RGB LCD绿色

lcd_rgb[10] output AC13 RGB LCD绿色

lcd_rgb[11] output AD14 RGB LCD绿色

lcd_rgb[12] output AE15 RGB LCD绿色

lcd_rgb[13] output AA13 RGB LCD绿色

lcd_rgb[14] output AE14 RGB LCD绿色

lcd_rgb[15] output AB13 RGB LCD绿色(最高位)

lcd_rgb[16] output AG14 RGB LCD红色(最低位)

lcd_rgb[17] output AB15 RGB LCD红色

lcd_rgb[18] output AH14 RGB LCD红色

lcd_rgb[19] output AB14 RGB LCD红色

lcd_rgb[20] output AG13 RGB LCD红色

lcd_rgb[21] output AE13 RGB LCD红色

lcd_rgb[22] output AH13 RGB LCD红色

lcd_rgb[23] output AF13 RGB LCD红色(最高位)

lcd_scl output F10 触摸屏IIC接口的时钟

lcd_sda inout F12 触摸屏IIC接口的数据

ct_rst output H11 触摸屏的复位t_cs

ct_int input F12 触摸屏的中断 t_pen

HDMI接口

tmds_data_p[0] output G1 HDMI的DATA0通道的P端

tmds_data_p[1] output F2 HDMI的DATA1通道的P端

tmds_data_p[2] output G3 HDMI的DATA2通道的P端

tmds_clk_p output E1 HDMI的CLK通道的P端

tmds_scl output G5 HDMI的SCL信号

tmds_sda output F5 HDMI的SDA信号

tmds_hpd input T6 HDMI的热插拔信号

摄像头接口(双目OV5640摄像头1)

cam_pwdn output B15 OV5640电源休眠控制信号

cam_rst_n output F13 cmos 复位信号,低电平有效

cam_vsync input G14 cmos 场同步信号

cam_href input G13 cmos 行同步信号

cam_pclk input C13 cmos 数据像素时钟

cam_data[0] input E15 cmos 数据

cam_data[1] input D15 cmos 数据

cam_data[2] input E14 cmos 数据

cam_data[3] input D14 cmos 数据

cam_data[4] input E13 cmos 数据

cam_data[5] input B13 cmos 数据

cam_data[6] input C14 cmos 数据

cam_data[7] input A13 cmos 数据

cam_scl output H13 cmos SCCB时钟信号线

cam_sda inout F15 cmos SCCB双向数据线

摄像头接口(双目OV5640摄像头2)

cam_pwdn output B14 OV5640电源休眠控制信号

cam_rst_n output A11 cmos 复位信号,低电平有效

cam_vsync input A15 cmos 场同步信号

cam_href input A12 cmos 行同步信号

cam_pclk input D11 cmos 数据像素时钟

cam_data[0] input C12 cmos 数据

cam_data[1] input C11 cmos 数据

cam_data[2] input B11 cmos 数据

cam_data[3] input B10 cmos 数据

cam_data[4] input A10 cmos 数据

cam_data[5] input E10 cmos 数据

cam_data[6] input E12 cmos 数据

cam_data[7] input D10 cmos 数据

cam_scl output A14 cmos SCCB时钟信号线

cam_sda inout D12 cmos SCCB双向数据线

PL端以太网RGMII接口

eth_rx_clk input E5 RGMII接收数据时钟

eth_rx_ctl input D5 RGMII输入数据有效信号

eth_rxd[0] input G6 RGMII输入数据RXD[0]

eth_rxd[1] input F6 RGMII输入数据RXD[1]

eth_rxd[2] input G8 RGMII输入数据RXD[2]

eth_rxd[3] input F7 RGMII输入数据RXD[3]

eth_tx_clk input D6 RGMII发送数据时钟

eth_tx_ctl output F8 RGMII输出数据有效信号

eth_txd[0] output D7 RGMII输出数据TXD[0]

eth_txd[1] output E8 RGMII输出数据TXD[1]

eth_txd[2] output E9 RGMII输出数据TXD[2]

eth_txd[3] output D9 RGMII输出数据TXD[3]

eth_mdc output E7 以太网管理接口的时钟

eth_mdio inout C7 以太网管理接口的双向数据

DDR4接口

c0_ddr4_odt[0] output AH4 DDR4 终端电阻使能

c0_ddr4_bg[0] output AE8 DDR4 Bank组地址

c0_ddr4_adr[16] output AB5 DDR4地址线

c0_ddr4_adr[15] output AB7 DDR4地址线

c0_ddr4_adr[14] output AF6 DDR4地址线

c0_ddr4_adr[13] output AD9 DDR4地址线

c0_ddr4_adr[12] output AC6 DDR4地址线

c0_ddr4_adr[11] output AH9 DDR9地址线

c0_ddr4_adr[10] output AE7 DDR4地址线

c0_ddr4_adr[9] output AC9 DDR4地址线

c0_ddr4_adr[8] output AH8 DDR4地址线

c0_ddr4_adr[7] output AE9 DDR4地址线

c0_ddr4_adr[6] output AH7 DDR4地址线

c0_ddr4_adr[5] output AD7 DDR4地址线

c0_ddr4_adr[4] output AF7 DDR4地址线

c0_ddr4_adr[3] output AC8 DDR4地址线

c0_ddr4_adr[2] output AF8 DDR4地址线

c0_ddr4_adr[1] output AB8 DDR4地址线

c0_ddr4_adr[0] output AG8 DDR4地址线

c0_ddr4_dqs_t[1] inout AD2 DDR4数据选取脉冲

c0_ddr4_dqs_c[1] inout AD1 DDR5数据选取脉冲

c0_ddr4_dqs_t[0] inout AE2 DDR6数据选取脉冲

c0_ddr4_dqs_c[0] inout AF2 DDR7数据选取脉冲

c0_ddr4_dq[15] inout AC4 DDR4数据

c0_ddr4_dq[14] inout AC3 DDR4数据

c0_ddr4_dq[13] inout AB4 DDR4数据

c0_ddr4_dq[12] inout AB3 DDR4数据

c0_ddr4_dq[11] inout AB2 DDR4数据

c0_ddr4_dq[10] inout AC2 DDR4数据

c0_ddr4_dq[9] inout AB1 DDR4数据

c0_ddr4_dq[8] inout AC1 DDR4数据

c0_ddr4_dq[7] inout AG3 DDR4数据

c0_ddr4_dq[6] inout AH3 DDR4数据

c0_ddr4_dq[5] inout AE3 DDR4数据

c0_ddr4_dq[4] inout AF3 DDR4数据

c0_ddr4_dq[3] inout AH2 DDR4数据

c0_ddr4_dq[2] inout AH1 DDR4数据

c0_ddr4_dq[1] inout AF1 DDR4数据

c0_ddr4_dq[0] inout AG1 DDR4数据

c0_ddr4_cs_n[0] output AB6 DDR4 片选信号

c0_ddr4_ck_t[0] output AG6 DDR4 差分时钟正

c0_ddr4_ck_c[0] output AG5 DDR4 差分时钟负

c0_ddr4_cke[0] output AE4 DDR4 时钟使能信号

c0_ddr4_reset_n output AG9 DDR4 复位信号

c0_ddr4_act_n output AD4 DDR4 写操作响应信号

c0_ddr4_ba[1] output AC7 DDR4 Bank地址

c0_ddr4_ba[0] output AH6 DDR4 Bank地址

c0_ddr4_dm_dbi_n[1] output AD5 DDR4 数据掩码

c0_ddr4_dm_dbi_n[0] output AG4 DDR4 数据掩码

在上表中,表格中列出来了除扩展口外,开发板上所有的PL IO引脚,扩展口上的引脚IO可以参考开发板的原理图或者直接查看开发板上的丝印标注。

另外在资料盘(A盘)→3_正点原子DFZU2EG/4EV MPSoC开发板原理图文件夹下,有提供Excel格式的管脚分配表格,表格里共两个工作表,一个是“PL IO引脚列表”,另一个是“PS IO引脚列表”,方便大家查看。

3.1.2PS端的IO分配

PS端一共包含了6个IO BANK,如下图所示:

图 3.1.9 PS端的BANK500& BANK501

& BANK502

图 3.1.10 PS端的BANK503

图 3.1.12 PS端的BANK505

与PL端IO BANK不同的是,PS端的IO连接是是相对固定的,用户不能够像PL引脚那样,将PS端的IO随意分配到某个外设。PS端外设的IO口与MIO(多路复用IO)之间,具有固定关系的映射,某个外设的IO口可能会映射到不同的MIO上,某个MIO也有可能会具有多个外设的IO口映射到其上面。两者之间的映射如下图所示:

图 3.1.13 PS端IO映射图

为了方便大家去查找IO,PS端和PL端一样也做了一张例程IO分配表,如下所示:

表 3.1.2 MPSoCZYNQ PS端IO引脚分配总表

信号名 管脚 端口说明

2个PS功能按键

ps_key1 MIO40 PS按键KEY1

ps_key2 MIO41 PS按键KEY2

2个PS_LED灯

ps_led1 MIO38 PS_LED1

ps_led2 MIO39 PS_LED2

QSPI FLASH0

QSPI0_SS MIO5 QSPI0 FLASH的片选,低电平有效

QSPI0_SCLK MIO0 QSPI0 FLASH的时钟

QSPI0_IO0 MIO4 QSPI0 FLASH的数据位0

QSPI0_IO1 MIO1 QSPI0 FLASH的数据位1

QSPI0_IO2 MIO2 QSPI0 FLASH的数据位2

QSPI0_IO3 MIO3 QSPI0 FLASH的数据位3

QSPI FLASH1

QSPI1_SS MIO7 QSPI1 FLASH的片选,低电平有效

QSPI1_SCLK MIO12 QSPI1 FLASH的时钟

QSPI1_IO0 MIO8 QSPI1 FLASH的数据位0

QSPI1_IO1 MIO9 QSPI1 FLASH的数据位1

QSPI1_IO2 MIO10 QSPI1 FLASH的数据位2

QSPI1_IO3 MIO11 QSPI1 FLASH的数据位3

PS UART

PS_UART1_RX MIO42 PS UART的接收

PS_UART1_TX MIO43 PS UART的发送

PS DP接口

DP_HPD MIO28 DP接口 热插拔引脚

DP_OE MIO29 DP接口 数据使能

DP_AUX_IN MIO30 DP接口 数据输入

DP_AUX_OUT MIO27 DP接口 数据输出

PS IIC

PS_IIC1_SCL MIO32 IIC时钟

PS_IIC1_SDA MIO33 IIC数据

PS 以太网

ETH_TXCK MIO64 PS以太网RGMII接口的TX_CLK

ETH_TXD0 MIO65 PS以太网RGMII接口的TX_D0

ETH_TXD1 MIO66 PS以太网RGMII接口的TX_D1

ETH_TXD2 MIO67 PS以太网RGMII接口的TX_D2

ETH_TXD3 MIO68 PS以太网RGMII接口的TX_D3

ETH_TXCTL MIO69 PS以太网RGMII接口的TX_CTL

ETH_RXCK MIO70 PS以太网RGMII接口的RX_CLK

ETH_RXD0 MIO71 PS以太网RGMII接口的RX_D0

ETH_RXD1 MIO72 PS以太网RGMII接口的RX_D1

ETH_RXD2 MIO73 PS以太网RGMII接口的RX_D2

ETH_RXD3 MIO74 PS以太网RGMII接口的RX_D3

ETH_RXCTL MIO75 PS以太网RGMII接口的RX_CTL

ETH_MDC MIO76 PS以太网MDIO接口的时钟

ETH_MDIO MIO77 PS以太网MDIO接口的数据

PS USB接口

USB_DIR MIO53 USB总线方向控制

USB_STP MIO58 数据传输的结束信号

USB_NXT MIO55 当前数据接收完成指示信号

USB_CLK MIO52 PHY的时钟输出

USB_DATA7 MIO63 双向数据总线位7

USB_DATA6 MIO62 双向数据总线位6

USB_DATA5 MIO61 双向数据总线位5

USB_DATA4 MIO60 双向数据总线位4

USB_DATA3 MIO59 双向数据总线位3

USB_DATA2 MIO54 双向数据总线位2

USB_DATA1 MIO57 双向数据总线位1

USB_DATA0 MIO56 双向数据总线位0

SD卡

SD_CLK MIO51 SD卡的时钟信号

SD_CMD MIO50 SD卡的命令信号

SD_CD MIO45 SD卡的插拔检测信号

SD_D0 MIO46 SD卡的DATA0

SD_D1 MIO47 SD卡的DATA1

SD_D2 MIO48 SD卡的DATA2

SD_D3 MIO49 SD卡的DATA3

eMMC存储器

eMMC_CCLK MIO22 eMMC的时钟信号

eMMC_RSTN MIO23 eMMC的复位信号

eMMC_CMD MIO21 eMMC的命令信号

eMMC_D0 MIO13 eMMC的DATA0

eMMC_D1 MIO14 eMMC的DATA1

eMMC_D2 MIO15 eMMC的DATA2

eMMC_D3 MIO16 eMMC的DATA3

eMMC_D4 MIO17 eMMC的DATA4

eMMC_D5 MIO18 eMMC的DATA5

eMMC_D6 MIO19 eMMC的DATA6

eMMC_D7 MIO20 eMMC的DATA7

3.2开发板原理图详解

3.2.1开发板电源

开发板电源的拓扑结构如下图所示:

图 3.2.1 电源拓扑图

整个板子的电源来自电源适配器的12V供电电压,分别经过两片降压芯片(型号为JW5068A)之后,一片输出5V电压VBTN,再经过电源开关后输出VCC5V电压给系统供电。一片输出0.85V电压VCC_PSINTLP给FPGA芯片供电。

这里要特别提醒一下大家,很多同学可能会有误解明明板子上已经有一种电压了例如1.8V,为什么后面还要再转个1.8V出来,而且同一种电压还会有好几个名称,这主要是因为有很多器件是有上电顺序的,不可以同时上电,虽然工作电压都相等,但是上电顺序有先后要求,所以我们就通过一定的电路设计让整个板子上的器件有一个先后的上电顺序,这就是为什么同一种电压转换了多次或者好几个名字,主要是每个名字代表的电压产生的顺序不同。

电源适配器供电的电源接口原理图如下图所示:

![]()

图 3.2.2 电源适配器供电接口

外部直流+12V电源从电源接口输入,其中D12是防反接二极管,避免外部直流电源极性接反的时候,烧坏开发板。

![]()

图 3.2.3输入电压转换电路

上图电路的作用是将外部输入的+12V电压经过降压芯片转换为5V电源VBTN输出。

DFZU2EG/4EV开发板板的供电电源是电源适配器,经过电源开关SW8控制是否对开发板供电,其原理图如下图所示:

图 3.2.4电源按键开关

VBTN为电源适配器输入的12V电压经电源降压芯片转换后得到的电压,VUSB为通过USB接口输入的电压。上图中的F2保险丝开发板没有连接的,所以VUSB未连接到电源开关按键,所以开发板不能通过USB接口供电。

直接使用VUSB 5V供电的外设有PS与PL端USB Type-C接口,VUSB 5V电压还经过电压转换芯片(XC6206P332)输出3.3V的电压给CH340串口芯片供电。电路图如下图所示:

图 3.2.5 USB串口电压示意图

直接使用VCC5V供电的开发板外设有HDMI接口、USB HUB芯片、ATK_Module接口、RBG_LCD接口、扩展口等。VCC5V电压还经过各种电压转化芯片给FPGA供电和各种板载外设供电。

VCC5V电压经过电压转换芯片(JW5060)输出1.8V的电压VCCAUX,电路如下图所示,转化的VCCAUX电压不仅给FPGA的BANK0、BANK66、FPGA POWER2供电,还给开发板的扩展口供电。

图 3.2.6电压转化电路

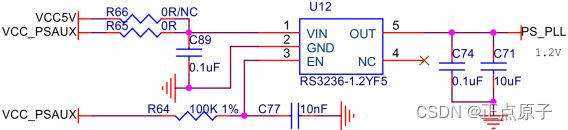

VCC5V电压还经过电压转换芯片(RS3236-1.2YF5)输出1.2V的电压PS_PLL,电路如下图所示,转化的PS_PLL电压给FPGA POWER1供电。

图 3.2.7电压转化电路

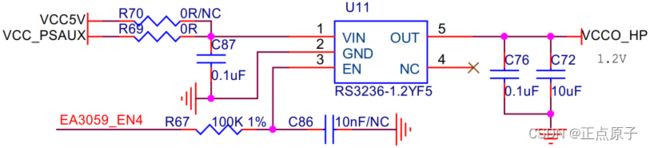

VCC5V电压还经过电压转换芯片(RS3236-1.2YF5)输出1.2V的电压VCCO_HP,电路如下图所示,转化的VCCO_HP电压给BANK65供电。

图 3.2.8电压转化电路

VCC5V电压还经过电压转换芯片(RS3236-1.8YF5)输出1.8V的电压PS_AVTT,电路如下图所示,转化的PS_AVTT电压给FPGA POWER1供电。

图 3.2.9电压转化电路

VCC5V电压还经过电压转换芯片(RS3236-ADJ8)输出0.9V的电压PS_AVCC,电路如下图所示,转化的PS_AVCC电压给FPGA POWER1供电。

图 3.2.10电压转化电路

VCC5V电压还经过电压转换芯片(SPX3819M5-2-5)输出2.5V的电压DDR_2V5,电路如下图所示,转化的DDR_2V5电压给DDR4供电。

图 3.2.11电压转化电路

VCC5V电压还经过电压转换芯片(SGM2028-ADJ)输出3.3V的电压DP_3V3,电路如下图所示,转化的DP_3V3电压给Mini_DP接口供电。

图 3.2.12电压转化电路

VCC5V电压还经过电压转换芯片(SPX3819M5-3-3)输出3.3V的电压VCCIO,电路如下图所示,转化的VCCIO电压给BANK25、BANK26供电。

图 3.2.13电压转化电路

VCC5V电压还经过两片电压转换芯片(AIC1519N-0)输出5V的电压USB_PORT14_5V,电路如下图所示,转化的USB_PORT14_5V电压给4个USB3.0 Host接口供电。

图 3.2.14电压转化电路

DC-DC芯片EA3059负责将VCC5V电压转换为0.9V、1.2V、1.8V、3.3V,供电电路如下图所示:

图 3.2.15 EA3059供电电路

从上图可以看到,EA3059芯片的功能还是很强大的,单个芯片就可以转换出四种不同的电压,这里我们需要注意它输出的四路电压顺序是1.8V>1.2V>3.3V>0.9V,这是怎么做到的呢?主要靠芯片的使能来控制(EN1~EN4),我们可以看到电压VCC_PSAUX的使能EN3是通过RC电路连接VCC5V电源,电压DDR_1V2的使能EN2是PS_AVTT电压启动后才能正常使能成功,由图 3.2.18 PS端上电启动顺序官方描述可知电压VCC_PSAUX的上电顺序是在PS_AVTT电压之前,所以VCC_PSAUX>PS_AVTT>DDR_1V2。所以EN3使能的1.8V比EN2使能的1.2V早;EN4是通过RC电路连接到EN2的,EN4需要先把电容给充电充满才能激活,所以EN2使能的1.2V要比EN4使能的3.3V早;EN1是通过RC电路连接到了3.3V,因此0.9V是晚于3.3V生效,所以启动顺序1.8V>1.2V>3.3V>0.9V。对应到原理图启动顺序就是VCC_PSAUX>DDR_1V2>VCC_3V3>PL_VCU_0V9。

EA3059芯片转化出的1.8V电压主要给BANK500、PS_QSPI、PS_eMMC、BANK502、PS_USB3320供电;EA3059芯片转化出的1.2V电压主要给BANK504、DDR4、BANK64供电;EA3059芯片转化出的3.3V电压主要给时钟振荡器、BANK24、BANK44、EEPROM、BANK501、BANK503、PS_eMMC、LVDS发送器、mini_DP接口、PS端网口、PL端网口、PCIe x1接口、JTAG接口、XADC接口、MIPI接口、TF_SD卡接口、PS按键、启动MODE模式选择、POWER LED、无线模块接口、FPGA DONE LED、风扇接口、PL按键、PL复位按键、扩展口、PS复位按键供电;EA3059芯片转化出的0.9V电压主要给FPGA的视频编解码单元的专用电源引脚(4EV开发板仅有)供电。

整个供电系统设计如下图所示:

图 3.2.16 DFZU2EG/4EV开发板供电系统原理图

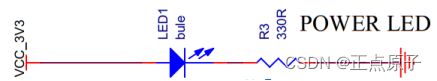

开发板上还具有一个电源指示灯,其原理图如下图所示:

图 3.2.17 开发板电源指示灯

它连接到了3.3V电源上,可以通过开发板的电源指示灯来判断开发板供电是否正常。

另外,由于Zynq UltraScale+ MPSoC芯片的供电有上电顺序的要求,所以这些电源的产生顺序必须符合ZYNQ的上电顺序要求,在Xilinx官方手册DS925(Zynq UltraScale+ MPSoC Data Sheet:DC and AC Switching Characteristics)中,有对ZU2EG和ZU4EV芯片的上电要求有详细的描述,Zynq UltraScale+ MPSoC PS上电顺序如下图所示:

图 3.2.18 PS端上电启动顺序官方描述

由上图可知,PS端在全功率域(FPD)可以工作之前,低功率域(LPD)必须工作。

为了实现最小电流消耗并确保I/O在通电时处于三态,列出了低功率域(LPD)的建议通电顺序。同时建议关机顺序与开机顺序相反。

1.VCC_PSINTLP

2.VCC_PSAUX、VCC_PSADC和VCC_PSPLL以任何顺序或同时进行。

3.VCCO_PSIO

为了实现最小电流消耗并确保I/O在通电时处于三态,列出了全功率域(FPD)的建议通电顺序。同时建议关机顺序与开机顺序相反。

1.由同一电源驱动的VCC_PSINTFP和VCC_PSINTFP_DDR。

2.VPS_MGTRAVCC和VCC_PSDDR_PLL以任何顺序或同时进行。

3.VPS_MGTRAVTT和VCCO_PSDDR以任何顺序或同时进行。

官方推荐的PS端低功率域(LPD)上电顺序为:VCC_PSINTLP→VCC_PSAUX、VCC_PSADC和VCC_PSPLL→VCCO_PSIO。

官方推荐的PS端全功率域(FPD)上电顺序为:VCC_PSINTFP和VCC_PISNTFP_DDR→VPS_MGTRAVCC和VCC_PSDDR_PLL→VPS_MGTRAVTT和VCCO_PSDDR。

Zynq UltraScale+ MPSoC芯片的PS需要多组电源。如下表所示:

表 3.2.1 Zynq UltraScale+ MPSoC PS的电源

PS端低功率域(LPD) VCC_PSINTLP PS低功率域电源电压

VCC_PSAUX PS辅助电路提供电压

VCC_PSADC PS模数转换器电源电压

VCC_PSPLL PS PLL(DPLL,RPLL,APLL,VPLL,IOPLL)供电电压

VCCO_PSIO PS I/O电源电压

PS端全功率域(FPD) VCC_PSINTFP PS全功率域电源电压

VCC_PSINTFP_DDR PS DDR全功率域电源电压

VPS_MGTRAVCC PS-GTR收发器的接收机和发射机内部电路的模拟电源引脚

VCC_PSDDR_PLL PS DDR PLL供电电压

VPS_MGTRAVTT PS-GTR发射机和接收机终端电路的模拟电源引脚

VCCO_PSDDR PS DDR控制器I/O供电电压。

所以从上面官方文档可知我们开发板PS端的供电顺序是VCC_PSINTLP→VCC_PSAUX→PS_PLL(VCC_PSPLL)与PS_AVCC(VPS_MGTRAVCC)→PS_AVTT(VPS_MGTRAVTT)。

图 3.2.19 DDR_1V2的电源使能电路

由上面电路可知VCC5V与PS_AVTT工作后才能使能DDR_1V2开始工作。

图 3.2.20 VCCAUX的电源使能电路

由上面电路可知VCC5V与PL_VCU_0V9工作后才能使能VCCAUX开始工作。

结合上面EA3059芯片输出电压的启动顺序VCC_PSAUX>DDR_1V2>VCC_3V3>PL_VCU_0V9,开发板的上电顺序为DCIN_12V→VCC_PSINTLP→VCC_PSAUX→PS_PLL(VCC_PSPLL)与PS_AVCC(VPS_MGTRAVCC)→PS_AVTT(VPS_MGTRAVTT)→DDR_1V2→VCC_3V3→PL_VCU_0V9→VCCAUX。

图 3.2.21VCC_HP电压电路

从上面的电路图可以看出VCC_HP电压的工作使能信号与VCC_3V电压一样都是EN4,所以VCC_HP与VCC_3V同时启动。开发板的上电顺序为DCIN_12V→VCC_PSINTLP→VCC_PSAUX→PS_PLL(VCC_PSPLL)与PS_AVCC(VPS_MGTRAVCC)→PS_AVTT(VPS_MGTRAVTT)→DDR_1V2→VCC_3V3与VCC_HP→PL_VCU_0V9→VCCAUX。

Zynq UltraScale+ MPSoC PL上电顺序如下图所示:

图 3.2.22 PL端上电启动顺序官方描述

官方的PL端建议的通电顺序为VCCINT、VCCINT_IO/VCCBRAM、VCCINT_VCU、VCCAUX/VCCAUX_IO和VCCO,这个通电顺序是为了实现最小电流消耗并确保I/O在通电时处于三态,并且建议关机顺序与开机顺序相反。

如果VCCINT和VCCINT_IO/VCCBRAM具有相同的电压电平,则它们可以由相同的电源同时供电,VCCINT_IO必须连接到VCCBRAM。如果VCCAUX/VCCAUX_IO和VCCO具有相同的电压电平,则两者可以由相同的电源同时供电,VCCAUX和VCCAUX_IO必须连接在一起。

VCCADC和VREF可随时通电,无需加电排序要求。

GTH或GTY收发器实现最小电流消耗的推荐通电顺序为VCCINT、VMGTAVCC、VMGTAVTT或VMGTAVC、VCCINT和VMGTAVTT。没有对VMGTVCCAUX进行上电顺序的建议。VMGTAVCC和VCCINT可以同时启动。并且建议断电顺序与通电顺序相反,来实现最小电流消耗。

如果不符合这些建议的顺序,在通电和断电期间,VMGTAVTT的电流可能会高于规定值进而影响芯片的正常使用。

PS和PL电源完全独立,所有PS电源均可在任何PL电源之前或之后通电。PS和PL电源区是被隔离的以防止相互影响损坏。

Zynq UltraScale+ MPSoC芯片的PL需要多组电源。如下表所示:

表 3.2.2 Zynq UltraScale+ MPSoC PL的电源

PL VCCINT PL内部逻辑的电源引脚

VCCINT_IO I/O Bank的电源引脚。VCCINT_IO必须连接到板上的VCCBRAM。

VCCBRAM PL BRAM逻辑电源引脚

VCCINT_VCU 视频编解码单元的电源引脚(仅适用EV系列系芯片)。

VCCAUX 辅助电路用电源引脚

VCCAUX_IO I/O组的辅助电源引脚,VCCAUX_IO必须连接到板上的VCCAUX

VCCO 输出驱动的电源引脚(每个Bank)

开发板的所有引脚(包括开发板的电源引脚)详细说明可以详细阅读Xlinx官方文档UG1075《Zynq UltraScale+ Device Packaging and Pinouts》产品规格用户指南。

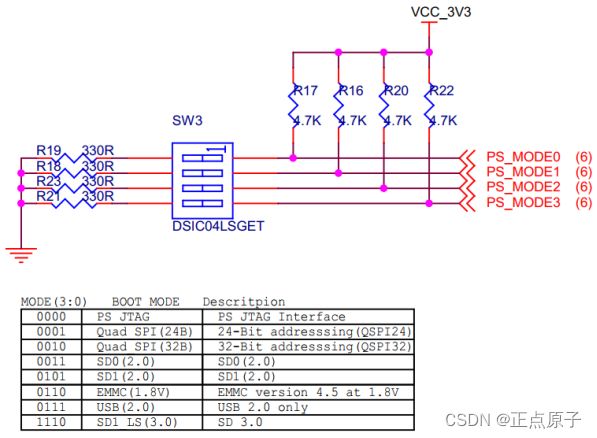

3.2.2DFZU2EG/4EV MPSoC开发板启动模式

DFZU2EG/4EV MPSoC开发板支持8种启动模式,我们常用的启动模式是JTAG启动、FLASH启动以及SD卡启动,此外还支持eMMC启动以及USB启动。具体的启动方式选择可以通过拨动拨码开关去控制,拨码开关拨动的值和对应的启动模式,在原理图中以表格的形式给大家列举出来了。其原理图如下所示:

图 3.2.23 拨码开关控制启动模式

3.2.3PL端千兆以太网

DFZU2EG/4EV MPSoC开发板板载了一个以太网PHY芯片,型号为YT8521。与PS端自带的以太网MAC层硬核逻辑不同的是,用户可以使用PL端的逻辑资源来实现一个以太网MAC层软逻辑,可以通过编写Verilog代码来实现。此外,用户还可以通过EMIO来将PL端的RGMII接口耦合到PS端的以太网MAC层硬核逻辑。

PL端的PHY芯片与MPSoC PL的连接框图如下图所示:

图 3.2.24 PL端千兆以太网PHY芯片连接框图

其原理图如下图所示:

图 3.2.25 PL端千兆以太网接口

YT8521芯片支持10/100/1000Mbps网络传输速率,通过RGMII接口跟MPSoC PL端的IO进行数据通信,并支持通过MDIO总线进行PHY寄存器的管理。

开发板上还为PL端的PHY芯片板载了一个自带网络变压器的RJ45插座(ATK91131A),它们能够满足高带宽通信的需求,比如,可以使用网线连接到电脑,来与电脑上位机进行通信。

RGMII接口时序图如下图所示:

图 3.2.26 RGMII接口时序图

YT8521芯片支持10/100/1000Mbps网络传输速率,由通信双方所能达到的最高通信速率决定。当以太网PHY芯片通信速率为1000Mbps时,以太网接口时钟频率为125Mhz,数据在时钟的上升沿和下降样被采样;当以太网PHY芯片通信速率为100Mbps时,以太网接口时钟频率为25Mhz,数据在时钟的上升沿被采样;当以太网PHY芯片通信速率为10Mbps时,以太网接口时钟频率为2.5Mhz,数据在时钟的上升沿被采样。

3.2.4PS端千兆以太网

DFZU2EG/4EV MPSoC开发板板载一颗PS端千兆以太网PHY(物理)芯片,型号为YT8521,实现了10/100/1000M以太网物理层功能。该PHY芯片的差分引脚连接到了板载的RJ45接口上,能够满足高带宽通信的需求。

YT8521连接到了PS端的BANK 502上面,PHY和MPSoC芯片的连接框图如下图所示:

图 3.2.27 PS端千兆以太网PHY芯片连接框图

其原理图如下图所示:

图 3.2.28 PS端千兆以太网PHY

YT8521芯片支持10/100/1000Mbps网络传输速率,通过RGMII接口跟MPSoC PS系统的MAC层进行数据通信,并支持通过MDIO总线进行PHY寄存器的管理。除此之外,YT8521上电会检测一些特定IO引脚的电平状态,从而确定自己的工作模式,用于配置芯片的工作状态。

3.2.5USB3.0接口

DFZU2EG/4EV MPSoC开发板板载4个USB3.0 Host接口,原理图如下所示(一共四个接口,这里只贴出其中一个接口原理图):

图 3.2.29 USB3.0 Host接口

从上图中可以看出USB3.0 Host接口一共有9根线,每根线的作用如下表所示(不包含SHIELD1和SHIELD2,这两个不属于USB3.0的接口引脚):

表 3.2.3 USB3.0接口引脚功能表

从上表中我们可以很清晰的看到USB3.0接口是兼容USB2.0的,其中DN、DP以及GND三根线就是用来完成USB2.0半双工数据传输的。而剩下的SSTXN、SSTXP、SSRXN以及SSRXP用来完成USB3.0的全双工数据传输。

DFZU2EG/4EV MPSoC开发板的四个USB3.0接口既可以执行USB2.0协议也可以执行USB3.0协议,并且这两种协议的数据信号上都接有ESD保护芯片,ESD保护芯片的作用就是保护差分数据通道不会被瞬时电压或者外部静电干扰甚至损毁。ESD保护芯片原理图如下所示:

图 3.2.31 USB2.0 ESD保护

在这里还要提醒大家一下,MPSoC上的USB3.0接口5V供电有一个双高端电源开关(Dual USB High-Side Power Switch),它会将一个5V电源转成两个5V电源,原理图如下所示:

图 3.2.32 双高端电源开关

3.2.6USB HUB芯片

DFZU2EG/4EV MPSoC开发板虽然板载了4路USB3.0 Host接口,但是这四路接口并不是全部直接连接到MPSoC主控芯片上,而是先连接到USB HUB芯片,然后再连接到主控芯片上的,这样可以大大节省MPSoC主控芯片的引脚资源,USB HUB芯片的原理图如下所示:

图 3.2.33 USB HUB芯片

从上图中可以看到这块USB HUB芯片是既支持USB2.0协议,也支持USB3.0协议,其中芯片左边的USB_TXP_UP、USB_TXN_UP、USB_RXP_UP和USB_RXN_UP对应USB3.0的数据线;USB_DP0和USB_DM0对应USB2.0的数据线。USB3.0的数据线是直接连接到MPSoC的主控芯片上,USB2.0数据线连接到USB3320芯片上,而右边对应的会将这一对USB3.0(收发双通道)和一对USB2.0(单通道)数据线转换成四对差分线连接到USB座子上。

USB3320芯片的原理图如下图所示:

图 3.2.34 USB3320芯片原理图

USB3320是PS端的USB2.0收发器芯片,USB2.0收发器采用的是一个1.8V的,高速且支持ULPI标准接口的USB3320C芯片,实现高速的USB2.0 Host模式的数据通信。

3.2.7MINI DP接口

DFZU2EG/4EV MPSoC开发板板载一个MINI DP接口,原理图如下所示:

图 3.2.35 MINI DP接口

关于MINI DP接口直接看上图的原理图不太容易理解,我把接口的引脚定义分为三类给大家用示意图的方式展现,如下图所示:

图 3.2.36 DP示意图

从上图中可以看到我们将DP接口的引脚分成了三类,第一类是数据引脚(Main_Link),这类引脚对应原理图中的ML_LANE0_P、ML_LANE0_N、ML_LANE1_P、ML_LANE1_N、ML_LANE2_P、ML_LANE2_N、ML_LANE3_P以及ML_LANE3_N。这四对差分数据通道用来传输视频音频数据,四对信号通道可以一起使用,也可以像我们DFZU2EG/4EV MPSoC开发板这样只使用两对数据通道,甚至只使用一对通道都是可以的。当然不同的通道数量会影响数据传输速度,并且单个通道的传输速率有1.62Gbps、2.7Gbps、5.4Gbps以及8.1Gbps四种,多个通道同时工作的情况下,所有通道必须使用同一种传输速率。

除了数据通道外,剩下的就是AUX和HPD通道了,AUX通道对应原理图中的AUX_CH_P和AUX_CH_N,这一对差分通道的功能主要是实现链路管理和设备控制;而HPD通道对应原理图中的HOTPLUG_DETECT,这个通道是由接收端发出的单向中断信号。当接收端设备拉低HPD信号,信号脉冲宽度在0.25ms~2ms之间,此时发送端会在HPD信号上升沿后的100ms以内重新读取接收端设备信息。如果HPD信号拉低时间超过2ms(例如DP数据线被拔掉了,断开连接),发送设备就会停止发送数据,等待接收设备重新连接上。

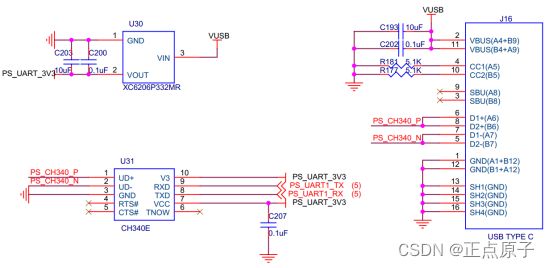

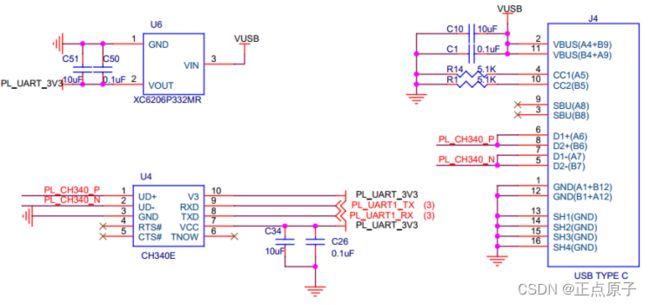

3.2.8PS端串口

DFZU2EG/4EV MPSoC开发板板载一个USB-UART串口通信接口,原理图如下所示:

图 3.2.37 PS端串口

USB转串口芯片,我们选择的是CH340,是国内芯片公司南京沁恒的产品,稳定性经测试还不错,所以我们还是要支持下国产。

USB Type C是一个Type C座,提供CH340和电脑通信的接口,VUSB就是来自电脑USB的电源。图中U30(XC6206P332MR)将输入的5V电压转成3.3V,此处之所以用单独的3.3V给CH340供电,是为了当开发板断电后,电脑仍然能够识别到开发板的串口COM号。

3.2.9PL端串口

DFZU2EG/4EV MPSoC开发板还搭载了一个PL端的UART串口,原理图如下所示:

图 3.2.38 PL端串口

PL端的串口在硬件原理上与PS端一致,此处不再赘述。

3.2.10XADC接口

DFZU2EG/4EV MPSoC开发板板载一个XADC接口,用于测量外部输入的模拟电压,范围为 0~1V。MPSoC芯片内部的System Monitors既可以测量MPSoC芯片内部的温度和电压,也可以用来测量外部的模拟电压。其原理图如下图所示:

图 3.2.39 XADC接口

板上的XADC接口(J20)用于测量外部输入的模拟电压。其中,输入端的R352、R353、C492组成抗混叠滤波器,用来移除输入信号中的高频谐波部分,防止高频谐波超过采样频率的一半。

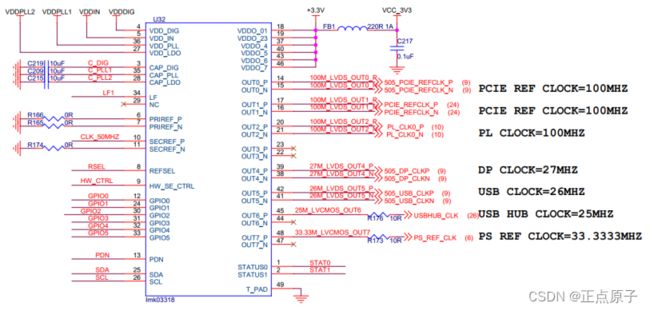

3.2.11时钟振荡器

由于DFZU2EG/4EV MPSoC开发板上面的外设需要多种不同频率的时钟信号来驱动,而全部使用晶振是比较麻烦的,因此我们在板子上搭载了一个时钟振荡器芯片(lmk03318),他可以产生多种不同频率的时钟,原理图如下所示:

图 3.2.41 50Mhz晶振

DFZU2EG/4EV MPSoC开发板板载一个时钟振荡器芯片(lmk03318),这块芯片本身需要外接一个50Mhz的晶振(X1),然后将这50Mhz的时钟转换成8路时钟给其他外设使用。其中第一路是100Mhz 505_PCIE REF CLOCK差分时钟,连接到BANK505,驱动MPSoC内部PCIe资源;第二路时钟是100Mhz PCIe REF CLOCK差分时钟,连接到PCIe的插座上;第三路是PL CLOCK 100Mhz差分时钟,连接到BANK64作为MPSoC芯片PL端的全局时钟;第四路时钟未输出;第五路是27Mhz的DP差分时钟,连接到BANK505,驱动MPSoC内部DP资源;第六路是26Mhz USB CLOCK差分时钟,连接到BANK505,驱动MPSoC内部USB资源;第七路是25Mhz USB HUB CLOCK连接到USB HUB芯片(GL3523),用来驱动USB HUB芯片;第八路是33.3333Mhz PS REF CLK连接到BANK503,驱动MPSoC内部处理器。

图 3.2.42 24Mhz晶振

开发板还板载一个24Mhz晶振产生 USBPHY _CLK0时钟,连接到USB2.0驱动芯片(USB3320),用来驱动USB3320芯片。

3.2.12J19扩展口

DFZU2EG/4EV MPSoC开发板板载一个J19扩展口,如下图所示:

图 3.2.43 J19扩展口

J19扩展口,是一个40Pin 3.3V的外设扩展口,除去电源和地还剩36个可用IO,方便我们去外接一些外设模块。例如双目摄像头、高速ADDA模块等等。

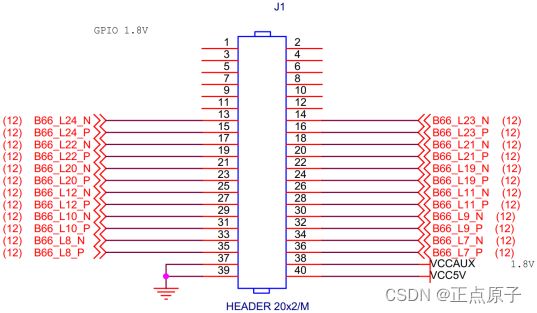

3.2.13J1扩展口

DFZU2EG/4EV MPSoC开发板还板载一个J1扩展口,如下图所示:

图 3.2.44 J1扩展口

J1扩展口跟J19扩展口最大的区别就是引脚电压不一样,J1扩展口的电压是1.8V,其次J1扩展口的可用IO为24个(出去电源、地和NC),方便大家去连接1.8V的外设。

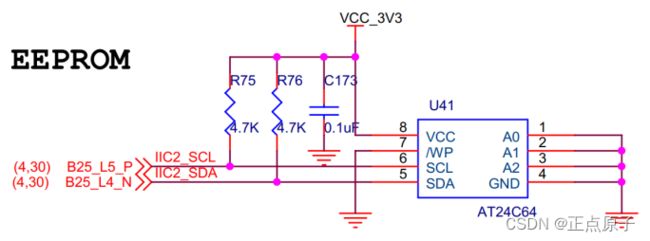

3.2.14EEPROM

EEPROM (Electrically Erasable Progammable Read Only Memory,E2PROM)即电可擦除可编程只读存储器,是一种常用的非易失性存储器(掉电数据不丢失),也常在嵌入式领域中作为数据的存储设备,在物联网及可穿戴设备等需要存储少量数据的场景中也有广泛应用。

DFZU2EG/4EV MPSoC开发板板载的EEPROM是Atmel公司的AT24C64,使用I2C接口进行通信,该芯片的容量为64Kb,对于一般应用来说是足够了。驱动该E2PROM只需要用到两个IO,其与MPSoC和EEPROM之间的连接框图如下图所示:

图 3.2.45 EEPROM连接框图

其电路原理图如下图所示:

图 3.2.46 EEPROM

硬件原理图里我们把A0~A2均接地,对AT24C64来说也就是把地址位设置成了0了,写代码的时候要注意这点。另外AT24C64采用IIC协议进行数据的读写,而IIC的串行时钟线SCL和数据线SDA均是开漏的,所以需要接上拉电阻。

3.2.15PCIe接口

DFZU2EG/4EV MPSoC开发板板载一个PCIe x1接口(母口),原理图如下所示:

图 3.2.47 PCIe接口

PCIe的通信速度很高,因此在设计硬件的时候一定要确保其电源纹波比较稳定,大家从图中可以看到,给PCIe座子供电的12V、3.3V电压都并联了三个电容,其目的就是滤除电源毛刺。并且在3.3V的电压上还接了一个肖特基二级管,可以对反向电压进行整流进一步提高电源稳定性同时还起到一定的保护电路的作用。

3.2.16PS端4片DDR4

DFZU2EG/4EV MPSoC开发板PS端板载了4片DDR4芯片,其原理图如下所示(这里只给出其中一片的原理图):

图 3.2.48 PS端DDR4

需要注意的是,DDR4的供电电压是1.2V,并且由于DDR4的通信速度很高,所以DDR4的电源纹波要求比较稳定,因此上图中电压全部接了电容作滤波处理。另外,DDR4由于速度高且是双倍速率采样,所以硬件设计时需要严格考虑信号完整性,开发板在原理图设计、PCB布线和PCB加工时候就充分考虑了匹配电阻/终端电阻,走线阻抗控制,走线等长控制,保证DDR4的高速稳定的工作。

四片DDR4的地址引脚和控制引脚是并联接到MPSoC主控芯片的IO上的,相当于将4片DDR4合成了一个大的DDR4其容量和数据位宽都扩大了4倍,我们使用MPSoC芯片内部的DDR4硬核控制器可以同时控制这4片DDR4。连接示意图如下所示:

从上图中我们就可以清晰的看到,四片DDR4的控制线和地址线是连接到一起的,相当于引脚的复用,而数据线是分开的,每片DDR4的数据线都有自己独立的MPSoC IO与之相连。

3.2.17PL端1片DDR4

DFZU2EG/4EV MPSoC开发板一共板载了5片DDR4,其中有4片都在PS端,并且可以使用DDR4物理硬核去调用这四片DDR4。除了PS端的4片DDR4之外,在PL端也有一片DDR4,其原理图如下所示:

图 3.2.49 PL端DDR4

PL端和PS端DDR4在硬件设计上是一样的,只不过PL端的DDR4没有专门的物理硬核来操控它,但是大家也不用担心,PL端的DDR4可以通过MIG软核来操控。MIG软核内实现了DDR4的各种驱动时序,例如初始化时序、读写指令时序等等,将这些时序封装成一个IP核并且留出了用户端口,我们只需要调用这个IP核就可以和DDR4进行通信。

3.2.18eMMC

eMMC是非易失性NAND存储器,俗称电子硬盘,开发板板载的eMMC芯片型号为KLM8G1GETF,存储容量为8GB,能够满足PS端大容量非易失性的存储需求,如存储ARM的应用程序、系统文件以及其它的用户数据文件。

MPSoC与eMMC之间的连接框图如下图所示:

图 3.2.50 eMMC芯片连接框图

eMMC连接到MPSoC芯片PS部分的BANK500 MIO口上,其原理图如下图所示:

图 3.2.51 eMMC芯片原理图

3.2.19风扇接口

MPSoC在工作的时候会产生大量的热量,因此在开发板上预留了一个散热扇的接口如下图所示:

![]()

图 3.2.52 散热扇接口

从上图中可以看到,散热扇的电源由12V提供,并且通过肖特基二级管与AO3400 MOS场效应管组成了一个开关电路,开关控制端FAN_PWM连接到MPSoC的IO上用来控制风扇的开启和关闭。

3.2.20PL端按键

DFZU2EG/4EV MPSoC开发板上PL端板载两个功能按键,如下图所示:

图 3.2.53 PL端按键

图中“PL_KEY1”和“PL_KEY2”为PL端的功能按键输入。它们都外接上拉电阻,未按下时按键端口输出高电平,按下时输出低电平。按键作为最简单的输入设备,适合在需要给系统输入控制信号的场合使用。

3.2.21PS端按键

DFZU2EG/4EV MPSoC开发板上PS端板载两个功能按键,如下图所示:

图 3.2.54 PS端按键

图中“PS_KEY1”和“PS_KEY2”为PS端的功能按键输入。它们都外接上拉电阻,未按下时按键端口输出高电平,按下时输出低电平。按键作为最简单的输入设备,适合在需要给系统输入控制信号的场合使用。

3.2.22PL端LED

DFZU2EG/4EV MPSoC开发板PL端板载两个LED,在调试代码的时候,使用LED来指示程序执行状态,是一个很好的辅助调试方法。其电路原理图如下图所示:

图 3.2.55 PL端LED

从上图中可以看出LED是阴极接地,阳极连接MPSoC主控芯片的IO,所以高电平点亮LED,低电平熄灭LED。

3.2.23PS端LED

DFZU2EG/4EV MPSoC开发板PS端板载两个功能LED,如下图所示:

图 3.2.56 PS端LED

从上图中可以看出LED是阴极接地,阳极连接MPSoC主控芯片的IO,所以高电平点亮LED,低电平熄灭LED。

3.2.24MIPI CSI接口

开发板板载了一个MIPI CSI接口,用于连接MIPI摄像头,接口原理图如下图所示:

图 3.2.57 MIPI接口原理图

MIPI CSI接口的差分信号(MIPI_LAN0_P/N、MIPI_LAN1_P/N、MIPI_LAN2_P/N、MIPI_LAN3_P/N和MIPI_CLK_P/N)连接至BANK65的HP IO上,其IO电平为1.2V;而MIPI接口的CAM_PWDN、CAM_CLK、CAM_RST连接至BANK66的IO上,其IO电平为1.8V,CAM_PWDN是摄像头的控制信号,CAM_CLK是作为摄像头的驱动时钟,CAM_RST是作为摄像头的复位信号。

3.2.25PL配置完成指示灯

开发板板载一颗PL配置完成指示灯,连接到了PL端的配置完成(DONE)信号,在PL端配置(下载程序)完成之后,该LED灯会被点亮。其原理图如下图所示:

图 3.2.58 PL配置完成指示灯

从上图中可以看出,LED是阴极接地,阳极连接MPSoC主控芯片的FPGA_DONE IO和3.3V电压,当FPGA PL端没有配置完成的时候,FPGA_DONE IO保持低电平,此时LED灯不亮;当FPGA PL端配置完成,FPGA_DONE IO会拉高此时LED亮(绿色)。

3.2.26电源指示灯

开发板板载一颗POWER指示灯,用于指示开发板的通电状态,其原理图如下图所示:

图 3.2.59 电源指示灯

电源指示灯很简单直接连接到3.3V电压上,当板子上电成功,电源指示灯就会亮起(蓝色)。

3.2.27HDMI接口

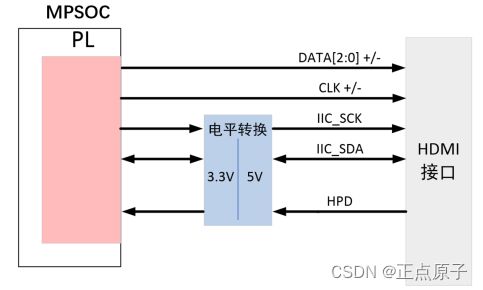

DFZU2EG/4EV MPSoC开发板板载高清晰度多媒体接口HDMI(High Definition Multimedia Interface,HDMI)接口,可以连接显示器用来实现图片和视频的显示。DFZU2EG/4EV MPSoC开发板通过PL侧的差分IO直接连接到HDMI接口的差分信号和时钟,通过FPGA逻辑实现TMDS信号的差分转并行和编解码,实现数字视频输入和输出的传输解决方案,最高支持1080P的输出功能。

其与MPSoC之间的连接框图如下图所示:

图 3.2.60 HDMI连接框图

当开发板作为HDMI主设备时,HDMI接口外接显示设备,HPD(hot plug detect)热插拔信号作为输入。开发板在作为HDMI主设备时,需要提供给HDMI显示设备一个+5V的电源。另外HMDI主设备会通过IIC总线来读取HDMI显示设备的设备信息。

其电路原理图如下所示:

图 3.2.61 HDMI接口

需要说明的是,HDMI的IIC引脚是5V电平的,需要将其转换为PL端所需的3.3V电压。电平转换电路如下图所示:

图 3.2.62 HDMI的IIC电平转换电路

其中,IIC3_SCL和IIC3_SDA连接到MPSoC PL侧的IO口上,HDMIB_SCL_LS和HDMIB_SDA_LS连接到HDMI插座上。

当总线空闲即IIC3_SCL和IIC3_SDA都被MPSoC驱动为高电平时,MOS管截止,HDMIB_SCL_LS和HDMIB_SDA_LS也被上拉电阻R179和R182上拉到+5V的高电平。

当IIC3_SCL或IIC3_SDA被MPSoC驱动为低电平时,MOS管导通,此时HDMIB_SCL_LS或HDMIB_SDA_LS也被下拉到了GND。

若HDMIB_SDA_LS需要向MPSoC发送低电平时,HDMIB_SDA_LS为低,MOS管内部二极管导通IIC1_SDA被下拉到了低电平。以此实现了双向电平转换的功能。

3.2.28WIRELESS接口

DFZU2EG/4EV MPSoC开发板板载一个WIRELESS接口,原理图如下:

图 3.2.63 WIRELESS接口

WIRELESS接口其实就是一个扩展口,它可以连接正点原子NRF24L01无线模块,实现远程无线射频通信。

3.2.29ATK-MODULE

DFZU2EG/4EV MPSoC开发板板载了一个ATK模块接口,电路原理图如下图所示:

图 3.2.64 ATK 模块接口

如图所示,J8是一个1*6的排母座,可以用来连接正点原子开发的“ATK-USB-UART模块”或者其他ATK接口的外设模块,比如:蓝牙串口模块、GPS模块、MPU6050模块等。当连接“ATK-USB-UART模块”,则实现UART串口通信功能。

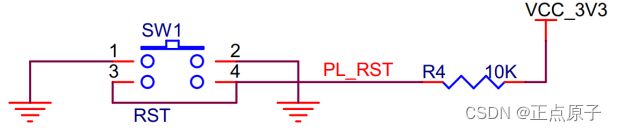

3.2.30PL端复位

DFZU2EG/4EV MPSoC开发板PL端板载一个复位按键可以对整个PL端进行复位操作,如下图所示:

图 3.2.65 PL端复位按键

复位按键一端接地一端上拉,并且上拉的那一端还连接到了MPSoC PL端的复位IO上,因此复位按键在没有按下时保持高电平,按下则低电平,所以PL端的复位是低电平有效。

3.2.31PS端复位

DFZU2EG/4EV MPSoC开发板PS端同样板载一个复位按键,如下图所示:

图 3.2.66 PS端复位按键

PS端的复位按键比较特殊,它不是直接连接到FPGA的IO上,而是连接到了电源芯片上,当我们按下复位按键时,会通过断电的方式给MPSoC进行复位。

3.2.32TF卡接口

DFZU2EG/4EV MPSoC开发板板载了一个Micro SD(TF)卡接口。Micro SD卡一般用于存储MPSoC芯片的BOOT程序,Linux操作系统内核, 文件系统以及其它的用户数据文件。

其电路原理图如下图所示:

图 3.2.67 Micro SD接口

SD卡的引脚都是直接连接到MPSoC芯片的MIO上的,然后通过MPSoC内部的SD控制器硬核去操控,需要注意的是,上图中的SD_CD信号用于Micro Card的热插拔检测,当插上Micro Card时,CD信号会被拉低。

3.2.33QSPI FLASH

开发板板载一颗QSPI Flash芯片,型号为W25Q256,存储容量为256Mbit(32M字节),采用QSPI协议和FPGA进行通信。QSPI Flash可用于存储MPSoC芯片的启动镜像数据,包括PS端的程序镜像和PL端的配置镜像,以保证MPSoC在重新上电后仍能继续工作。

原理图如下所示:

图 3.2.68 QSPI FLASH芯片原理图

需要说明的是,开发板预留了两个FLASH接口,但我们实际上只使用了一片Flash(只焊接了一片)。

3.2.34RGB888 TFT-LCD

TFT-LCD是一种液晶显示屏,它采用薄膜晶体管(TFT)技术提升图像质量,如提高图像亮度和对比度等。相比于传统的CRT显示器,TFT-LCD有着轻薄、功耗低、无辐射、图像质量好等诸多优点,因此广泛应用于电视机、电脑显示器、手机等各种显示设备中。DFZU2EG/4EV MPSoC开发板板载的RGB LCD模块接口(FPC接口)电路如下图所示:

图 3.2.69 RGB LCD 模块接口

图中,RGBLCD是RGB LCD液晶接口,采用RGB888数据格式,最大支持256256256=1677W色颜色显示,并支持触摸屏(支持电阻屏和电容屏)。该接口仅支持RGB接口的液晶(不支持MCU接口的液晶),目前正点原子的RGB接口LCD模块有:4.3寸(ID:4384 , 800480)、7寸(ID:7084, 800480、ID:7016,1024*600)和10寸(ID:1018)等尺寸可选。

图中的T_MISO/IIC2_SDA/T_PEN/T_CS/ IIC2_SCL用于实现对液晶触摸屏的控制(支持电阻屏和电容屏),连接到MPSoC PL端的IO的触摸屏的4个信号如图中的T_PEN、T_CS、IIC2_SCL、IIC2_SDA所示,它们也可以使用PS端的EMIO来连接到PS系统。LCD_BL用于控制LCD的背光,LCD_BL为1表示打开背光。

3.3开发板使用注意事项

为了让大家更好的使用DFZU2EG/4EV MPSoC开发板,我们在这里总结该开发板使用的时候尤其要注意的一些问题,希望大家在使用的时候多多注意,以减少不必要的问题。

1.当你想使用某个IO口用作其他用处的时候,请先看看开发板的原理图,该IO口是否有连接在开发板的某个外设上,如果有,该外设的这个信号是否会对你的使用造成干扰,先确定无干扰,再使用这个IO。

2.开发板上的拨码开关需要拨到对应的模式才能启动开发板,如果模式和启动方式不对应会造成代码下载失败或者板子启动不起来。

3.当液晶显示白屏的时候,请先检查液晶模块是否插好(拔下来重新插试试),如果还不行,可以通过串口看看LCD ID是否正常,再做进一步的分析。

至此,本手册的实验平台MPSoC FPGA的硬件部分就介绍完了,了解了整个硬件对我们后面的学习会有很大帮助,有助于后面的管脚约束(分配),在编写程序的时候,可以事半功倍,希望大家细读!另外正点原子开发板的其他资料及教程更新,都可以在技术论坛 下载到,大家可以经常去这个论坛获取更新的信息。

3.4MPSoC的学习方法

MPSoC作为目前热门的SOC类处理器,正在被越来越多的公司选择使用。学习MPSoC的朋友也越来越多,初学者可能会认为MPSoC很难学,以前只学过51,或者甚至连51都没学过的,一看到MPSoC就懵了。其实,万事开头难,只要掌握了方法,学好MPSoC,还是非常简单的,这里我们总结学习MPSoC的几个要点:

1.一款实用的开发板。

这个是实验的基础,有时候软件仿真通过了,在板上并不一定能跑起来,而且有个开发板在手,什么东西都可以直观的看到,效果不是仿真能比的。但开发板不宜多,多了的话连自己都不知道该学哪个了,觉得这个也还可以,那个也不错,那就这个学半天,那个学半天,结果学个四不像。倒不如从一而终,学完一个再学另外一个。

2.掌握方法,勤学慎思。

MPSoC不是妖魔鬼怪,不要畏难,基本方法就是:

a)了解MPSoC的基本结构。

学习MPSoC之前需要先对MPSoC基本结构和其功能有个大概的了解,如PS、AXI总线、锁相环PLL、FIFO等。需要知道PLL是用来产生不同频率的时钟,如使用HDMI时需要生成75MHz的时钟;FIFO用于数据的缓存和异步时钟域数据的传递等。

b)了解Verilog HDL基本语法

没有软件的硬件就如同行尸走肉一般。软件是硬件的灵魂,硬件是软件的舞台。好的软件设计才能发挥硬件的性能,而软件的精髓在于代码。学习FPGA也是这样,Verilog HDL做为一种硬件描述语言,是对数字电路的一种描述,而数字电路是并行工作的,因而在编写Verilog HDL时要有并行的思想,不同于软件设计语言,软件设计语言是由CPU统一进行处理,一条指令一条指令的串行运行,所以软件设计语言是基于串行的设计思想,因而在写Verilog HDL代码的时候要注意这种差别。另外对于Verilog HDL的基本语法是务必要掌握的,如一般常用的module/endmodule、input/output/inout、wire/reg、begin/end、posedge/negedge、always/assign、if/else、case/default/endcase/parameter/localparam等关键字要清楚它们的作用和区别。掌握了Verilog HDL的基本语法和Verilog HDL的并行设计思想后,会觉得Verilog HDL和C语言一样简单。

c)MPSoC PS的学习

学习MPSoC PS首先要了解C语言的基本语法。然后了解PS端基本的系统框架和外设,例如PS端架构、片内互连、AXI总线、DDR控制器等等。最关键的是PS端的C程序。软件系统可以被认为是建立于基于硬件的系统上的一个栈,或者说是一系列层,从底至上依次是基础硬件系统(来自Vivado的自定义硬件)、板级支持包、Operating System、软件应用。

初学者可以多看看官方的文档和资料,对于PS端的软件,xilinx提供了丰富的库函数,很多时候用户直接调用调用即可,读者要学会利用这些库函数。遇到问题时,读者可以借助xilinx的SDK开发环境中的各种调试功能来定位错误,以帮助解决问题。

3.多思考,多动手。

所谓熟能生巧,先要熟,才能巧。如何熟悉?这就要靠大家自己动手,多多练习了,光看或说是没什么太多用的。只有在使用MPSoC的过程中,才会一点点的熟悉,也只有动手实练,才能对FPGA有切实的感受。

熟悉了之后,就应该进一步思考,也就是所谓的巧了。我们提供了几十个例程,供大家学习,跟着例程走,无非就是熟悉MPSoC的过程,只有进一步思考,才能更好的掌握MPSoC,也即所谓的举一反三。例程是死的,人是活的,所以,可以在例程的基础上,自由发挥,实现更多的其他功能,并总结规律,为以后的学习和使用打下坚实的基础,如此,方能信手拈来。

所以,学习一定要自己动手,光看视频,光看文档,是不行的。举个简单的例子,你看视频,教你如何煮饭,几分钟估计你就觉得学会了。实际上你可以自己测试下,是否真能煮好?机会总是留给有准备的人,只有平时多做准备,才可能抓住机会。

只要以上三点做好了,学习MPSoC基本上就不会有什么太大问题了。如果遇到问题,可以在我们的技术论坛:开源电子网:www.openedv.com/forum.php提问,论坛FPGA板块有各种主题,很多疑问已经有网友提过了,所以可以在论坛先搜索一下,很多时候,就可以直接找到答案了。论坛是一个分享交流的好地方,是一个可以让大家互相学习,互相提高的平台,所以有时间,可以多上去看看。