Synchronize asynchronous signals

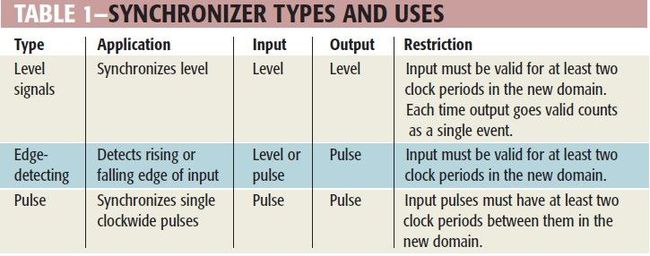

Level signals:

Edge-detecting

Pulse

Rules:

1.One important rule when synchronizing signals is that a design should not synchronize the same signal in more than one place; that is, a single signal fans out to more than one synchronizer. Because synchronization takes one to two clock cycles, a designer cannot reliably predict when each of these signals arrives across a clock domain.

2.In addition, the timing of a group of synchronized signals in the new clock domain can vary because the delay can be either a single clock cycle of delay or two cycles, depending on when the input arrives at the synchronizer.

3.For synchronization to work properly, the signal crossing a clock domain should pass from flip-flop in the original clock domain to the first flip-flop of the synchronizer without passing through any combinational logic between the two (Figure 1). This requirement is important because the first stage of a synchronizer is sensitive to glitches that combination logic produces. A long enough glitch that occurs at the correct time could meet the setup-and-hold requirements of the first flip-flop in the synchronizer, leading the synchronizer to pass a false-valid indication to the rest of the logic in the new clock domain.

Reference: Mike Stein, Paradigm Works "Crossing the abyss: asynchronous signals in a synchronous world"