Verilog基本语法之模块以及模块调用详解(2)

模块结构

一、模块结构组成

模块由三个元素组成,分别是模块起始、接口说明、逻辑功能描述

1. 模块起始:每个模块都要进行端口定义,格式为:module 模块名(端口1, 端口2, 端口3),

2. I/O接口说明:input输出,output输出,inoutput双向接口

3. 逻辑功能描述:always、assign等功能描述。

二、模块详解

组合成为完整程序如下:

module <模块名> (<端口列表>)

<I/O接口说明>

<内部信号声明>

<逻辑功能定义>

Endmodule

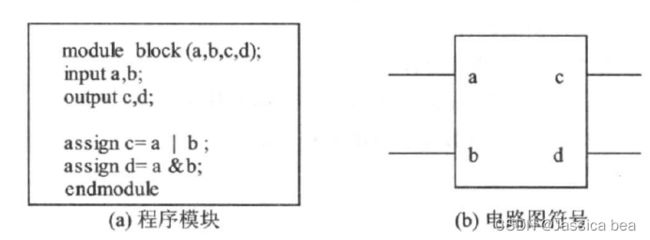

拿与门、或门举例:

module AndOR(a, b, c)//模块起

input a,b;//接口方向为输入

output c,d;

assign c = a & b;//组合逻辑-与

assign d = a | b;//组合逻辑-非

endmodule //模块终

注意:每条逻辑功能语句和数据定义的最后必须有分号。

程序模块---->>>到电路模块

注意

Verilog模块中的过程块(initial/always)、模块调用、assign赋值间是并行的

连续赋值语句不能独立于always块存在;

能独立存在的只有assign赋值,以及模块调用;

**

二、模块调用

**

模块调用包括元件库的调用以及已设计模块的调用,设计模块调用如下

1.模块例化有两种方法:按位置顺序调用、按名词调用

-

1.位置相关:

1)例化时,例化的参数顺序必须和模块顺序一致 2)例化时,只要写端口名字 -

2.名称相关:

1)必须指定当前例化的端口名称 2)端口的顺序可以自由排序

位置相关举例:

wire [3:0] x1;

wire [3:0] x2;

wire [4:0] x3;

add add_inst0

(

x1, //对应 模块本身的a,顺序必须一一对应

x2, //对应 模块本身的b

x3 //对应 模块本身的c

);

名称相关举例:

wire [3:0] x1;

wire [3:0] x2;

wire [4:0] x3;

add add_inst1

(

.a (x1),

.c (x3),//用“.”指定例化端口名,例化顺序可打乱

.b (x2)

);

三、调用实例

拿一个二选一多路选择器举例,二选一多路选择器代码如下:

module mux21 (dataa,datab, outdata, sel);

input [2:0] dataa;

input [2:0] datab;

inpur sel;

outdata [2:0] outdata;

········

········

endmodule

那么我们应该怎么样去调用它呢?如下:

<模块名><实例名>(

.端口(连线),

.端口(连线)

);

下面是用结构建模的方式调用上述二选一模块,实现三选一:

module mux31 (dataa, datab, datac, sel1, sel2, outdata);

input[2:0] dataa;

input[2:0] datab;

input [2:0] datac;

input sel1;

input sel2;

output [2:0] outdata;

wire [2:0] data;

mux21 mux21_dut1(

.dataa(dataa),

.datab(datab),

.outdata(data),

.sel(sel1)

);

mux21 mux21_dut2(

.dataa(data),

.datab(datac),

.outdata(outdata),

.sel(sel2)

);

endmodule

上述建模是利用了两个二选一多路选择器来构成了一个三选一多路选择器。

------->下一章: Verilog语法之模块巩固(3)(实例练习篇)