FPGA时钟IP核Demo

时钟IP核

对输入的时钟进行时钟分频、倍频、相位偏移

MMCM( 混合模式时钟管理 )和PLL(锁相环)内部的时钟资源

-

PLL 的全称是Phase Locked Loop , 锁相环,反馈控制电路

PLL对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。

-

时钟资源包含时钟管理单元CMT, 每个CMT由一个MMCM和一个PLL组成

MMCM mixed-mode clock manager 混合模式时钟管理

PLL( phase locked loop ) 锁相环

时钟资源简介

7系列的FPGA使用了专用的全局和区域时钟资源来管理和设计不同的时钟需求

-

全局时钟:专用的互联网络,降低时钟的偏斜,占空比的失真和功耗 --> 资源有限

专用的时钟缓冲、驱动结构,延时低

-

区域时钟:只能驱动区域内部的逻辑资源和IO口

Clock Management Tiles (CMT) 提供了时钟合成(Clock frequency synthesis ),倾斜矫正(deskew), 过滤抖动(jitter filtering) 功能

一个CMT包 1个MMCM 1个PLL

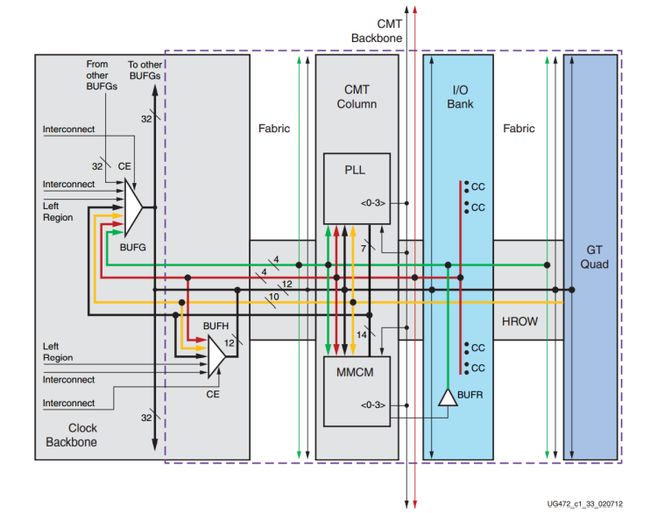

整体时钟资源视图

-

Clock Region 区域时钟

-

Clock Backbone 全局时钟线主干道

将FPGA分成左右两个部分,所有的全局时钟布线都要从Clock Backbone经过

-

BUFG 全局时钟缓存

-

HROW: 水平时钟线

水平方向贯穿每个时钟区域的中心部分

-

CMT Backbone CMT主干道

-

I/O Column 时钟的输入引脚

-

GT Column 串行时钟收发器

划分成几个不同的时钟区域,每个区域可以单独工作,也可以通过时钟主干道统一工作

单个时钟域视图

-

BUFG: 全局时钟缓冲器, BUFG的时钟输出可以经过Clock Backbone 到达任何一个区域,而且可以通过HROW到达每个区域内部的逻辑单元

-

BUFH : 水平时钟缓冲器,功能受限的BUFG,仅能在左右相邻的时钟区域

-

BUFIO: IO时钟缓冲器

-

BUFR: 区域时钟缓冲器,输出的时钟,仅能作用于本时钟区域

-

BUFMR: 多区域时钟缓冲器

-

CC 时钟专用引脚

-

MMCM: 混合模式时钟管理器

-

PLL: 锁相环

时钟引脚:SRCC, MRCC 专用时钟引脚

-

SRCC : 仅作用于本时钟区域

-

MRCC : 作用于本时钟区域和相邻时钟区域

_P、_N 差分信号

MMCM / PLL IP核

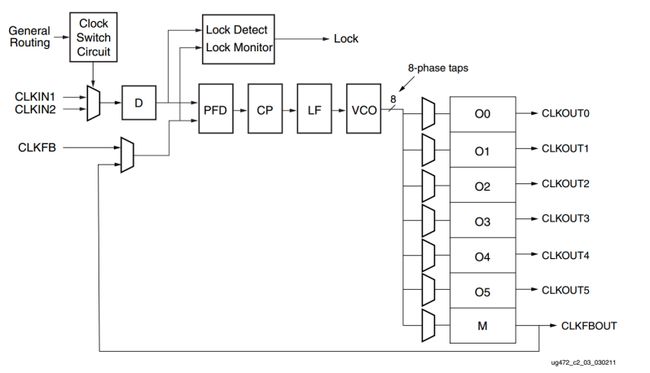

PLL

锁相环是一种反馈控制电路,利用外部输入的参考信号控制环路内部震荡信号的频率和相位。

锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

PLL主要用于为内存接口生成所需的时钟信号,也具有与器件逻辑的连接

PLL由以下几个部分组成

- 前置分频计数器(D计数器)

- 相位-频率检测器(PFD, Phase-Frequency Detector)电路

- 电荷泵(Charge Pump)

- 环路滤波器( Loop Filter )

- 压控振荡器( VCO,Voltage Controlled Oscillator )

- 反馈乘法器计数器( M计数器 )

- 后置分频计数器( O1-O6计数器 )

工作过程

-

PFD 检测其参考频率(FREF)和反馈信号(Feedback)之间的相位差和频率差,控制电荷泵和环路滤波器将相位差转换为控制电压

-

VCO 根据不同的控制电压产生不同的震荡频率,从而影响 Feedback 信号的相位和频率

-

在 FREF和 Feedback 信号具有相同的相位和频率之后,就认为 PLL 处于锁相的状态。

-

在反馈路径中插入M计数器会使VCO的震荡频率是FREF信号频率的M倍

FREF信号等于输入时钟(FIN) 除以预缩放计数器(D)

参考频率用以下方程描述:FREF= FIN/D

VCO 输出频率为 FVCO= FIN*M/D

PLL 的输出频率为 FOUT=(FIN*M)/(D*O)

MMCM

MMCM 的功能是PLL的超集,具有比PLL更强大的相移功能。

MMCM主要用于驱动器件逻辑(CLB, DSP, RAM 等 )的时钟

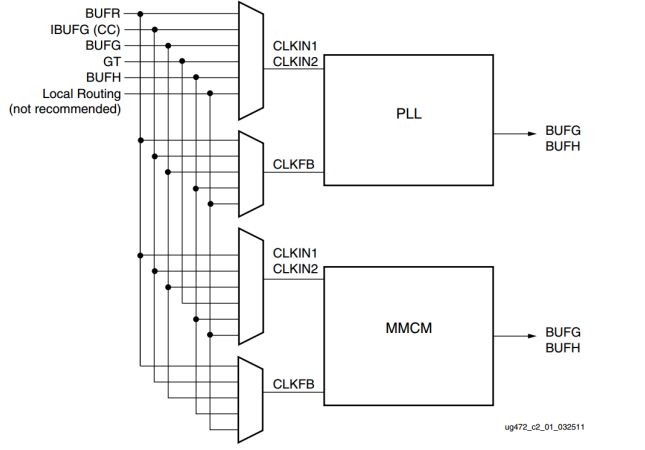

CMT

输入:

- IBUFG(CC) 具有时钟能力的IO输入 CCIO --> Clock Capable Input

- 区域时钟BUFR

- 全局时钟BUFG

- GT收发器输出时钟

- 行时钟BUFH

- 本地布线(不推荐使用本地布线来驱动时钟资源)

输出:

- 驱动全局时钟的BUFG

- 驱动全局时钟的BUFH

BUFG能够驱动整个器件内部的PL侧通用逻辑的所有时序单元的时钟端口。

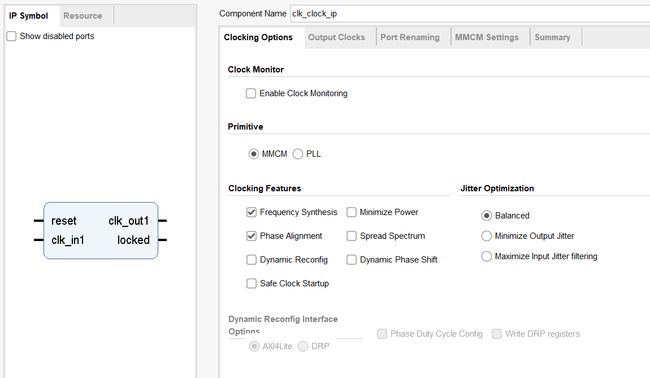

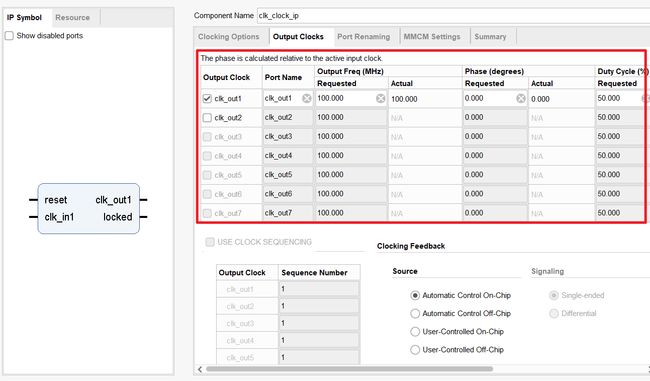

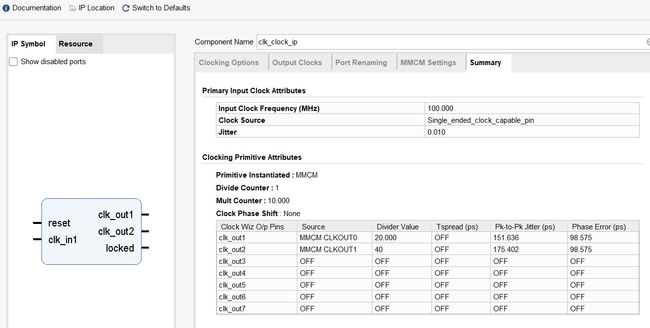

Clocking Wizard配置

使用时钟向导(Clocking Wizard)配置时钟IP核

IP核框图:

-

clk_in 输入时钟,可以从专用时钟引脚输入

-

locked信号,从 0 变为1 ,表示输出的时钟达到稳定

配置过程

步骤1

步骤2

- Clock Monitor 时钟监控: 一般不勾选

- MMCM、PLL MMCM的功能比PLL强大,根据需求选择

- Clocking Features

- Frequency Synthesis 频率合成 --> 输出不同频率时钟

- Phase Aligment 相位矫正

- Minimize Power 低功耗,时钟精度会降低

- Jitter Optimization 抖动设置

- 默认平衡模式

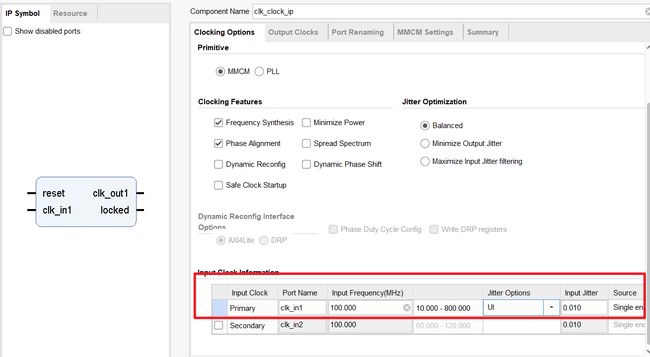

步骤3

- 输入时钟设置

步骤4

- 输出时钟设置

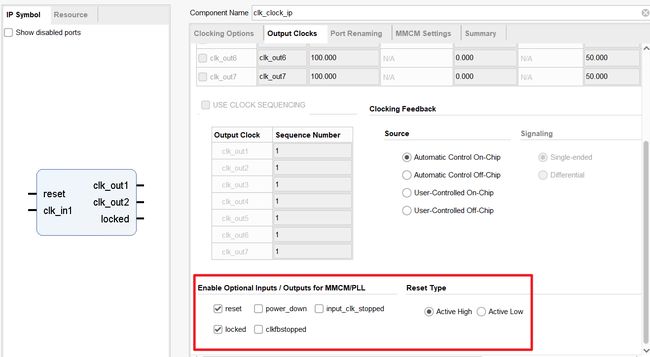

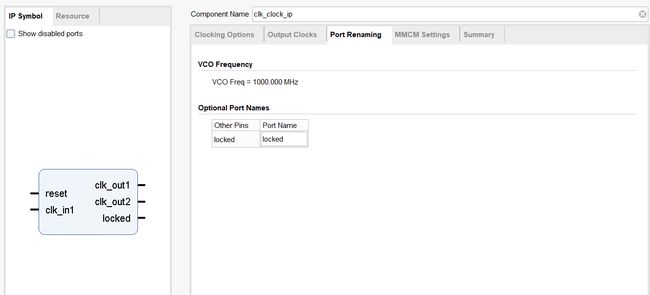

步骤5

- 输入输出引脚设置

- 端口重命名

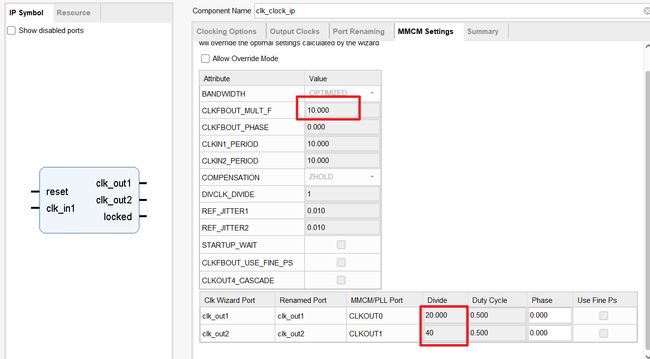

步骤7

- 默认

步骤8

使用IP核

verilog

`timescale 1ns / 1ps

//

// Engineer: wkk

// Create Date: 2022/11/25 12:53:36

// Module Name: clock_ip

//

module clock_ip(

input sys_clk,

input sys_rst_n,

output clk_50m,

output clk_25m,

output clk_ip_locked

);

clk_clock_ip u_clk_clock_ip(

.clk_out1 (clk_50m),

.clk_out2 (clk_25m),

.reset (~sys_rst_n),

.locked (clk_ip_locked),

.clk_in1 (sys_clk)

);

endmodule

testbench

`timescale 1ns / 1ns

//

// Engineer: wkk

// Module Name: clock_ip_tb

//

module clock_ip_tb();

reg sys_clk ;

reg sys_rst_n ;

wire clk_50m ;

wire clk_25m ;

wire clk_ip_locked ;

clock_ip u_clock_ip(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.clk_50m (clk_50m ),

.clk_25m (clk_25m ),

.clk_ip_locked (clk_ip_locked)

);

initial begin

sys_clk = 0;

sys_rst_n = 0;

end

always #5 sys_clk = ~sys_clk;

initial begin

#10

sys_rst_n = 1;

#200

$stop;

end

endmodule

参考

正点原子《启明星 ZYNQ 之 FPGA 开发指南 V2.0》