毕业设计开题分析:MIPS指令集硬件化设计与实现

基于专业背景分析题目:

一.主要设计方向

题目可概括为“软件硬件化”。软件硬件化涉及范围广泛,涉及软硬件协同的系统软件,都可以将其基于FPGA平台进行固化设计,以从系统结构的角度对其进行优化。从计算机专业的角度衡量:面向硬件系统的底层软件为操作系统内核,操作系统的内核也是整个系统最核心、最直接面向硬件的部分,也是最耗时的部分,针对操作系统核心(os kernel)的固化设计是目前系统结构/嵌入式系统方向非常热门的研究课题之一。

涉及专业核心课:数据结构,计算机组成原理,操作系统原理

课题方向:计算机系统结构

(阐明研究起点)

二.研究背景与意义

1.课题引入

嵌入式实时操作系统系统中应用的需求规模和复杂度的不断提升,在工业控制、医疗器械、汽车电子、智能家电、移动媒体、消费电子等诸多领域均得到了广泛应用。而随着应用领域的不断深化和细化,各种复杂的应用场景对的性能和稳定性要求也在逐渐加强。

根据国际电气和电子工程师协会(IEEE)的定义嵌入式系统是“控制、监视或者辅助设备、机器和车间运行的装置"(devices used to Control monitor,or assist the operation of equipment, maehinery or Plants)。一般而言整个嵌入式系统的体系结构可以分成四个部分:嵌入式处理器、嵌入式外围设备、嵌入式操作系统和嵌入式应用软件。由此可见嵌入式系统是硬件和软件的综合体。

由于大部分嵌入式实时系统都必须有较高的实时性保证因此对软硬件质量(特别是可靠性与运行速度方面)有着较高的要求。

提高嵌入式RTOS系统性能的途径主要分为三个方向:

1.不断优化现有的组织结构和运行算法,提高系统的运行效率;其缺陷在于算法的时间复杂度上限受限于具体硬件平台。

2.根据具体的应用场景和应用需求进行特殊的定制优化,提升系统运行的性能;其缺陷为设计架构太过特殊,不具有通用性,可移植性的特点。

3.提出新的软硬件协同架构,结合软硬件的优点,达到提升性能和增强稳定性的目的。

2.背景分析

将实时操作系统硬件化的这一概念最早由美国学者Jaehwan Lee[1]和Vincent John Mooney[2]于20世纪80年代提出,他们将实时操作系统分别用软件和硬件实现并在此二者的身上进行全面的分析比较,得出实时系统调度器使用专门的硬IP核实现将显著提升实时系统的效率。硬件操作系统使用硬件逻辑电路或者时序电路实现任务调度、中断处理、定时器以及资源管理等功能,以显著提高系统的实时响应性能。实现复杂软件算法的硬件化,可以兼顾在实时应用场景中的实时性以及可靠性。从九十年代初开始,成型的研究成果如Lennart Lindh等人主导的“FASTCHART”项目[1]等纷纷涌现。

而在硬件设计领域,传统的硬件电路设计流片成本高,需要很长的设计周期,对开发人员的专业要求非常高。而随着,电子设计自动化)设计技术的发展,—现场可编程门阵列)等可编程逻辑器件及相关技术的进步,硬件设计变得低成本、短周期、可定制,其设计以及验证方式也变得更加灵活,利用相关的硬件设计技术,操作系统硬件化的难度将会降低。

国内外研究现状:

一.国内现状

2007年,上海交通大学的侯觅提出并设计了一种基于硬件的实时任务管理器(RTM,Real-time Task Manager)[4],RTM为一个独立的部件,作为处理器外的扩展外围电路。其中使用任务控制逻辑控制任务调度、时间管理、事件管理等模块的逻辑控制,使用任务控制寄存器用于保存任务状态以及作为的控制接口。

2007年,中国科技大学的王传福和周学海[5]提出了一种提高硬件多线程处理器性能的方法。为流水线的每级功能单元上配置一组“快照寄存器”,用于存储恢复流水线状态,使得线程的切换完全由硬件部分实现,其设计达到了线程级并行,中断和保护现场完全由硬件实现。消除了线程切换过程中的幵销,从而提高硬件多线程处理器的性能。这种方案在硬件内部增加了额外的处理电路以及存储单元,需要对处理器的内部结构进行修改。

2008年浙江大学的陈天洲、胡威、严力科和马吉军提出了一种基于CPU/FPGA混合架构的硬件线程执行机制[6],在硬件线程库中提供多个功能的逻辑算法。系统创建线程后在上重构线程的硬件功能单元,然后使用硬件部分执行计算密集型任务。这种软硬件协同的设计可以很好的兼容现有的模型,减少软硬件之间的通信量,提高了可重构硬件的利用率。

2008年,东北大学的尹震宇博士、赵海教授、徐久强[7]教授等提出了一种基于硬件操作系统(Hardware-OS)的设计结构,通过在处理器中添加微指令处理逻辑及硬件处理模块,将中依赖复杂软件代码实现的部分系统机制,交由处理器硬件执行,降低了嵌入式软件开发的复杂度。这种方式在内部增加微指令硬件处理逻辑以及部分硬件电路,从而实现操作系统部分硬件化,它也要求对处理器的内部结构进行修改。

2008年,解放军信息工程学院的崔建华,孙红胜,王保进[8]基于“外部通用处理器+FPGA”的框架结构,设计了一种简单的硬件。系统在上支持任务调度、中断管理、定时器管理等基本功能,使用片内寄存器实现队列,采用多级比较器查找当前最高优先级就绪任务。和通过总线传输数据,并使用片选和中断信号实现快速的响应。这种设计方案采用基于总线的互连方式,无需对处理器的结构进行修改,基于ASIC的设计原理,对现有的部分功能软件进行了硬件化,并作为处理器的外围电路。

2019年,沈阳工业大学的张晓宇[9]将实时操作系统内核固化为独立的外围电路,将传统操作系统内核与用户任务分割开来,使CPU专注于用户任务的运算,而在任务调度方面用FPGA搭建的逻辑电路进行调度。可以发挥硬件系统的最大性能,利用FPGA可并行化设计的特点搭建了多核异构调度器。并将软件系统中的信号量、互斥信号量、定时计数器也进行了硬件化设计与实现,将上述软件系统中比较耗时的抽象功能使用可编程逻辑器件FPGA进行硬件化实现,形成一个完整的硬件操作系统内核。该系统可以在一个时钟之内完成所有OS内核命令。

2018年,青岛大学的徐向权[10]将μ C /0S-II中的任务创建、任务管理、任务切换、定时管理、信号量和互斥信号显管理使用硬件方式实现,形成硬件化操作系统内核 Hardware Rea1 - Time Operating Systen , HRToS )。再将定时管理迁移到硬件中用硬件定时器实现,由于硬件结构的并行性,使得定时中断的处理时间与任务数量无关。

二.国外现状

2006年,巴西的学者MELLISSA VETROMILLE和LUCIANO OST0对比分析了将实时操作系统的任务调度基于完全的软件实现、软件结合硬件协处理实现和完全的硬件实现,对比实验结果表明硬件调度模式表现出了更高的实时性能[11]。

2003年,美国的学者BRINDA GANESH、BRUCE JACOB和PAUL KOHOUT设计了由任务调度、事件处理和时间管理三个组件构成的硬件实时任务管理器。通过实践分析得出硬件实时任务管理器明显减少了系统开销,很大程度上发挥了系统潜在的多任务并行特性,使得实时操作系统的任务处理时间减少了90%[12]。

三.创新方向总结:(/1)无/有

| RTM-侯觅 |

Hardware-OS 尹震宇 |

RTOS- 崔建华 |

张晓宇 |

徐向权 |

Vincent Mooney |

FASTCHART |

王广辉 |

|

| 进程管理及调度 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 中断管理及调度 |

1 |

1 |

1 |

1 |

1 |

|||

| 时钟管理 |

1 |

1 |

1 |

1 |

1 |

1 |

||

| 进程同步通信 |

1 |

1 |

||||||

| 死锁检测 |

1 |

|||||||

| 信号量机制 |

1 |

1 |

||||||

| 多处理器支持 |

||||||||

| 互联方式:

|

1 |

3 |

1 |

1 |

1 |

1 |

1 |

1,3 |

| 硬件实现技术

|

2 |

2 |

2 |

2 |

2 |

2 |

2 |

2 |

| 面向cpu环境 (G/S) 通用/定制 |

G |

S |

G |

G |

G |

G |

G |

G |

从硬件实现技术的不同分类,大部分研究都采用了基于FPGA的实现方案,这是因为基于FPGA硬件开发的便捷性缩短了硬件设计周期。商业化的使用两种方式实现了硬件化的,基于的设计方案可以进一步优化系统性能。

从与硬件化部件不同的互连方式来看,大多数研究采用了基于数据地址总线的互连方式,只有三个系统支持特殊的指令集结构,这种架构需要指令集的特殊支持。

从上表可知:操作系统硬件化的研宄主要集中在任务管理和调度器的硬件化实现上,这两部分是传统操作系统中使用频繁且最耗时[13]的模块,对其进行硬件实现并优化可以有效加速系统响应处理。实时操作系统中资源的同步互斥也是关键之一,调度器的硬件化已经是老生常谈,但是关于调度算法的选择可以有优化空间:

举例如下:在传统的调度算法中,综合考虑了进程等待时间与运行时间的算法为动态优先级算法,表达式如下:

其中Trunning与Twait根据进程数据结构中记录的相对时间动态修正,而priority0是进程的初始相对优先级,其数值为一个系统运行时已经固定的偏移量。为了能够更好的反应用户喜好,初始优先级最好能在一定的取值范围内根据用户的使用频率动态调整。基于这样的背景,可以考虑使用小型神经网络来预测并修正priority0。

目前大部分神经网络都是通过软件设计实现,而用硬件实现的较少[17],一个是因为软件设计代码更灵活,更容易把一个算法用代码描述出来。但是对于操作系统的用户预测而言,一个学习线程长期在系统后台运行,对系统的性能消耗非常高。硬件时钟频率高,处理速度快并且实时性好。用硬件描述语言实现神经网络,可以更好的发挥神经网络的性能。[16]

其次,上述研究中多数支持简单的任务通信,调度等模块,而对于常用的死锁避免,却鲜有涉及。基于银行家算法的死锁避免策略有以下特点:

A.算法简洁,经个人微机系统长期验证,可靠性强的特点。

B.使用频率高,重复运算次数多,且涉及大量矩阵运算。考虑到FPGA具有并行度高等特点,银行家算法适合固化为独立的处理机部件。故本文选择基于银行家算法的死锁避免策略。

主要内容与待解决问题:

一.设计路径框架:

最小系统”是指能够使软硬件系统正常运作的最小软件系统和最小硬件系统的总称。首先设计的步骤在于基于FPGA,完成一个含实时嵌入式操作系统的最小系统,其硬件部分仅包含基本的处理器,复位、时钟电路,RAM,串口。

最终系统规模如下:

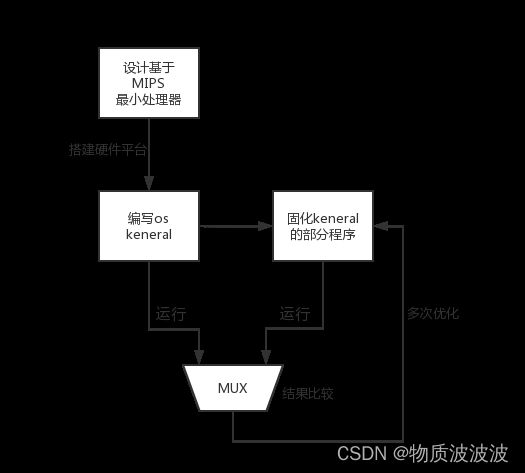

设计流程如下所示:

思路为非常清晰的循环结构,在完成最小系统的搭建后,将其中的银行家算法等核心程序进行固化设计,并与原系统进行性能对照。

设计方法与实施方案:

传统的硬件描述语言主要用于描述数字系统的结构行为、功能与接口,对较为复杂的算法设计实现则支持不够。

一.基于时序逻辑的设计方案(硬布线设计方案)

1.利用Handel−C语言设计

以往进行系统功能、结构以及行为等方面描述中所引用的语言主要为VHDL等,但在算法设计较为复杂的情况下,这种方式将难以发挥足够的支撑作用.但随着数字系统设计过程中相关的建模以及算法描述等逐渐增多,用于硬件描述的C语言或C++语言也得以形成.而以C语言为基础形成的Handel-C语言在目前应用过程中属于较为成熟的硬件描述语言.其主要以C语言以及C++语言为依据,进行一定程度上的语言与语法改进与扩充.实际应用过程中,系统设计人员无需进行C语言向VHDL或Verilog语言进行转换,避免系统错误或风险的出现.通过Handle-C语言,能够对算法直接描述,使编译加载于硬件中,促进编程时间与效率的改善,其具备的功能在Celoxica DK1中都有所体现.在系统应用过程中,尽管与VHDL语言在编程语法规则上表现出一定的差异,但从编程根本目的上基本保持一致,主要为实现算法思想的硬件化并通过在可编程芯片中的加载以便于应用.一般情况下,VHDL语言编写的基本流程可使模块化编程较为容易,设计人员会采用分块的方式以实

现其on功能.而Handle-C由于以C语言体系为基础,在编程时可直接进行算法的描述,具有较高的编程效率.但Handle-C在系统设计过程中还需考虑到具体的编译环境,其常用的编译环境软件DK1.1需能够满足C语言或C++语言环境的基本要求,所安装的编译器可选择如Borland

C++5.5或更高版本[14].

将传统c语言映射到硬件平台上方案如下:

(1) 决定如何将软件系统映射到目标硬件平台。

(2) 将传统的C语言程序转化成Handle-C程序,并用仿真器检查程序的语法错误。

(3) 从Handle-C提供的特别的操作平台去修改已有的程序代码。

(4) 加入良好的并行操作。

(5) 在程序中加入必须的硬件接口及映射仿真通道。

(6) 使用FPGA的布线工具去产生FPGA硬件映射程序。

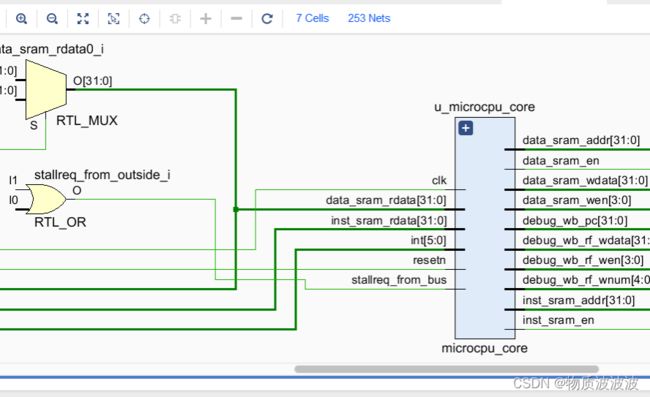

2.利用verilog模块化调用设计

图2-3 顶层模块调用子模块的模块化布线

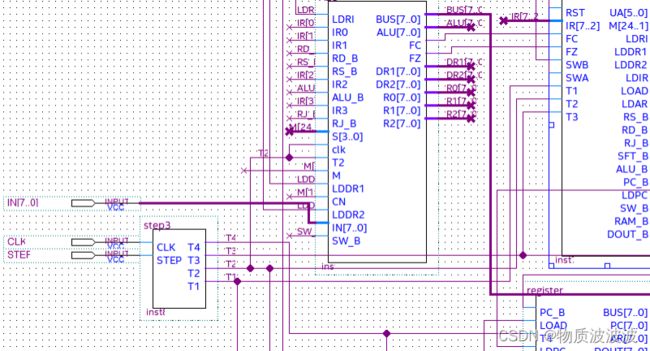

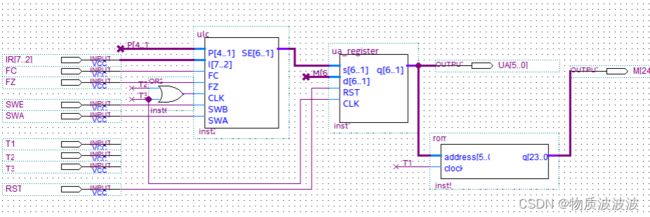

二.基于存储逻辑的设计方案(微程序设计方案)

将指令进行分解的好处是:分解后的指令颗粒度更小,更适合于硬件执行,并且更容易进行流水化。为了进一步提高执行效率,Intel CPU 中还可能针对某些指令序列进行优化,比如进行指令合并(macrofusion)等,以减少完成指令序列所需的时钟周期数。对于 CISC 指令的分解和合并操作可能由 CPU 中的硬件电路完成,也可能由微代码完成。Intel 会定期发布微代码的更新,这些更新会以文件的形式,随着操作系统升级包一起被下载到用户的计算机中,并在系统启动时自动安装到 CPU 内。微代码可以用于修补 CPU 的一部分 bug 或漏洞。比如著名的 Spectre 漏洞就是通过微码更新的方式修复的,但由于这个补丁会强制 CPU 在特定情况下关闭部分优化功能,这个补丁也导致了 CPU 性能的降低。

在 Windows 下,微码更新会随着 Windows Update 自动推送。但在 Linux 下,由于版权限制,用户可能需要手动安装对应的软件包,如 intel-microcode。

参考文献:

[1] Mooney V J, Blough D M. A hardware-software real-time operating system framework for

socs[J]. IEEE Design & Test of Computers, 2002, 19(6):44-51.

[2] Moisuc E C, Larionescu A,Ungurean I. Hardware event handling in the hardware real-time

operating systems[C]//2014 18th International Conference on System Theory, Control and

Computing (ICSTCC). Washington, DC:IEEE Computer Society, 2014:54-58

[3] L . Lindh , Fastchart - A Fast Time Deterministic Cpu and Hardware Based Realtime - kernel[C], Euromicro 91 Workshop on Real Time Systems .1991:3640.

[4]侯觅.基于硬件的实时任务管理器的研究[D]上海:上海交通大学,2007.

[5]王传福,周学海.提高硬件多线程处理器性能的方法[J].计算机工程,2008,34(5):34-37.

[6]陈天洲,严力科,胡威,马吉军.CPU/FPGA 混合架构上的硬件线程加速方法[J].

软件学报,2009,20(增刊)

[7]尹震宇,赵海,王金英等.一种嵌入式处理器上的HOS设计[J].计算机工程,2008

[8] 崔建华,孙红胜,王保进.硬件实时操作系统的设计与实现[J].电子技术应用,2008,8(5):34-37.

[9]实时操作系统内核硬件化的研究与实现 [D]. 张晓宇.沈阳工业大学,2019

[10] 硬件实时操作系统中任务切换技术的研究[D]. 徐向权.青岛大学,2018

[11] Vetromille M, Ost L, Marcon C A M, et al. Rtos scheduler implementation in hardware and

software for real time applications[C]//Seventeenth IEEE International Workshop on Rapid

System Prototyping. Washington, DC:IEEE Computer Society, 2006:163-168.

[12] Kohout P, Ganesh B, Jacob B. Hardware support for real-time operating systems[C]//First IEEE/ACM/IFIP International Conference on Hardware/ Software Codesign and Systems Synthesis (IEEE Cat. No.03TH8721). Washington, DC:IEEE Computer Society, 2003:45-51.

[13] 王广辉.基于FPGA的实时操作系统互斥锁硬件化技术研究[D].杭州:浙江大学,2013.

[14]吴春英.基于FPGA的遗传算法硬件化技术的研究[D].南京航空航天大学,2010.

[15] 基于FPGA的专用软件硬件化技术探讨[J]. 刘明;刘学明.赤峰学院学报(自然科学版),2015(13)

[16]张萧,黄晞,仲伟汉,张亮.Sigmoid函数及其导函数的FPGA实现[J].福建师范大学学报(自然科学版),2011,27(02):62-65.

[17]张智明,张仁杰.神经网络激活函数及其导数的FPGA实现[J].现代电子技术,2008,31(18):139.