海思3559万能平台搭建:添加一个新的sensor

前言

海思对摄像头的支持是只有固定的,如果我们想更换新的相机,让fpga接入通过lvds接口给3559提供视频源的话,除了相关配置,还需要添加新的sensor库,编译新的isp库,而且,如果移植不善,还可能对第三方库(SDL,FreeType,SDL_TTF等)造成影响,需要进一步修改

参考文档:

Sensor 调试指南

MIPI使用指南

HiMPP V4.0 媒体处理软件 FAQ

HiISP 开发参考

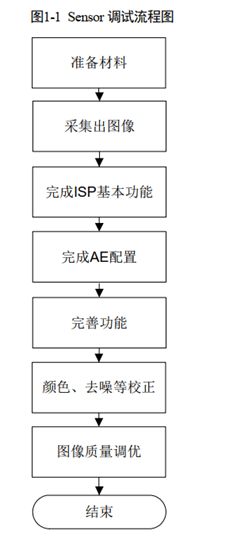

一.调试流程

1.2 准备材料

1.2.1 确认主芯片规格

支持 Master 模式,支持的线性、WDR 接口模式,支持输入频率上限。

1.2.2 Sensor datasheet

确认图像传输接口模式,输出频率。

确认曝光时间、增益如何设置,帧率如何修改。

确认在 WDR 模式下的以上两项。

LVDS 接口,需要确认同步码。

1.2.3 Initialize Settings

获取 Sensor Initialize Settings,一般至少要准备最大规格和标准分辨率两种序列。

1.3 采集图像

1.3.1 硬件准备就绪

首先验证是否可以读写 Sensor 寄存器。

利用 i2c_read/ i2c_write 命令,或 ssp_read/ssp_write 命令,测试 Sensor 寄存器读写。

该命令集成在默认的文件系统中,可直接调用。

1.3.2 完成初始化序列配置

配置初始化序列,建议参考版本发布包里面的 sensor 驱动,以便于快速开发。为了方便调试,此时要排除 AE 配置及帧率配置的干扰。

步骤 1 准备 Sensor 驱动

可以基于一款规格相近 Sensor(master/slave, i2c/spi, wdr/linear)驱动修改,尝试编译出 Sensor 库。具体可参看 isp/sensor/hi35xx/xxxx 目录下的 xxx_cmos.c 和xxx_sensor_ctl.c 文件进行修改。

修改 cmos_set_image_mode 函数,及 cmos_get_isp_default 中的 u32MaxWidth,u32MaxHeight 参数。使该 senosr 分辨率、帧率可以被正确设置。

在 sys_config.c 中修改 Sensor 时钟配置、I2C/SPI 接口 pin mux、vi 时钟、isp 时钟等寄存器。适配时,可基于相似规格的 Sensor 修改。对于从模式的 sensor,需要配置从模式 pin mux,Hi3559AV100、Hi3519AV100 默认打开从模式 pin mux,

Hi3516CV500 通过调用 vi_slave_mode_mux 配置从模式 pin_mux(默认不会调用该函数,对于从模式 sensor 要增加判断分支实现该函数的调用来正确配置从模式pin mux)。

步骤 2 Sensor 初始化序列

实现 void sensor_init()函数。参考 sensor 手册或者 sensor 厂家提供的 sensor 序列实现这个函数。对于从模式 sensor,在 sensor_init()函数中需要调用HI_MPI_ISP_GetSnsSlaveAttr 接口来实现从模式寄存器的适配。以 imx334 从模式的 sensor_init 为例:

void imx334slave_init(VI_PIPE ViPipe)

{

HI_U8 u8ImgMode;

HI_BOOL bInit;

HI_S32 SlaveDev;

HI_U32 u32Data;

bInit = g_pastImx334Slave[ViPipe]->bInit;

u8ImgMode = g_pastImx334Slave[ViPipe]->u8ImgMode;

SlaveDev = g_Imx334SlaveBindDev[ViPipe];

u32Data = g_Imx334SalveSensorModeTime[ViPipe];

/* hold sync signal as fixed */

CHECK_RET(HI_MPI_ISP_GetSnsSlaveAttr(SlaveDev,

&gstImx334Sync[ViPipe]));

gstImx334Sync[ViPipe].unCfg.stBits.bitHEnable = 0;

gstImx334Sync[ViPipe].unCfg.stBits.bitVEnable = 0;

gstImx334Sync[ViPipe].u32SlaveModeTime = u32Data;

CHECK_RET(HI_MPI_ISP_SetSnsSlaveAttr(SlaveDev,

&gstImx334Sync[ViPipe]));

/* 1. sensor i2c init */

imx334slave_i2c_init(ViPipe);

CHECK_RET(HI_MPI_ISP_GetSnsSlaveAttr(SlaveDev,

&gstImx334Sync[ViPipe]));

// release hv sync

gstImx334Sync[ViPipe].u32HsTime =

g_astImx334ModeTbl[u8ImgMode].u32InckPerHs;

if (g_pastImx334Slave[ViPipe]-

>astRegsInfo[0].stSlvSync.u32SlaveVsTime == 0) {

gstImx334Sync[ViPipe].u32VsTime =

g_astImx334ModeTbl[u8ImgMode].u32InckPerVs;

} else {

gstImx334Sync[ViPipe].u32VsTime = g_pastImx334Slave[ViPipe]-

>astRegsInfo[0].stSlvSync.u32SlaveVsTime;

}

gstImx334Sync[ViPipe].unCfg.u32Bytes = 0xc0030000;

gstImx334Sync[ViPipe].u32HsCyc = 0x3;

gstImx334Sync[ViPipe].u32VsCyc = 0x3;

CHECK_RET(HI_MPI_ISP_SetSnsSlaveAttr(SlaveDev,

&gstImx334Sync[ViPipe]));

/*sensor registers init*/

……

g_pastImx334Slave[ViPipe]->bInit = HI_TRUE;

return;

}

在 xxx_sensor_ctl.c 填写 sensor 寄存器的基地址 sensor_i2c_addr,地址的比特位宽sensor_addr_byte,寄存器的比特位宽信息 sensor_data_byte。在 xxx_cmos.c 文件中,注释掉全部 sensor_write_register,并在cmos_get_sns_regs_info 函数里,把 u32RegNum 配置为 0。以使 AE 不配置sensor,排除干扰。

----结束

在目录/Hi3559AV100_SDK_V2.0.3.1/mpp/component/isp/user/sensor下新建两个文件夹cyclone_lvds0,cyclone_lvds1,参考开发板自带的,新建自己的sensor库,直接给最后的源码如下

(后面给出)

1.3.3 Sensor 输出

本部分是基于 mpp 目录下的 sample 做整个通路的输出说明。主要在已完成了 sensor 序列的前提下做的。其步骤主要包括:MIPI、VI、ISP 以及 VPSS 的配置。这些配置可以参考已有 sensor 的配置进行简单修改即可。如果已经有集成的环境直接配置参数就可以运行,比如 Hisi PQTool 的启动脚本,对应 sensor 的目录有启动的配置文件,只需要配置正确即可。

步骤 1

在完成初始化的配置之后,可在 ISP 目录下编译即可生成新的 Sensor 的库,新库的路径为 Hi3559AV100_SDK_V2.0.3.1/mpp/component/isp/user/lib libsns_lvds0.a 和 Hi3559AV100_SDK_V2.0.3.1/mpp/component/isp/user/lib libsns_lvds0.so。

步骤 2

基于 mpp 的 sample 对新 Sensor 进行验证。在 sample/Makefile.param 文件中新增一款Sensor 的编译配置 SENSOR_TYPE,然后添加对应的 libsns_lvds0.a 文件

SENSOR0_TYPE ?= FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P

SENSOR1_TYPE ?= FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P

SENSOR_LIBS += $(REL_LIB)/libsns_lvds0.a

SENSOR_LIBS += $(REL_LIB)/libsns_lvds1.a

步骤 3

在 sample_comm.h 中的 SAMPLE_VI_MODE_E 中添加该 sensor 类型,注意和sample/Makefile.param 文件中新增的 SENSOR_TYPE 一致。然后再 sample_comm_isp.c中 SAMPLE_COMM_ISP_Init 函数中添加这个 sensor 类型的属性,如:Bayer pattern,帧率,宽高信息。

步骤 4 配置 MIPI 属性,

在 sample_comm_vi.c 中 SAMPLE_COMM_VI_SetMipiAttr 添加 MIPI属性,调试 MIPI/LVDS 部分参考《MIPI 使用指南》。

步骤 5 配置 VI 属性。

在 sample_comm_vi.c 中 SAMPLE_COMM_VI_StartDev 添加 VI 属性。

步骤 6

编译并运行相应的应用程序 sample_vio,如果一切顺利,此时整个系统已经运行。可以通过 cat /proc/umap/isp 或者 cat /proc/umap/hi_mipi 等查看信息。

步骤 7

如果 ISP 没有中断,请先检查 Sensor 输入时钟、输出信号及 Sensor 寄存器配置是否正常。具体操作请查阅《Hi35xx 专业型 HD IP Camera SoC 用户指南》或 《Hi35xxVxxxultra-HD Mobile Camera SoC 用户指南》。

步骤 8

若发现 MIPI、VI、ISP 等都正常,并想进行图像质量调节,可以把上述的配置移植到PQTool 的对应 sensor 配置文件中(在 config 目录下新建一个 sensor 目录,参考类似sensor 的配置做相应的修改即可)。

----结束

注意事项

当使用多路从模式 sensor 时,需要注意部分 sensor 由于自身对于 Vsync 信号和 Hsync信号的时序匹配的精度要求比较高。

在 VI 端开启同步模式时,需要对 sensor 的启动流程进行特别的处理。比如对于SONY 的 IMX477,工作在从模式时,因为其 Vsync 信号由 VI 端产生,Hsync 信号由 sensor 自己产生,Vsync 和 Hsync 信号在时序上需要严格匹配。

当 VI 端开启同步模式时,会改变 Vsync 信号时序来进行多路 Vsync 信号的同步,此时造成 Vsync 和 Hsync 信号时序上有差异从而导致 IMX477 数据输出异常。所以对于 IMX477 这类对 Vsync 和 Hsync 信号时序匹配精度要求比较高的 sensor,需要更改 sensor 的启动流程,在 VI 端开启同步模式前控制 sensor 先进入 standby模式,等 VI 端的 Vsync 信号同步结束后再控制 sensor 切换到数据输出模式。具体改动可参考 IMX477 多路从模式的 Sample 用例。

1.4 ISP 基本功能

本章节涉及 Sensor 部分,请仔细阅读 Sensor 的 Datasheet,或联系 Sensor 原厂 FAE。

结构体说明请参考《HiISP 开发参考》。

驱动文件一般分为 xxx_cmos.c 文件,xxx_cmos_ex.h 和 xxx_sensor_ctl.c 文件,分别用于 ISP 功能和初始化序列,xxx_cmos_ex.h 文件用于存放定义的驱动文件中的全局变量。

驱动文件共有 3 个 callback 函数,是 sensor 驱动向 Firmware 注册函数的接口。

HI_MPI_ISP_SensorRegCallBack(),HI_MPI_AE_SensorRegCallBack(),HI_MPI_AWB_Sen

sorRegCallBack(),分别对应 ISP、海思 AE 及海思 AWB。

开发流程

ISP 基本功能,请按如下顺序实现:

- cmos_set_image_mode(), cmos_set_wdr_mode()。

- sensor_global_init()。

- sensor_init(), sensor_exit()。

- cmos_get_isp_default(),cmos_get_isp_black_level()。

注意事项

cmos_set_image_mode ()

该函数用于区分不同分辨率,用 ISP_SNS_STATE_S 中的 u8ImgMode 传递分辨率模式

请注意返回值,返回“0”表示重新配置 Sensor,会调用 sensor_init(),返回“-2”表示不用重新配置 Sensor,无动作。

请注意 ISP_SNS_STATE_S 中 u32FLStd 和 au32FL 的区别。u32FLStd 是当前分辨率及 WDR 模式下,标准帧率(一般为 30fps)时的总行数。au32FL 是实际总行数,该参数会在其它函数中,由于降帧的原因,基于标准行数 u32FLStd 及帧率修改。

cmos_set_wdr_mode()

该函数用于区分不同 WDR 模式,用 ISP_SNS_STATE_S 中的 enWDRMode 传递。不同 WDR 模式,一般会修改 AE 相关函数,ISP default 内各个参数以及初始化序列。

sensor_init()

请根据不同的分辨率及 WDR 模式配置不同序列。

sensor_exit()

实现参考类似 sensor 的驱动即可。

cmos_get_isp_default()

该函数配置基本是调试或校正参数,可以在调试及校正时修改参数。

请注意不同 WDR 模式参数可能不一样,比如 Gamma,DRC 等。具体请参考

《HiISP 开发参考》。

cmos_get_isp_black_level()

在这个函数里面配置 RAW 数据四个通道的黑电平。

注意:!!!

有些类型的 sensor 的黑电平会随着 gain 值的变化而漂移,这时需要在不同的 ISO 值下分别校正出对应的黑电平值,在 cmos_get_isp_black_level()函数内进行相应的实现。

sensor_global_init()

该函数配置了 sensor 初始化的相关配置,包括分辨率、WDR 模式、u32FLStd 的默认值,初始化状态值及其他相关的状态值。

1.5 完成 AE 配置

完成 AE 配置后,图像就基本正常了。

开发流程

AE 配置,请按如下顺序实现:

- cmos_get_sns_regs_info()。

- cmos_get_ae_default(), cmos_again_calc_table(), cmos_dgain_calc_table()。

- cmos_get_inttime_max()。

- cmos_gains_update(), cmos_inttime_update()。

- cmos_fps_set(), cmos_slow_framerate_set()。

注意事项

cmos_get_sns_regs_info()

该函数用于配置需要确保同步性的 sensor、ISP 寄存器,如曝光时间、增益及总行数等。虽然这些寄存器可以通过直接调用 sensor_write_register()来配置,但无法保证同步性,可能出现闪烁。所以这些寄存器请一定要用该函数配置。

u8DelayFrmNum 是寄存器配置延时。举个例子,很多 Sensor 的增益是下一帧生效,但曝光时间是下下帧生效,所以需要增益晚一帧配置,以使增益和曝光时间同时生效,这时就需要用 Delay 的功能。配置 u8Cfg2ValidDelayMax 是控制 ISP 与sensor 同步,ISP 包括 ISP Dgain 和 WDR 曝光比等参数,可通过检查 ISP Dgain 是否与 sensor gain 同步来检查参数正确性。该参数的意义是生效时间,一般会比最大的 sensor 寄存器延迟多 1。

- bUpdate 用于控制该寄存器是否更新,如果不用修改,可以置为 false。cmos_get_ae_default()

- 请根据 sensor 修改参数。enAccuType 是计算精度的类型,常用AE_ACCURACY_TABLE 及 AE_ACCURACY_LINEAR。而AE_ACCURACY_DB 因为 CPU 计算精度问题,除非精度很低的,均由 TABLE的方式代替。

- LINEAR 方式是指曝光时间或增益以固定步长线性递增。比如每一步增长 0.325倍,或曝光时间每一步增长 1。步长由 f32Accuracy 决定。

- TABLE 方式一般用于增益,指每一步可以达到的增益通过查表的方式,在cmos_again_calc_table()或 cmos_dgain_calc_table()函数中计算得到。此时f32Accuracy 失去意义,不生效。海思 AE 默认计算顺序是先分配曝光时间,其次 again,然后 digain,最后 ispdgain。可以通过设置 AE Route 或 AE RouteEx 来调整分配顺序。

cmos_again_calc_table(), cmos_dgain_calc_table()这两个函数输入、输出完全一致,分别对应 Again 和 Dgain 的 TABLE 方式。下面以 Again 为例说明。 - pu32AgainLin 同时做输入和输出。做输入是 AE 计算出来的期望增益,1024 表示 1 倍。在该函数中,要查询到一个 sensor 可以实现的,小于该增益的最大增益。并重新赋给该参数作为向 AE 的输出。

- pu32AgainDb 是输出,AE 内部不用于运算,只是作为函数 cmos_gains_update()的输入。一般用于传递当前增益的 sensor 寄存器值。

例如:某 sensor 增益按 0.3dB 递增。sensor 寄存器值从 0 开始,每增加 1,对应增益分别为 0dB, 0.3dB, 0.6dB, 0.9dB…离线算出一个将 dB 转化为线性倍数的查找表,为 1024, 1060, 1097, 1136…

在函数中将输入的增益与查找表比对,假如输入为 1082,那查出来可用的最大增益是 1060,返回 1060 为实际生效的增益。

cmos_get_inttime_max()

该函数只在 xto1 WDR 模式下生效,用于计算不同曝光比的时候,曝光时间的最大值一般是行合成模式才需要。因为行合成模式,曝光时间的限制为长曝光时间加短曝光时间的和要小于一帧长度。所以不同曝光比下,最大曝光时间有差异,需要重新运算。

cmos_gains_update(), cmos_inttime_update()

这两个函数,是根据输入的 Again、Dgain 或曝光时间配置 sensor 寄存器。精度模式采用 TABLE 时,输入参数值为对应

cmos_again_calc_table()/cmos_dgain_calc_table() 函数中返回的 pu32AgainDb、

pu32DgainDb。

精度模式采用 Linear 时,输入参数为生效的增益、曝光时间除以 f32Accuracy。比

如 f32Accuracy 为 0.0078125,实际生效增益为 1.5 倍时,输入值为 1.5 / 0.0078125

= 192。

Xto1 WDR 模式,需要分别配置长短每一帧的曝光时间。cmos_inttime_update()会

被调用 X 次,分别传入不同帧曝光时间,第一次传入短帧。

cmos_fps_set(), cmos_slow_framerate_set()

**cmos_fps_set()**函数为手动帧率配置函数,需要根据传入的帧率配置 sensor 对应的寄存器,实现改变 sensor 帧率的功能,并返回实际生效的帧率及最大曝光行数。

cmos_slow_framerate_set()函数为自动降帧配置函数,需要根据当前曝光实际需要的最大曝光行数配置 sensor 对应的寄存器,实现 sensor 的降帧功能,并返回实际生效的最大曝光行数。

1.6 完善功能

完善所有其它的函数,确保所有功能工作正常。由于 AE 中的同步性最容易出错,请重点验证同步。

1.7 颜色、去噪等校正

请根据《图像质量调试工具使用指南》校正 sensor 参数。

1.8 图像质量调优

图像质量调优请参阅对应的《ISP 图像调优指南》。

如果看的太乱了直接快进到这里

上面的是官方文档,有些操作跳过了(我不严谨我不严谨),有些操作按照官方的做了然后添加了具体的做法,看起来会有点乱,如果只想看移植步骤可以直接看这里,提供了一个老版本移植到新版本的步骤说明一定一定要看清SDK版本

1.新建sensor库

源码位于/Hi3559AV100_SDK_V2.0.3.1/mpp/component/isp/user/sensor

在isp级目录编译,会在路径Hi3559AV100_SDK_V2.0.3.1/mpp/component/isp/user/lib 下生成libsns_lvds0.a和.so,并且会拷贝至Hi3559AV100_SDK_V2.0.3.1/mpp/out/linux/multi-core/lib

第一个相机,称为lvds0(1080P)共三个文件,

源码,实在太大了博客放不下

2.修改make sample/Makefile.param,增加sensor类型和刚刚生成的库

SENSOR0_TYPE ?= FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P

SENSOR1_TYPE ?= FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720

SENSOR_LIBS += $(REL_LIB)/libsns_lvds0.a

SENSOR_LIBS += $(REL_LIB)/libsns_lvds1.a

3.引用刚刚的库中的结构体stSnsLVDS0Obj

在\Hi3559AV100_SDK_V2.0.3.1\mpp\component\isp\include\hi_sns_ctrl.h中,添加

extern ISP_SNS_OBJ_S stSnsLVDS0Obj;

extern ISP_SNS_OBJ_S stSnsLVDS1Obj;

该头文件可能也需要在mpp/out/linux/multi-core/include下,没把握就都改了

4.sample/common路径下的sampl_comm.h增加sensor枚举类型

typedef enum hiSAMPLE_SNS_TYPE_E

{

SONY_IMX477_MIPI_12M_30FPS_12BIT,

SONY_IMX477_MIPI_9M_50FPS_10BIT,

SONY_IMX477_MIPI_8M_60FPS_12BIT,

SONY_IMX477_MIPI_8M_30FPS_12BIT,

SONY_IMX290_MIPI_2M_30FPS_12BIT,

SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1,

SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT,

SONY_IMX334_MIPI_8M_30FPS_12BIT,

SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1,

SONY_IMX277_SLVS_8M_120FPS_10BIT,

SONY_IMX277_SLVS_8M_30FPS_12BIT,

SONY_IMX277_SLVS_8M_60FPS_12BIT,

SONY_IMX277_SLVS_12M_30FPS_12BIT,

SONY_IMX277_SLVS_2M_240FPS_12BIT,

FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P,

FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P,

SAMPLE_SNS_TYPE_BUTT,

} SAMPLE_SNS_TYPE_E;

5.sample/common路径下的sampl_comm_vi.c增加sensor类型

(1)

static input_mode_t SAMPLE_COMM_VI_GetSnsInputMode(SAMPLE_SNS_TYPE_E enSnsType)

{

input_mode_t enInputMode;

switch (enSnsType)

{

case SONY_IMX277_SLVS_8M_120FPS_10BIT: /*imx277 test*/

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

enInputMode = INPUT_MODE_SLVS;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

enInputMode=INPUT_MODE_LVDS;

break;

default:

enInputMode = INPUT_MODE_MIPI;

break;

}

return enInputMode;

}

(2)

HI_S32 SAMPLE_COMM_VI_GetComboAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, combo_dev_t MipiDev, combo_dev_attr_t* pstComboAttr)

{

switch (enSnsType)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN6_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n", MipiDev, enSnsType);

}

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN6_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n", MipiDev, enSnsType);

}

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n",MipiDev, enSnsType);

}

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n",MipiDev, enSnsType);

}

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX290_12BIT_2M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (1 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN1_SENSOR_IMX290_12BIT_2M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n",MipiDev, enSnsType);

}

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX290_10BIT_2M_WDR3to1_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX334_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX334_12BIT_8M_WDR2to1_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_8lane_CHN0_SENSOR_IMX277_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_6lane_CHN0_SENSOR_IMX277_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_6lane_CHN0_SENSOR_IMX277_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_6lane_CHN0_SENSOR_IMX277_12BIT_2M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &LVDS_4lane_CHN0_FPGA_CYCLONE_16BIT_xM_1080P_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &LVDS_4lane_CHN1_FPGA_CYCLONE_16BIT_xM_720P_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

default:

SAMPLE_PRT("not support enSnsType: %d\n", enSnsType);

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

return HI_SUCCESS;

}

(3)

HI_S32 SAMPLE_COMM_VI_GetDevAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, VI_DEV_ATTR_S* pstViDevAttr)

{

switch (enSnsType)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_12M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_9M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX290_2M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX290_2M_BASE, sizeof(VI_DEV_ATTR_S));

pstViDevAttr->au32ComponentMask[0] = 0xFFC00000;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX334_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX334_8M_WDR2TO1_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX277_SLVS_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX277_SLVS_12M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX277_SLVS_2M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_FPGA_CYCLONE_1920x1080_BASE, sizeof(VI_DEV_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_FPGA_CYCLONE_720x576_BASE, sizeof(VI_DEV_ATTR_S));

break;

default:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_8M_BASE, sizeof(VI_DEV_ATTR_S));

}

return HI_SUCCESS;

}

(4)

HI_S32 SAMPLE_COMM_VI_GetPipeAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, VI_PIPE_ATTR_S* pstPipeAttr)

{

switch (enSnsType)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_4000x3000_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3000x3000_RAW10_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW10_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_1920x1080_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_1920x1080_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

pstPipeAttr->enPixFmt = PIXEL_FORMAT_RGB_BAYER_10BPP;

pstPipeAttr->enBitWidth = DATA_BITWIDTH_10;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW10_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_4000x3000_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_1920x1080_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_FPGA_CYCLONE_ATTR_1920x1080_RAW16_422_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_FPGA_CYCLONE_ATTR_720x576_RAW16_422_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

default:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

}

return HI_SUCCESS;

}

(5)

HI_S32 SAMPLE_COMM_VI_GetChnAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, VI_CHN_ATTR_S* pstChnAttr)

{

switch (enSnsType)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_4000x3000_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3000x3000_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_4000x3000_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_FPGA_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_FPGA_ATTR_720x576_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

default:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

}

return HI_SUCCESS;

}

(6)

HI_S32 SAMPLE_COMM_VI_GetSizeBySensor(SAMPLE_SNS_TYPE_E enMode, PIC_SIZE_E* penSize)

{

HI_S32 s32Ret = HI_SUCCESS;

if (!penSize)

{

return HI_FAILURE;

}

switch (enMode)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enMode %d!",enMode);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

*penSize = PIC_4000x3000;

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

*penSize = PIC_3000x3000;

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

*penSize = PIC_1080P;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

*penSize = PIC_3840x2160;

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

*penSize = PIC_4000x3000;

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

*penSize = PIC_1080P;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

*penSize=PIC_1080P;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

*penSize=PIC_D1_PAL;

break;

default:

*penSize = PIC_3840x2160;

break;

}

return s32Ret;

}

(7)

combo_dev_t SAMPLE_COMM_VI_GetComboDevBySensor(SAMPLE_SNS_TYPE_E enMode, HI_S32 s32SnsIdx)

{

combo_dev_t dev = 0;

switch (enMode)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enMode %d!",enMode);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

if(0 == s32SnsIdx)

{

dev= 0;

}

else if(1 == s32SnsIdx)

{

dev= 2;

}

else if(2 == s32SnsIdx)

{

dev= 4;

}

else if(3 == s32SnsIdx)

{

dev= 6;

}

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

dev= 0;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

dev= 2;

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

if(0 == s32SnsIdx)

{

dev= 0;

}

else if(1 == s32SnsIdx)

{

dev= 2; //8;

}

break;

default:

dev= 0;

break;

}

return dev;

}

/* xin.han add fpgaDEV配置 参考FAQ3.3.5.2*/

VI_DEV_ATTR_S DEV_ATTR_FPGA_CYCLONE_1920x1080_BASE =

{

VI_MODE_LVDS,

VI_WORK_MODE_1Multiplex,

{0xFF000000, 0x00FF0000},

VI_SCAN_PROGRESSIVE,

{-1, -1, -1, -1},

VI_DATA_SEQ_UYVY,

{

/*port_vsync port_vsync_neg port_hsync port_hsync_neg */

VI_VSYNC_PULSE, VI_VSYNC_NEG_LOW, VI_HSYNC_VALID_SINGNAL,VI_HSYNC_NEG_HIGH,VI_VSYNC_VALID_SINGAL,VI_VSYNC_VALID_NEG_HIGH,

/*hsync_hfb hsync_act hsync_hhb*/

{0, 1920, 0,

/*vsync0_vhb vsync0_act vsync0_hhb*/

0, 1080, 0,

/*vsync1_vhb vsync1_act vsync1_hhb*/

0, 0, 0}

},

VI_DATA_TYPE_YUV,

HI_FALSE,

{1920 , 1080},

{

{

{1920 , 1080},

},

{

VI_REPHASE_MODE_NONE,

VI_REPHASE_MODE_NONE

}

},

{

WDR_MODE_NONE,

1080

},

DATA_RATE_X1

};

//fpga

VI_DEV_ATTR_S DEV_ATTR_FPGA_CYCLONE_720x576_BASE =

{

VI_MODE_LVDS,

VI_WORK_MODE_1Multiplex,

{0xFF000000, 0x00FF0000},

VI_SCAN_PROGRESSIVE,

{-1, -1, -1, -1},

VI_DATA_SEQ_UYVY,

{

/*port_vsync port_vsync_neg port_hsync port_hsync_neg */

VI_VSYNC_PULSE, VI_VSYNC_NEG_LOW, VI_HSYNC_VALID_SINGNAL,VI_HSYNC_NEG_HIGH,VI_VSYNC_VALID_SINGAL,VI_VSYNC_VALID_NEG_HIGH,

/*hsync_hfb hsync_act hsync_hhb*/

{0, 720, 0,

/*vsync0_vhb vsync0_act vsync0_hhb*/

0, 288, 0,

/*vsync1_vhb vsync1_act vsync1_hhb*/

0, 0, 0}

},

VI_DATA_TYPE_YUV,

HI_FALSE,

{720 , 288},

{

{

{720 , 288},

},

{

VI_REPHASE_MODE_NONE,

VI_REPHASE_MODE_NONE

}

},

{

WDR_MODE_NONE,

288

},

DATA_RATE_X1

};

/* xin.han add fpga LVDS配置 参考FAQ3.3.5.1*/

combo_dev_attr_t LVDS_4lane_CHN0_FPGA_CYCLONE_16BIT_xM_1080P_NOWDR_ATTR =

{

.devno = 0,

.input_mode = INPUT_MODE_LVDS,

.data_rate = MIPI_DATA_RATE_X1,

.img_rect = {0, 0, 1920, 1080},

.lvds_attr =

{

.input_data_type = DATA_TYPE_RAW_16BIT,//pay attention to this

.wdr_mode = HI_WDR_MODE_NONE,

.sync_mode = LVDS_SYNC_MODE_SAV,

.vsync_attr = {LVDS_VSYNC_NORMAL, 0, 0},

.fid_attr = {LVDS_FID_NONE, HI_TRUE},

.data_endian = LVDS_ENDIAN_BIG,

.sync_code_endian = LVDS_ENDIAN_BIG,

.lane_id = {0, 1, 2, 3,-1,-1,-1,-1,-1,-1,-1,-1,-1,-1,-1,-1},

.sync_code = {

#if 1

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 0

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 1

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 2

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 3

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

#else

{

{0xAC00, 0xB600, 0x8000, 0x9D00}, // lane 0

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAC00, 0xB600, 0x8000, 0x9D00}, // lane 1

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAC00, 0xB600, 0x8000, 0x9D00}, // lane 2

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAC00, 0xB600, 0x8000, 0x9D00}, // lane 3

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

{0xAC00, 0xB600, 0x8000, 0x9D00},

},

#endif

}

}

};

combo_dev_attr_t LVDS_4lane_CHN1_FPGA_CYCLONE_16BIT_xM_720P_NOWDR_ATTR =

{

.devno = 2,

.input_mode = INPUT_MODE_LVDS,

.data_rate = MIPI_DATA_RATE_X1,

.img_rect = {0, 0, 720, 288},

.lvds_attr =

{

.input_data_type = DATA_TYPE_RAW_16BIT,//pay attention to this

.wdr_mode = HI_WDR_MODE_NONE,

.sync_mode = LVDS_SYNC_MODE_SAV,

.vsync_attr = {LVDS_VSYNC_NORMAL, 0, 0},

.fid_attr = {LVDS_FID_NONE, HI_TRUE},

.data_endian = LVDS_ENDIAN_BIG,

.sync_code_endian = LVDS_ENDIAN_BIG,

.lane_id = {4, 5, 6, 7,-1,-1,-1,-1,-1,-1,-1,-1,-1,-1,-1,-1},

.sync_code = {

#if 1

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 0

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 1

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 2

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

{

{0xAB00, 0xB600, 0x8000, 0x9D00}, // lane 3

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

{0xAB00, 0xB600, 0x8000, 0x9D00},

},

#endif

}

}

};

/* xin.han add fpga pipe设置,参考FAQ3.3.5.3*/

VI_PIPE_ATTR_S PIPE_FPGA_CYCLONE_ATTR_1920x1080_RAW16_422_3DNR_RFR =

{

VI_PIPE_BYPASS_NONE, HI_TRUE, HI_TRUE,

1920, 1080,

PIXEL_FORMAT_YVU_SEMIPLANAR_420,

COMPRESS_MODE_NONE,

DATA_BITWIDTH_8,

HI_FALSE,

{

PIXEL_FORMAT_YVU_SEMIPLANAR_422,

DATA_BITWIDTH_8,

VI_NR_REF_FROM_RFR,

COMPRESS_MODE_NONE

},

HI_FALSE,

{ -1, -1}

};

//fpga lvds input

VI_PIPE_ATTR_S PIPE_FPGA_CYCLONE_ATTR_720x576_RAW16_422_3DNR_RFR =

{

VI_PIPE_BYPASS_NONE, HI_TRUE, HI_TRUE,

720, 288,

PIXEL_FORMAT_YVU_SEMIPLANAR_420,

COMPRESS_MODE_NONE,

DATA_BITWIDTH_8,

HI_FALSE,

{

PIXEL_FORMAT_YVU_SEMIPLANAR_422,

DATA_BITWIDTH_8,

VI_NR_REF_FROM_RFR,

COMPRESS_MODE_NONE

},

HI_FALSE,

{ -1, -1}

};

/* xin.han add fpga*/

VI_CHN_ATTR_S CHN_FPGA_ATTR_1920x1080_420_SDR8_LINEAR =

{

{1920, 1080},

PIXEL_FORMAT_YVU_SEMIPLANAR_420,

DYNAMIC_RANGE_SDR8,

VIDEO_FORMAT_LINEAR,

COMPRESS_MODE_NONE,

0, 0,

0,

{ -1, -1}

};

//cyclone fpga lvds input

VI_CHN_ATTR_S CHN_FPGA_ATTR_720x576_420_SDR8_LINEAR =

{

{720, 288},

PIXEL_FORMAT_YVU_SEMIPLANAR_420,

DYNAMIC_RANGE_SDR8,

VIDEO_FORMAT_LINEAR,

COMPRESS_MODE_NONE,

0, 0,

0,

{ -1, -1}

};

/* xin.han add fpga */

ISP_PUB_ATTR_S ISP_PUB_ATTR_FPGA_LVDS_xM_xFPS_1080P =

{

{0, 0, 1920, 1080},

{1920, 1080},

30,

BAYER_GRBG,

WDR_MODE_NONE,

0,

};

//fpga lvds data

ISP_PUB_ATTR_S ISP_PUB_ATTR_FPGA_LVDS_xM_xFPS_720P =

{

{0, 0, 720, 288},

{720, 288},

30,

BAYER_GRBG,

WDR_MODE_NONE,

0,

};

6.sample/common路径下的sampl_comm_isp.c增加sensor类型

(1)

HI_S32 SAMPLE_COMM_ISP_GetIspAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, ISP_PUB_ATTR_S* pstPubAttr)

{

switch (enSnsType)

{

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_12M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_9M_50FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_8M_60FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_8M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX290_2M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX290_MIPI_2M_30FPS_WDR3TO1_LINE, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX334_4K_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX334_4K_30FPS_WDR2TO1_LINE, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_8M_120FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_8M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_8M_60FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_12M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_2M_240FPS, sizeof(ISP_PUB_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

memcpy(pstPubAttr, &ISP_PUB_ATTR_FPGA_LVDS_xM_xFPS_1080P, sizeof(ISP_PUB_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

memcpy(pstPubAttr, &ISP_PUB_ATTR_FPGA_LVDS_xM_xFPS_720P, sizeof(ISP_PUB_ATTR_S));

break;

default:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_8M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

}

return HI_SUCCESS;

}

(2)

ISP_SNS_OBJ_S* SAMPLE_COMM_ISP_GetSnsObj(HI_U32 u32SnsId)

{

SAMPLE_SNS_TYPE_E enSnsType;

enSnsType = g_enSnsType[u32SnsId];

switch (enSnsType)

{

// printf("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

return &stSnsImx477Obj;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

return &stSnsImx290Obj;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

return &stSnsImx334SlaveObj;

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

return &stSnsImx334Obj;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

return &stSnsImx277SlvsObj;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

return &stSnsLVDS0Obj;

// return &stSnsImx477Obj;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

return &stSnsLVDS1Obj;

// return &stSnsImx477Obj;

default:

return HI_NULL;

}

}

7.component/isp/user/3a/include路径下的hi_awb_comm.h增加结构体(out/linux/multi-core/include)

typedef struct hiAWB_SENSOR_DEFAULT_S {

HI_U16 u16WbRefTemp; /* RW;reference color temperature for WB */

HI_U16 au16GainOffset[ISP_BAYER_CHN_NUM]; /* RW; gain offset for white balance */

HI_S32 as32WbPara[AWB_CURVE_PARA_NUM]; /* RW; parameter for wb curve,p1,p2,q1,a1,b1,c1 */

HI_U16 u16GoldenRgain; /* Rgain for the golden sample */

HI_U16 u16GoldenBgain; /* Bgain for the golden sample */

HI_U16 u16SampleRgain; /* Rgain for the current sample */

HI_U16 u16SampleBgain; /* Bgain for the current sample */

AWB_AGC_TABLE_S stAgcTbl;

AWB_CCM_S stCcm;

HI_U16 u16InitRgain; /* Init WB gain */

HI_U16 u16InitGgain;

HI_U16 u16InitBgain;

HI_U8 u8AWBRunInterval; /* RW;AWB Run Interval */

HI_U16 au16InitCCM[CCM_MATRIX_SIZE];

ISP_SPECAWB_ATTR_S stSpecAwbAttrs;

ISP_SPECAWB_CAA_CONTROl_S stCaaControl;

} AWB_SENSOR_DEFAULT_S;

8. component/isp/include/arch/hi3559av100/include(out/linux/multi-core/include)下hi_comm_sns.h,注意类型

typedef struct hiISP_CMOS_DEFAULT_S {

ISP_CMOS_ALG_KEY_U unKey;

const ISP_CMOS_DRC_S *pstDrc;

const ISP_CMOS_DEMOSAIC_S *pstDemosaic;

const ISP_CMOS_PREGAMMA_S *pstPreGamma;

const ISP_CMOS_GAMMA_S *pstGamma;

const ISP_CMOS_SHARPEN_S *pstSharpen;

const ISP_CMOS_EDGEMARK_S *pstEdgeMark;

const ISP_CMOS_LDCI_S *pstLdci;

const ISP_CMOS_DPC_S *pstDpc;

const ISP_CMOS_LSC_S *pstLsc;

const ISP_CMOS_RLSC_S *pstRLsc;

const ISP_CMOS_GE_S *pstGe;

const ISP_CMOS_ANTIFALSECOLOR_S *pstAntiFalseColor;

const ISP_CMOS_BAYERNR_S *pstBayerNr;

const ISP_CMOS_SPLIT_S *pstSplit;

const ISP_CMOS_CA_S *pstCa;

const ISP_CMOS_CLUT_S *pstClut;

const ISP_CMOS_LOGLUT_S *pstLogLUT;

const ISP_CMOS_PRELOGLUT_S *pstPreLogLUT;

const ISP_CMOS_WDR_S *pstWdr;

ISP_CMOS_NOISE_CALIBRATION_S stNoiseCalibration;

ISP_CMOS_SENSOR_MAX_RESOLUTION_S stSensorMaxResolution;

ISP_CMOS_SENSOR_MODE_S stSensorMode;

ISP_CMOS_DNG_COLORPARAM_S stDngColorParam;

ISP_CMOS_WDR_SWITCH_ATTR_S stWdrSwitchAttr;

ISP_CMOS_AWB_ATTR_S stAwbAttr;

} ISP_CMOS_DEFAULT_S;

需要在isp添加的源码文件中对应修改

9. component/isp/include/arch/hi3559av100/include(out/linux/multi-core/include)下hi_comm_sns.h,注意类型

typedef struct hiISP_CMOS_EDGEMARK_S {

HI_BOOL bValid;

HI_BOOL bEnable; /* RW; Range:[0, 1]; Format:1.0;Enable/Disable Edge Mark */

HI_U8 u8Threshold; /* RW; range: [0, 255]; Format:8.0; */

HI_U32 u32Color; /* RW; range: [0, 0xFFFFFF]; Format:32.0; */

} ISP_CMOS_EDGEMARK_S;

10.sample/venc路径下的config.c增加sensor类型

(1)

HI_S32 PLATFORM_VI_GetSizeBySensor(SAMPLE_SNS_TYPE_E enMode, PIC_SIZE_E* penSize)

{

HI_S32 s32Ret = HI_SUCCESS;

if (!penSize)

{

return HI_FAILURE;

}

switch (enMode)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enMode %d!",enMode);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

*penSize = PIC_4000x3000;

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

*penSize = PIC_3000x3000;

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

*penSize = PIC_1080P;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

*penSize = PIC_3840x2160;

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

*penSize = PIC_4000x3000;

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

*penSize = PIC_1080P;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

*penSize=PIC_1080P;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

*penSize=PIC_D1_PAL;

break;

default:

*penSize = PIC_3840x2160;

break;

}

return s32Ret;

}

(2)

combo_dev_t PLATFORM_VI_GetComboDevBySensor(SAMPLE_SNS_TYPE_E enMode, HI_S32 s32SnsIdx)

{

combo_dev_t dev = 0;

switch (enMode)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enMode %d!",enMode);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

if(0 == s32SnsIdx)

{

dev= 0;

}

else if(1 == s32SnsIdx)

{

dev= 2;

}

else if(2 == s32SnsIdx)

{

dev= 4;

}

else if(3 == s32SnsIdx)

{

dev= 6;

}

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

dev= 0;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

dev= 2;

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

if(0 == s32SnsIdx)

{

dev= 0;

}

else if(1 == s32SnsIdx)

{

dev= 2; //8;

}

break;

default:

dev= 0;

break;

}

return dev;

}