FPGA/ZYNQ学习总结

文章目录

- zynq学习总结

-

- 启动开发板-启动模式

- PL部分的开发

- PS部分的开发

- PS、PL的联动-AXI

-

- MIO

- EMIO

- AXI GPIO IP核

- 创建AXI类型的IP核

- MIO、EMIO、AXI GPIO的理解

- 如何保证是PS或PL单独运行

- 疑惑

-

- 用硬件SPI驱动LCD的引脚约束问题

zynq学习总结

zynq7000系列包含2个ARM Coretex A9和Artix 7系列的FPGA,分别称为PS、PL。

ebaz4205是矿板,板上有xc7z010芯片,因此可以玩ARM和FPGA,而且便宜。

如何改造原始矿板网上有教程,不多说。我在咸鱼买了补焊后的矿板、扩展版、调试器。PS和PL是独立的两部分,我买的矿板为PL端补焊了50MHz的晶振。

启动开发板-启动模式

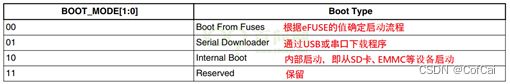

不同芯片都有不同的启动模式,就像原来学习的STM32、IMX6ULL,可以从不同设备进行启动。下图分别时STM32和IMX6ULL的启动模式选择:

ebaz4205矿板默认从NAND flash启动(自带了linux系统,不过需要密码),如果要改为SD卡启动,则需要将矿板背面的电阻R4258移动到R4277,其实就是改变启动默认(通过电平)。

- 自带的linux系统需要登陆用户名和密码,网上有相应的教程删除登陆用户名,但是我没成功(网络配置没成功,导致tftp不能用);

- 也可以通过自己做uboot、kernel、rootfs,然后烧写到SD卡中,调整矿板为从SD卡启动,但是需要改焊电阻,手上没工具,所以暂时失败;

- 最后是通过jtag调试器,可以正常下载程序;

上面方式1删除登陆用户名的基本方法是:读出NAND flash中的镜像,挂载镜像到本机,修改镜像,写回到NAND flash。具体过程如下:

-

开发板上电3s之内通过输入d(串口)可进入uboot;

-

设置ipaddr、serverip环境变量,就是将自己(ebaz4205)设置为tftp客户端;

-

通过nand命令读出NAND flash中的镜像文件,包括uboot、kernel、rootfs等;

-

通过tftp将镜像文件保存到tftp server的tftp目录去;

-

通过xxx命令挂载得到的rootfs;

-

修改挂载的rootfs中的某些文件,就是去除登陆密码,还可以关掉挖矿程序;

-

将修改后的rootfs写回到NAND flash;

-

参考链接-通过修改rootfs重置密码,但是我网络配置没成功,失败;

-

[突然找到可直接重置密码的命令!!!!!TODO](xjtuecho/EBAZ4205: A 5$ Xilinx ZYNQ development board. (github.com)),进入uboot,然后输入:

setenv nandboot "echo Copying Linux from NAND flash to RAM... && nand info && run nandroot;nand read 0x100000 0x2220000 0x300000 && fpga loadb 0 0x100000 0x300000 && nand read ${kernel_load_address} 0x300000 ${kernel_size} && nand read ${devicetree_load_address} 0x800000 ${devicetree_size}" run nandboot setenv bootargs 'console=ttyPS0,115200 root=/dev/mtdblock6 rootfstype=jffs2 noinitrd rw rootwait reboot=cold,hard emergency init=/bin/sh' bootm ${kernel_load_address} - ${devicetree_load_address} init=/bin/sh passwd 还有关闭BTC挖矿程序: mv /etc/rcS.d/S95cgminer.sh /etc/rcS.d/K95cgminer.sh reboot

上面方式2的过程同构建IMX6UL的镜像:

-

uboot、kernel、rootfs等构建,在网上找到已找到构建好的镜像;

-

后续过程如下:

谢谢楼主,板子跑起来了。 发个新手步骤 先把SD卡分两个区 第一个FAT 第二个 ext4,需要在linux下操作(VM虚拟机装的Linux的Gparted分区工具), 都是最常见的分区方法,FAT分个100M就够 压缩包拷贝到linux虚拟机里,用命令, 用su,密码,root账号命令行登陆,解压文件,保证权限正确 tar -xvf /bootfat.tar.bz2 -C /mnt mnt为你挂载tf卡第一个fat32分区的路径 tar -xvf /rootfs.tar.gz -C /mnt mnt为你挂载tf卡第二个ext4分区的路径 插到板子上,然后启动就OK。 默认用户名osrc 密码root root 密码也是root 需要先创建root账号才可以用root登陆,sudo adduser root 先设置ROOT用户sudo passwd root 再 su -

不过也可以通过Xilinx提供的petalinux进行构建更加方便;

PL部分的开发

这部分类似于毕业实习时前几天的操作。

创建Vivado工程、选择芯片或开发板、创建设计源文件、(创建仿真文件)、创建约束文件(可以可视化配置-schematic)、综合仿真、生成bitstream、下载。

约束文件:比如将代码中的clk port约束到N18接口,leds port约束到 E20.

ebaz4205的PL端本身是没有时钟源的,需要补焊,晶振是与N18相连的,即N18会产生50MHz的频率。

PL部分相比于PS,少了创建zynq,并导出硬件信息到SDK中进行开发。

参考链接-利用PL资源实现流水灯

参考链接-利用PL资源实现HDMI

PS部分的开发

在PL部分的基础上,添加zynq IP核,并导出硬件信息到SDK并进行开发。

Vivado中通过zynq processing system创建ARM核,配置DDR,以及其它非必须操作(比如配置串口、spi等,这部分可以使用MIO资源,也可以使用EMIO,甚至可以利用FPGA资源生成对应的硬件电路并使用)。然后创建HDL,生成bitstream、导出硬件描述信息、启动SDK。在SDK创建工程,进行ARM部分的(逻辑)开发,可以利用自带的一些开发examples。

PS、PL的联动-AXI

方式比较多,目前所了解的通过EMIO、AXI GPIO IP核、创建AXI的IP核并通过reg控制。

参考链接-PL端利用PS端的时钟,就是将PS端的时钟引脚(M_AXI_GP0_ACLK)连接到PL端的时钟输入引脚(FCLK_CLK0),FCLK_CLK0内部其实有锁相环PLL,可以配置FCLK_CLK0的输出频率。

然后,如果自己编写的LED IP核需要时钟,则直接连接到FCLK_CLK0。

MIO

PS部分的原生GPIO,就像STM32中的GPIO、IMX6ULL的GPIO,不存在与PL的联动。

如何控制呢?有没有实例?和EMIO一起说(其实是可以查看SDK中的官方例程)。

参考链接-利用PS中的硬件SPI控制LCD

EMIO

资源还是PS部分的,只不过通过AXI将引脚引到PL端,再引到PL端的外设上面。占用PL端的资源很少,就是一些连接线。在配置界面中的IO peripheral可以自由配置,配置之后就Make Eternal,并生成HDL文件,然后就可以看到相关的管脚,并可以在SDK中直接进行编程控制。

AXI GPIO IP核

AXI GPIO是Xilinx提供的GPIO IP核,使用FPGA的逻辑资源生成的GPIO硬件电路,占用较多的PL端的资源。参考链接-通过AXI GPIO实现PS点亮PL端的led灯。

基本原理是:

- 添加zynq processing system和AXI GPIO IP核;

- 配置zynq的DDR、AXI GPIO的引脚(输入还是输出?双channel?等);

run block automation,此时会自动添加AXI相关通信模块,以便PS和PL的通信;- 将AXI GPIO的引脚

Make Eternal再重命名为LEDS; - 生成bitstream、导入到SDK,在后续SDK中就可以直接操作

LEDS进行开发(实际上是通过step3中自动添加的AXI通信模块实现的);

创建AXI类型的IP核

创建AXI类型IP核通过reg来实现PS控制PL:创建AXI Lite接口,会有slv_reg0变量,这个变量就是PS和PL进行通信的桥梁。参考链接-ZYNQ端PS访问PL端的reg寄存器,实现PS与PL数据交互,基本过程如下:

- 在tools中创建IP核,并选择AXI类型的IP核;

- 配置AXI IP核,主要是添加几个

reg,每个reg都是32bit; - 编辑AXI IP核,就是在生成的模板上加入自己的Verilog代码(通过

slv_reg0的值来执行相应的动作,比如点亮led,而slv_reg0则在SDK中直接控制,即通过slv_reg0作为桥梁,实现PS对PL端的LED的控制),此处看具体示例; - 在block desgin中添加已修改的AXI IP核,然后生成bitsream,导出到SDK中进行开发;

那如何实现AXI类型的IP核、AXI GPIO一起开发(如何连接?),目的如下:

- PS端有按键,通过按键在SDK代码中控制

slv_reg0;===(PS端的按键如何使用,应该是在IO peripheral中使用MIO,然后会有相应的port暴露出来) - 如何在AXI类型IP核的Verilog代码中通过

slv_reg0控制AXI GPIO?;(主要疑惑在这一步) - 即PS端的按键在SDK中控制

slv_reg0,slv_reg0在Verilog代码中控制AXI GPIO;

MIO、EMIO、AXI GPIO的理解

参考链接-MIO、EMIO、AXI GPIO的理解

如何保证是PS或PL单独运行

PL单独运行:Vivado中生成bitstream后下载到开发板,不包含zynq IP核

PS部分:Vivado中生成zynq IP核,并导出到SDK中进行开发,最后在SDK中下载(bitstream下载,arm部分代码的下载。PL部分没变化时,bitstream可以不用重复下载)。

疑惑

用硬件SPI驱动LCD的引脚约束问题

扩展板上的LCD是连接到PL端的。

参考链接-利用PS的IO资源模拟SPI驱动LCD:IO资源使用的是EMIO,位宽为5(spi相关引脚),最后需要引脚约束(这我能明白,因为EMIO本身就是处于PS与PL之间的部分)。

参考链接-利用PS的硬件SPI驱动LCD:硬件SPI使用的是MIO,在PS端;而LCD在PL端。硬件SPI是接在PS端的,为什么可以控制PL端的LCD?按道理MIO不是只能控制在PS端的外设吗?MIO又没有接到PL端。

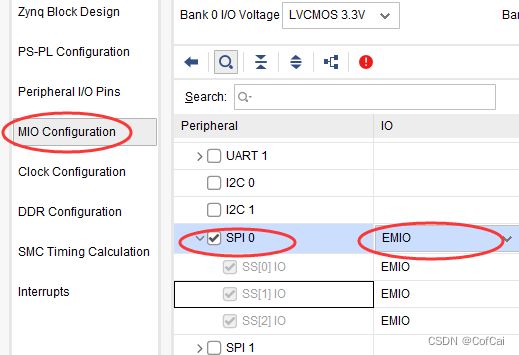

解答:MIO和EMIO在使用上几乎一样,则是EMIO接到FPGA/PL端更加灵活。

- 如果上图

SPI0选择的是MIO,则硬件SPI的引脚是在PS端,且一般是固定的,spi类型的LCD屏幕的引脚需要对应详解,PS端spi引脚是那些可以查阅相关手册; - 如果上图

SPI0选择的是EMIO(上图就是),则硬件SPI的引脚会通过EMIO引出PL端,并且是不固定的,需要自己进行约束,这也是EMIO更灵活的原因; - 上面1、2都是在说硬件SPI,也可用IO模拟SPI协议(自己编写程序模拟spi),也分为使用MIO和EMIO,道理一样;