m基于FPGA的64QAM调制解调、载波同步verilog实现

目录

1.算法描述

2.仿真效果预览

3.MATLAB核心程序

4.完整MATLAB

1.算法描述

64QAM(正交幅度调制),在使用同轴电缆的网络中,这种数字频率调制技术通常用于发送下行链路数据。64QAM在6mhz信道中,64QAM的传输速率非常高,最多可支持38.015mbps的峰值传输速率。然而,它对干扰信号很敏感,难以适应嘈杂的上行链路传输(从电缆用户到互联网)。参见QPSK、DQPSK、CDMA、S-CDMA、BPSK和VSB。

它具有调制效率高、对传输路径的信噪比要求高、带宽利用率高的特点,适合有线电视传输;QAM(DVB-C调制)在中国有线电视网络中得到广泛应用。QAM是一种联合幅度和相位调制技术。它利用载波的幅度和相位同时传输信息位。不同的幅度和相位表示不同的编码符号。因此,在相同的最小距离条件下,QAM星座可以容纳更多的星座点,以实现更高的频带利用率。

载波同步又称载波恢复(carrierrestoration),即在接收设备中产生一个和接收信号的载波同频同相的本地振荡(localoscillation),供给解调器作相干解调用。当接收信号中包含离散的载频分量时,在接收端需要从信号中分离出信号载波作为本地相干载波;这样分离出的本地相干载波频率必然与接收信号载波频率相同,但为了使相位也相同,可能需要对分离出的载波相位作适当的调整。若接收信号中没有离散载波分量,例如在2PSK信号中(“1” 和“0”以等概率出现时),则接收端需要用较复杂的方法从信号中提取载波。因此,在这些接收设备中需要有载波同步电路,以提供相干解调所需要的相干载波;相干载波必须与接收信号的载波严格地同频同相。

本系统几个设计要点:

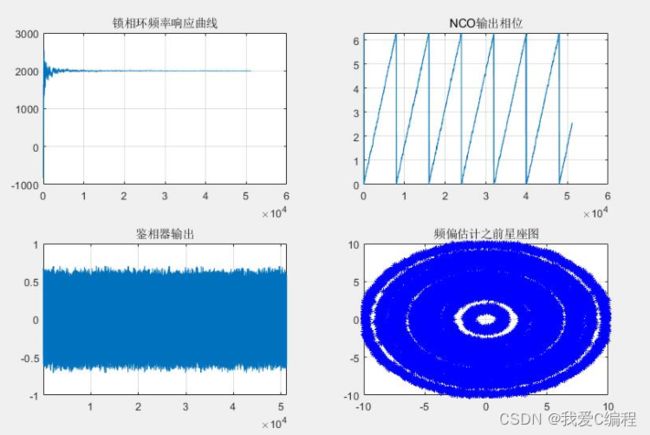

第一:环路滤波系数的分段更新,实现频率跟踪效果的稳定。当锁相环开始工作的时候,首先由一组较大的环路滤波系数实现频率的快速跟踪,然后由一组较小的环路系数,实现频率的稳定跟踪。

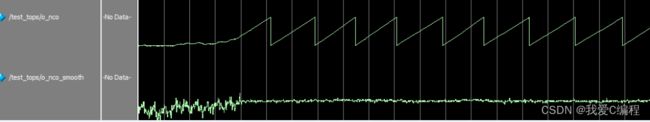

第二:环路平滑处理。

第三:同时进行鉴频和鉴相

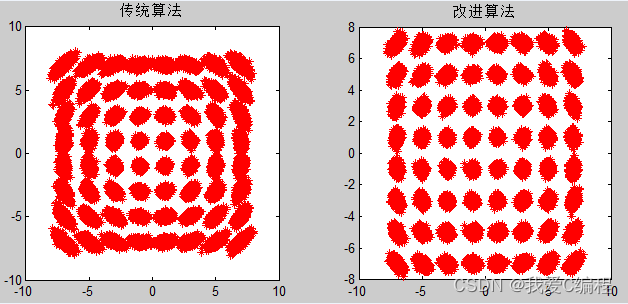

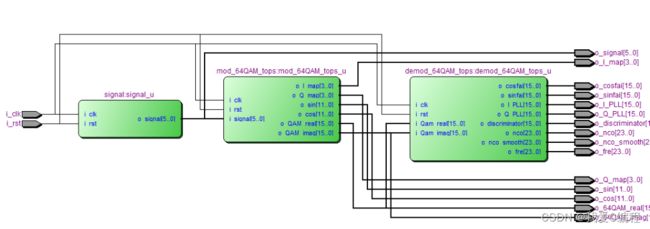

上面两个是性能上的改进,然后针对FPGA的设计,我们采用如下的改进设计构架。

第一:基于流水线的设计流程,使得载波同步算法能够以流的形式进行反馈工作;

第二:基于Cordic算法的NCO产生对应的SIN和COS。

2.仿真效果预览

算法仿真:MATLAB 2022a

FPGA设计:quartusii13.0

FPGA仿真:ModelSim-Altera 6.6d

3.MATLAB核心程序

`timescale 1ns / 1ps

module tops(

i_clk,

i_rst,

o_signal,

o_I_map,

o_Q_map,

o_sin,

o_cos,

o_64QAM_real,

o_64QAM_imag,

o_cosfai,

o_sinfai,

o_I_PLL,

o_Q_PLL,

o_discriminator,

o_nco,

o_nco_smooth,

o_fre

);

input i_clk;

input i_rst;

output [5:0] o_signal;

output signed[3:0] o_I_map;

output signed[3:0] o_Q_map;

output signed[11:0]o_sin;

output signed[11:0]o_cos;

output signed[15:0]o_64QAM_real;

output signed[15:0]o_64QAM_imag;

output signed[15:0]o_cosfai;

output signed[15:0]o_sinfai;

output signed[15:0]o_I_PLL;

output signed[15:0]o_Q_PLL;

output signed[15:0]o_discriminator;

output signed[23:0]o_nco;

output signed[23:0]o_nco_smooth;

output signed[23:0]o_fre;

signal signal_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_signal (o_signal)

);

//64QAM mod

mod_64QAM_tops mod_64QAM_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_signal (o_signal),

.o_I_map (o_I_map),

.o_Q_map (o_Q_map),

.o_sin (o_sin),

.o_cos (o_cos),

.o_QAM_real (o_64QAM_real),

.o_QAM_imag (o_64QAM_imag)

);

//64QAM demod

demod_64QAM_tops demod_64QAM_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Qam_real (o_64QAM_real),

.i_Qam_imag (o_64QAM_imag),

.o_cosfai (o_cosfai),

.o_sinfai (o_sinfai),

.o_I_PLL (o_I_PLL),

.o_Q_PLL (o_Q_PLL),

.o_discriminator (o_discriminator),

.o_nco (o_nco),

.o_nco_smooth (o_nco_smooth),

.o_fre (o_fre)

);

endmodule

01-124m4.完整MATLAB

V