- S7-300 400与S7-200 SMART PLC以太网通讯(S7协议)资源文件介绍

滑展妙Bernice

S7-300400与S7-200SMARTPLC以太网通讯(S7协议)资源文件介绍【下载地址】S7-300400与S7-200SMARTPLC以太网通讯S7协议资源文件介绍本资源文件详细解析了S7-300400与S7-200SMARTPLC通过以太网进行通讯的技术细节,涵盖硬件连接、软件配置及通讯调试等关键环节。通过学习,您将掌握S7协议在PLC通讯中的实际应用,提升自动化与电气工程领域的专业技能

- 从零构建智能ai语音助手:ESP32s3+Python+大语言模型实战指南

从零构建智能ai语音助手:ESP32s3+Python+大语言模型实战指南一、项目概述大家好!今天给大家带来一个干货满满的实战项目——基于ESP32S3硬件和Python后端的智能语音助手系统。这个项目将物联网技术与AI技术完美结合,打造一个可以实时对话、意图识别的智能语音交互系统。相比传统的离线语音系统只能识别固定命令词,我们这套系统可以:实现自然语言理解,支持多种表达方式无需预设固定命令词,更

- 穿透硅层:模电数电如何重塑你的编程基因

还债大湿兄

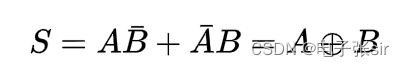

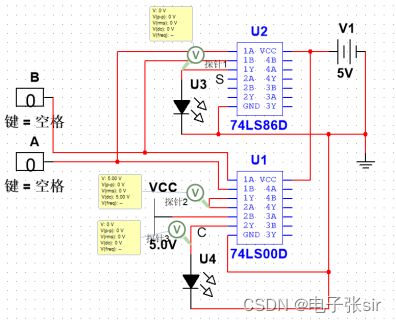

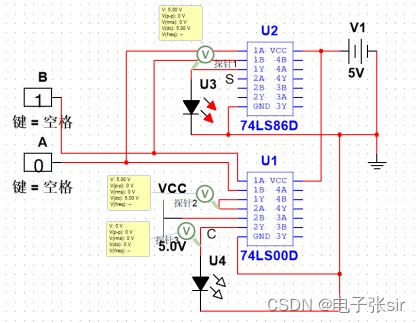

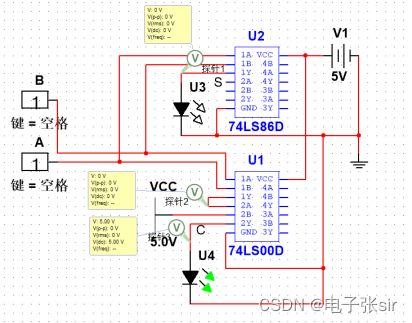

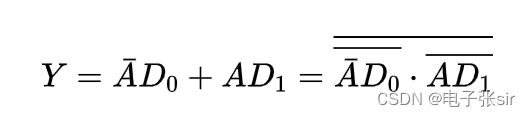

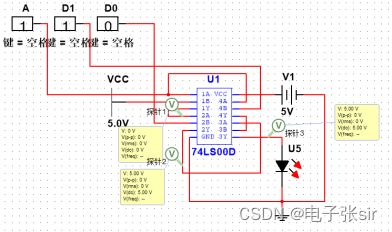

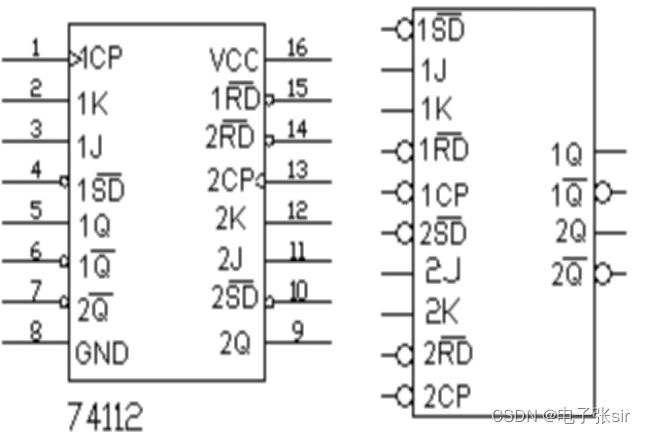

模电数电

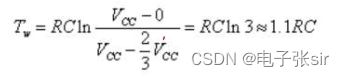

“不理解电子运动的程序员,永远在数字世界的表层流浪。”——吉恩·阿姆达尔(IBM360系统架构师)一、晶体管级视角:代码的物理载体1.CPU指令执行的硬件真相关键模电参数:阈值电压Vth:决定晶体管开关的电压临界点(典型值0.7V)跨导gm:栅压控制电流的能力(单位mS)米勒电容Cgd:限制开关速度的核心因素2.存储器操作的电子原理DRAM存储单元刷新过程://硬件级刷新伪代码voiddram_r

- VMware Fusion 13 Mac虚拟机

VMwareFusionPromac不仅能让你在Mac苹果电脑上运行Windows或Linux系统、使用非Mac平台的应用,而且还可以支持各种USB硬件设备。原文地址:VMwareFusion13Mac虚拟机

- 上位机软件开发

深圳市由你创科技

上位机开发c语言

上位机软件开发是指开发用于与下位机(如单片机、PLC、传感器、嵌入式设备等)进行通信、数据交互及控制的计算机端软件。这类软件通常需要实现数据采集、实时监控、参数配置、数据分析及可视化等功能。以下是开发上位机软件的关键步骤和技术要点:一、开发流程需求分析明确功能需求:数据采集频率、通信协议、界面交互、数据存储方式等。确定硬件接口:串口(RS232/RS485)、USB、TCP/IP、CAN总线、Mo

- 无缝矩阵支持音频分离带画面分割功能的全面解析

geffen1688

分类分布式

一、技术原理与实现方式1. 音频分离技术核心功能:HDMI无缝矩阵通过硬件或软件实现音频加嵌与分离功能,支持多设备音频的独立处理与增强。实现方式:音频加嵌:将外部音频信号(如麦克风、调音台)嵌入HDMI信号中传输,适用于家庭影院、会议系统等场景。音频分离:将HDMI信号中的音频独立输出至外部设备(如音响、音频处理器),支持多通道数字音频的交叉切换。技术支撑:采用32bitARM核心芯片(

- 使用STM32CubeMX在嵌入式系统中实现通过FMC读写SDRAM

程序员杨弋

嵌入式开发stm32嵌入式硬件单片机嵌入式

嵌入式系统中的存储器是非常重要的组成部分,为了满足大容量和高速度要求,SDRAM(SynchronousDynamicRandomAccessMemory)是常用的选择之一。本文将介绍如何使用STM32CubeMX配置硬件FMC(FlexibleMemoryController)以实现在STM32微控制器上读写SDRAM。1、STM32CubeMX配置FMC和SDRAM首先,我们需要打开STM32

- 多通路fpga 通信_FMC与FPGA双口ram通讯

weixin_39796752

多通路fpga通信

硬件环境:ARM+FPGA通过FMC互联,STM32F767和EP4CE15F23I7FMC设置,STM的系统时钟HCLK为216MHz1/*FMCinitializationfunction*/2voidMX_FMC_Init(void)3{4FMC_NORSRAM_TimingTypeDefTiming;56/**PerformtheNOR1memoryinitializationsequen

- system Verilog:clocking中定义信号为input和output的区别

加载-ing

systemverilog

在SystemVerilog中,clocking块用于定义时钟块,这通常用于描述时钟边缘和同步的输入/输出行为,特别是在测试平台和硬件接口描述中。在下述两个代码示例中,主要区别在于a被定义为一个input还是output。当a被定义为input时:systemverilogclockingcb@(posedgeclk);inputa;endclocking这意味着a是一个从被测试设计(DUT)到测

- [硬件接口]HDMI和DP 区别

DisplayPort和HDMI在FPGA应用场景的实现使用与区别概述DisplayPort(DP)和HDMI是两种主流的数字音视频接口,广泛应用于视频传输场景。在FPGA(现场可编程门阵列)应用中,DP和HDMI常用于视频处理、显示驱动和高带宽数据传输。本文档比较两者在FPGA实现中的使用方式、应用场景及主要区别,并以Markdown格式呈现。1.FPGA实现概述1.1DisplayPort在F

- [AXI] AXI Interconnect

AXIInterconnectIP详细介绍概述AXIInterconnect专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过模块化架构实现高效的数据路由、协议转换、数据宽度转换和时钟域转换,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联的场景,如多核处理器系统、视频处理、网络通信和硬件加速器

- 【亲测免费】 基于51单片机的温度报警系统:实时监测与智能报警

杭林菲

基于51单片机的温度报警系统:实时监测与智能报警【下载地址】基于51单片机的温度报警系统源代码论文本项目提供了一个基于51单片机的温度报警系统的完整资源,包括源代码和相关论文。该系统采用单片机、18B20温度传感器、数码管和蜂鸣器等硬件组件设计而成,能够实时监测环境温度,并在温度超出预设范围时发出报警信号项目地址:https://gitcode.com/open-source-toolkit/1f

- 基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码

基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码【下载地址】基于FPGA的Verilog电子密码锁设计资源文件基于FPGA和Verilog语言设计的电子密码锁项目,提供完整的硬件设计原理图、Verilog代码、仿真波形图和硬件描述文档。通过FPGA的可编程特性,实现密码设置、验证及锁定功能,适合学术研究、教学演示或个人兴趣学习。项目文件清晰,包含详细的使用说明,帮助用户快速

- 基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用

风吹麦很

fpga开发嵌入式

基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用快速傅里叶变换(FastFourierTransform,FFT)是一种重要的信号处理算法,在许多领域中都得到广泛的应用,例如通信系统、雷达技术、图像处理等。为了提高FFT的计算性能和实时性,将其设计为硬件加速器常常是一个明智的选择。本文将介绍基于现场可编程门阵列(Field-ProgrammableGateArray,FPGA)的FF

- 嵌入式系统:多路温度采集与环境报警监测

DevCyberX

嵌入式

概述:本文介绍了如何使用单片机、LM35温度传感器、ADC0832模数转换器和DS18B20数字温度传感器构建一个嵌入式系统,用于多路温度采集和环境报警监测。通过该系统,可以实时监测多个温度传感器的温度,并在温度超过设定阈值时触发报警。硬件组件:单片机:选择一款适合的单片机(如Arduino、STM32等)作为主控制器。LM35温度传感器:用于测量环境温度。ADC0832模数转换器:将模拟信号转换

- VMware Fusion 13 Mac虚拟机

fengyun2891

macosmac虚拟机

VMwareFusionmac不仅能让你在Mac苹果电脑上运行Windows或Linux系统、使用非Mac平台的应用,而且还可以支持各种USB硬件设备。原文地址:VMwareFusion13Mac虚拟机

- 智变时代|暴雨亮相第四届中国数据中心服务器与设备峰会

BAOYUCompany

人工智能

随着生成式AI浪潮席卷千行百业,算力基础设施的智能化升级已成为企业决胜未来的关键战场。在此背景下,第四届中国数据中心服务器与设备峰会于2025年7月1日在上海盛大开幕,聚焦大模型时代下服务器与设备的技术革新与应用落地。暴雨已经多次连续受邀参加本次峰会并在今年的峰会上发表了主题为《如何轻便应用大模型一体机》的演讲。暴雨产品营销总监李明指出:“当前DeepSeek等大模型应用仍然存在“硬件投资费用高昂

- ESP32 S3音频开发

1.音频硬件框架Codec:音频编解码芯片,一种低功耗单声道音频编解码器,包含单通道ADC、单通道DAC、低噪声前置放大器、耳机驱动器、数字音效、模拟混音和增益功能。它通过I2S和I2C总线与ESP32-S3-WROOM-1模组连接,以提供独立于音频应用程序的。PA:音频功率放大器,用于放大来自音频编解码芯片的音频信号,以驱动扬声器。2.音频软件框架ESP32提供了几个简单的高级API,可以参考例

- ESP32-S3 I2S音频开发实战指南

薛慕昭

音视频

目录前言I2S简介TDM通信模式(标准)PDM通信模式.对比总结为什么要学习I2SPCM原始数据I2S录制声音I2S播放声音WAV音频WAV文件头结构(44字节)解析wav格式数据struct.unpack的基本用法格式化字符串(fmt)示例1:解析单个值示例2:解析多个值示例3:解析混合类型示例4:解析字符串示例5:解析WAV文件头注意事项总结实操演练保存wav格式数据结语前言在智能硬件和物联网

- 【esp32-s3】7.2 I2S——播放wav文件

飞鸟厌鱼

esp32esp32s3

文章目录1前言2硬件3代码4结果1前言本章实现了播放和录制功能。2硬件3代码/*I2SDigitalMicrophoneRecordingExampleThisexamplecodeisinthePublicDomain(orCC0licensed,atyouroption.)Unlessrequiredbyapplicablelaworagreedtoinwriting,thissoftware

- 硬件产品研发管理工具实战指南

前端知识教程

一、硬件研发的三大核心挑战需求传递失真现实问题:市场需求→工程师理解→设计实现,关键信息层层丢失研究证明:需求每经过1次传递,关键参数偏离风险增加37%——《硬件需求工程中的信息衰减》(麻省理工硕士论文,2023)典型案例:客户要求“防水IP68”→设计实现为“防泼溅”→样机泡水测试失败BOM管理混乱数据真相:元器件参数、供应商、替代料管理缺失导致:→38%项目因物料错误超支→采购延误平均4.5天

- iOS苹果和Android安卓测试APP应用程序的区别差异

iOS苹果和Android安卓在测试APP应用程序时存在显著差异,这些差异主要源于系统架构、生态规则、设备多样性等多重因素。以下是具体的区别:一、操作系统与生态iOS是苹果公司的封闭移动操作系统,而Android是谷歌开发的开放源码移动操作系统。iOS设备生态系统相对封闭,仅限于苹果自家设备,硬件和软件高度整合;Android设备生态系统则相对开放,存在多种品牌和型号,硬件和软件组合多样性大。二、

- 选择护盾云独立服务器还是护盾云高防服务器建站

hudun9587

服务器运维

选择独立服务器还是高防服务器建站,需结合业务场景、安全需求、成本预算及技术能力综合决策。以下从核心差异、适用场景、成本效益及选型策略四个维度展开分析,并通过行业案例与数据支撑结论:一、核心差异对比:独立服务器vs高防服务器1.安全防御能力硬件资源完全独占(CPU/内存/带宽),但默认无专用防御设备,需依赖软件防火墙(如iptables、CSF)或额外采购硬件防护设备(如F5、FortiGate)。

- Proface GP系列HMI产品故障排查与解决指南

Compass宁

本文还有配套的精品资源,点击获取简介:本文档旨在汇总ProfaceGP系列人机界面(HMI)产品在工业自动化领域应用中可能遇到的各类技术问题及其解决方案。包括但不限于硬件故障、电源问题、通信故障、软件配置错误、画面显示异常、数据记录问题、设备兼容性、故障诊断、网络连接及安全更新等方面的问题。提供详细的排查步骤和解决策略,帮助用户快速定位并修复问题,确保设备的正常运行。1.【ProfaceGP】系列

- 浅谈指针,内存与指针做函数参数

2501_90124553

C语言

一、概念1、指针==地址指针的目的是为了进行寻址操作,找到对应的内存2、内存(1)虚拟内存:实际是硬盘的一块区域(2)物理内存:计算机中安装的硬件内存(比如:内存条)RAM:随机存储器,用于临时存储数据,读写速度快(3)虚拟内存内存总大小:4G内存单元:每个内存单元大小节(byte)内存单元总数:4*1024*1024*1024内存块:地址空间连续的多个内存单元地址:每个内存单元都有一个对应的地址

- 1. CentOS系统安装

君迁棪木

CentOS7复习笔记linux

CentOS系统安装SSH远程连接:安装centos系统新建虚拟机——>自定义——>硬件兼容性:workstation15.x——>稍后安装操作系统——>Linux,CentOS764位——>名称位置随意——>NAT模式,新建虚拟磁盘——>拆分成多个文件——>自定义硬件——>新CD/DVD,使用IOS映像文件——>完成,开启虚拟机根据虚拟网络类型配置IP地址Nat网络类型:输入命令:ipa##检查

- 驱动开发系列59- 再述如何处理硬件中断

黑不溜秋的

GPU驱动专栏驱动开发

目录一:硬件中断以及内核是如何处理中断的二:分配硬件IRQ1.使用request_irq()分配中断处理程序2.释放IRQ3.设置中断标志4.理解电平触发与边沿触发中断三:实现中断处理程序四:使用线程中断模型五:启用/禁用中断六:查看所有已分配的中断线七:理解和使用上半部和下半部八:总结在本文中,我们将重点讨论编写设备驱动程序时一个非常关键的方面:什么是硬件中断,更重要的是,作为驱动开发者,你该如

- Java安全之JNI

java软件安全

介绍JNI(JavaNativeInterface)是一种允许Java程序与本地代码(如C或C++)互操作的接口技术。通过JNI,Java程序能够调用本地代码,实现性能和功能上的优化,克服Java在某些场景下的内存管理和执行效率瓶颈。它使得开发者可以在Java应用中集成底层操作系统功能或使用已存在的高效本地库,从而提升应用的执行速度或访问硬件资源的能力。JNI基本知识本地库生命周期阶段触发条件关键

- 【NVIDIA-H100】基于 nvidia-smi 数据H100 GPU 功耗异常深度分析与解决方案

清风 001

AI大模型底层建设人工智能gpu算力

目录一、引言二、GPU功耗与温度管理基础逻辑(一)GPU温度调控机制(二)功耗与温度的关联逻辑三、3号H100GPU异常数据深度拆解(一)正常卡与异常卡数据对比(核心指标)(二)异常指标的物理意义四、功耗低的根源分析(多维度拆解)(一)硬件故障维度1.温度传感器故障(GPU核心)2.显存散热模块失效3.供电电路异常(二)软件与驱动维度1.NVIDIA驱动版本兼容性问题2.系统级电源管理策略冲突(三

- 基于Web门户架构的监狱内网改版实践:值班排班系统设计与信创适配探讨

bbsh2099

方案与思考WebFuture

面向监狱内网改版场景的门户平台技术架构与智能排班实践关键词:监狱内网改版、监狱内部网站改版、值班排班系统、信创适配、智能门户架构一、场景背景与问题分析在信创国产化、等级保护合规、政务集约化趋势持续推进的背景下,传统监狱内部网站普遍面临如下问题:架构陈旧,安全漏洞频出,难以满足等级保护三级要求;不兼容国产软硬件栈,不支持国密算法与国产数据库;缺乏智能化排班系统,无法满足“岗哨轮班制”等典型排班制度;

- windows下源码安装golang

616050468

golang安装golang环境windows

系统: 64位win7, 开发环境:sublime text 2, go版本: 1.4.1

1. 安装前准备(gcc, gdb, git)

golang在64位系

- redis批量删除带空格的key

bylijinnan

redis

redis批量删除的通常做法:

redis-cli keys "blacklist*" | xargs redis-cli del

上面的命令在key的前后没有空格时是可以的,但有空格就不行了:

$redis-cli keys "blacklist*"

1) "blacklist:12:

[email protected]

- oracle正则表达式的用法

0624chenhong

oracle正则表达式

方括号表达示

方括号表达式

描述

[[:alnum:]]

字母和数字混合的字符

[[:alpha:]]

字母字符

[[:cntrl:]]

控制字符

[[:digit:]]

数字字符

[[:graph:]]

图像字符

[[:lower:]]

小写字母字符

[[:print:]]

打印字符

[[:punct:]]

标点符号字符

[[:space:]]

- 2048源码(核心算法有,缺少几个anctionbar,以后补上)

不懂事的小屁孩

2048

2048游戏基本上有四部分组成,

1:主activity,包含游戏块的16个方格,上面统计分数的模块

2:底下的gridview,监听上下左右的滑动,进行事件处理,

3:每一个卡片,里面的内容很简单,只有一个text,记录显示的数字

4:Actionbar,是游戏用重新开始,设置等功能(这个在底下可以下载的代码里面还没有实现)

写代码的流程

1:设计游戏的布局,基本是两块,上面是分

- jquery内部链式调用机理

换个号韩国红果果

JavaScriptjquery

只需要在调用该对象合适(比如下列的setStyles)的方法后让该方法返回该对象(通过this 因为一旦一个函数称为一个对象方法的话那么在这个方法内部this(结合下面的setStyles)指向这个对象)

function create(type){

var element=document.createElement(type);

//this=element;

- 你订酒店时的每一次点击 背后都是NoSQL和云计算

蓝儿唯美

NoSQL

全球最大的在线旅游公司Expedia旗下的酒店预订公司,它运营着89个网站,跨越68个国家,三年前开始实验公有云,以求让客户在预订网站上查询假期酒店时得到更快的信息获取体验。

云端本身是用于驱动网站的部分小功能的,如搜索框的自动推荐功能,还能保证处理Hotels.com服务的季节性需求高峰整体储能。

Hotels.com的首席技术官Thierry Bedos上个月在伦敦参加“2015 Clou

- java笔记1

a-john

java

1,面向对象程序设计(Object-oriented Propramming,OOP):java就是一种面向对象程序设计。

2,对象:我们将问题空间中的元素及其在解空间中的表示称为“对象”。简单来说,对象是某个类型的实例。比如狗是一个类型,哈士奇可以是狗的一个实例,也就是对象。

3,面向对象程序设计方式的特性:

3.1 万物皆为对象。

- C语言 sizeof和strlen之间的那些事 C/C++软件开发求职面试题 必备考点(一)

aijuans

C/C++求职面试必备考点

找工作在即,以后决定每天至少写一个知识点,主要是记录,逼迫自己动手、总结加深印象。当然如果能有一言半语让他人收益,后学幸运之至也。如有错误,还希望大家帮忙指出来。感激不尽。

后学保证每个写出来的结果都是自己在电脑上亲自跑过的,咱人笨,以前学的也半吊子。很多时候只能靠运行出来的结果再反过来

- 程序员写代码时就不要管需求了吗?

asia007

程序员不能一味跟需求走

编程也有2年了,刚开始不懂的什么都跟需求走,需求是怎样就用代码实现就行,也不管这个需求是否合理,是否为较好的用户体验。当然刚开始编程都会这样,但是如果有了2年以上的工作经验的程序员只知道一味写代码,而不在写的过程中思考一下这个需求是否合理,那么,我想这个程序员就只能一辈写敲敲代码了。

我的技术不是很好,但是就不代

- Activity的四种启动模式

百合不是茶

android栈模式启动Activity的标准模式启动栈顶模式启动单例模式启动

android界面的操作就是很多个activity之间的切换,启动模式决定启动的activity的生命周期 ;

启动模式xml中配置

<activity android:name=".MainActivity" android:launchMode="standard&quo

- Spring中@Autowired标签与@Resource标签的区别

bijian1013

javaspring@Resource@Autowired@Qualifier

Spring不但支持自己定义的@Autowired注解,还支持由JSR-250规范定义的几个注解,如:@Resource、 @PostConstruct及@PreDestroy。

1. @Autowired @Autowired是Spring 提供的,需导入 Package:org.springframewo

- Changes Between SOAP 1.1 and SOAP 1.2

sunjing

ChangesEnableSOAP 1.1SOAP 1.2

JAX-WS

SOAP Version 1.2 Part 0: Primer (Second Edition)

SOAP Version 1.2 Part 1: Messaging Framework (Second Edition)

SOAP Version 1.2 Part 2: Adjuncts (Second Edition)

Which style of WSDL

- 【Hadoop二】Hadoop常用命令

bit1129

hadoop

以Hadoop运行Hadoop自带的wordcount为例,

hadoop脚本位于/home/hadoop/hadoop-2.5.2/bin/hadoop,需要说明的是,这些命令的使用必须在Hadoop已经运行的情况下才能执行

Hadoop HDFS相关命令

hadoop fs -ls

列出HDFS文件系统的第一级文件和第一级

- java异常处理(初级)

白糖_

javaDAOspring虚拟机Ajax

从学习到现在从事java开发一年多了,个人觉得对java只了解皮毛,很多东西都是用到再去慢慢学习,编程真的是一项艺术,要完成一段好的代码,需要懂得很多。

最近项目经理让我负责一个组件开发,框架都由自己搭建,最让我头疼的是异常处理,我看了一些网上的源码,发现他们对异常的处理不是很重视,研究了很久都没有找到很好的解决方案。后来有幸看到一个200W美元的项目部分源码,通过他们对异常处理的解决方案,我终

- 记录整理-工作问题

braveCS

工作

1)那位同学还是CSV文件默认Excel打开看不到全部结果。以为是没写进去。同学甲说文件应该不分大小。后来log一下原来是有写进去。只是Excel有行数限制。那位同学进步好快啊。

2)今天同学说写文件的时候提示jvm的内存溢出。我马上反应说那就改一下jvm的内存大小。同学说改用分批处理了。果然想问题还是有局限性。改jvm内存大小只能暂时地解决问题,以后要是写更大的文件还是得改内存。想问题要长远啊

- org.apache.tools.zip实现文件的压缩和解压,支持中文

bylijinnan

apache

刚开始用java.util.Zip,发现不支持中文(网上有修改的方法,但比较麻烦)

后改用org.apache.tools.zip

org.apache.tools.zip的使用网上有更简单的例子

下面的程序根据实际需求,实现了压缩指定目录下指定文件的方法

import java.io.BufferedReader;

import java.io.BufferedWrit

- 读书笔记-4

chengxuyuancsdn

读书笔记

1、JSTL 核心标签库标签

2、避免SQL注入

3、字符串逆转方法

4、字符串比较compareTo

5、字符串替换replace

6、分拆字符串

1、JSTL 核心标签库标签共有13个,

学习资料:http://www.cnblogs.com/lihuiyy/archive/2012/02/24/2366806.html

功能上分为4类:

(1)表达式控制标签:out

- [物理与电子]半导体教材的一个小问题

comsci

问题

各种模拟电子和数字电子教材中都有这个词汇-空穴

书中对这个词汇的解释是; 当电子脱离共价键的束缚成为自由电子之后,共价键中就留下一个空位,这个空位叫做空穴

我现在回过头翻大学时候的教材,觉得这个

- Flashback Database --闪回数据库

daizj

oracle闪回数据库

Flashback 技术是以Undo segment中的内容为基础的, 因此受限于UNDO_RETENTON参数。要使用flashback 的特性,必须启用自动撤销管理表空间。

在Oracle 10g中, Flash back家族分为以下成员: Flashback Database, Flashback Drop,Flashback Query(分Flashback Query,Flashbac

- 简单排序:插入排序

dieslrae

插入排序

public void insertSort(int[] array){

int temp;

for(int i=1;i<array.length;i++){

temp = array[i];

for(int k=i-1;k>=0;k--)

- C语言学习六指针小示例、一维数组名含义,定义一个函数输出数组的内容

dcj3sjt126com

c

# include <stdio.h>

int main(void)

{

int * p; //等价于 int *p 也等价于 int* p;

int i = 5;

char ch = 'A';

//p = 5; //error

//p = &ch; //error

//p = ch; //error

p = &i; //

- centos下php redis扩展的安装配置3种方法

dcj3sjt126com

redis

方法一

1.下载php redis扩展包 代码如下 复制代码

#wget http://redis.googlecode.com/files/redis-2.4.4.tar.gz

2 tar -zxvf 解压压缩包,cd /扩展包 (进入扩展包然后 运行phpize 一下是我环境中phpize的目录,/usr/local/php/bin/phpize (一定要

- 线程池(Executors)

shuizhaosi888

线程池

在java类库中,任务执行的主要抽象不是Thread,而是Executor,将任务的提交过程和执行过程解耦

public interface Executor {

void execute(Runnable command);

}

public class RunMain implements Executor{

@Override

pub

- openstack 快速安装笔记

haoningabc

openstack

前提是要配置好yum源

版本icehouse,操作系统redhat6.5

最简化安装,不要cinder和swift

三个节点

172 control节点keystone glance horizon

173 compute节点nova

173 network节点neutron

control

/etc/sysctl.conf

net.ipv4.ip_forward =

- 从c面向对象的实现理解c++的对象(二)

jimmee

C++面向对象虚函数

1. 类就可以看作一个struct,类的方法,可以理解为通过函数指针的方式实现的,类对象分配内存时,只分配成员变量的,函数指针并不需要分配额外的内存保存地址。

2. c++中类的构造函数,就是进行内存分配(malloc),调用构造函数

3. c++中类的析构函数,就时回收内存(free)

4. c++是基于栈和全局数据分配内存的,如果是一个方法内创建的对象,就直接在栈上分配内存了。

专门在

- 如何让那个一个div可以拖动

lingfeng520240

html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/1999/xhtml

- 第10章 高级事件(中)

onestopweb

事件

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- 计算两个经纬度之间的距离

roadrunners

计算纬度LBS经度距离

要解决这个问题的时候,到网上查了很多方案,最后计算出来的都与百度计算出来的有出入。下面这个公式计算出来的距离和百度计算出来的距离是一致的。

/**

*

* @param longitudeA

* 经度A点

* @param latitudeA

* 纬度A点

* @param longitudeB

*

- 最具争议的10个Java话题

tomcat_oracle

java

1、Java8已经到来。什么!? Java8 支持lambda。哇哦,RIP Scala! 随着Java8 的发布,出现很多关于新发布的Java8是否有潜力干掉Scala的争论,最终的结论是远远没有那么简单。Java8可能已经在Scala的lambda的包围中突围,但Java并非是函数式编程王位的真正觊觎者。

2、Java 9 即将到来

Oracle早在8月份就发布

- zoj 3826 Hierarchical Notation(模拟)

阿尔萨斯

rar

题目链接:zoj 3826 Hierarchical Notation

题目大意:给定一些结构体,结构体有value值和key值,Q次询问,输出每个key值对应的value值。

解题思路:思路很简单,写个类词法的递归函数,每次将key值映射成一个hash值,用map映射每个key的value起始终止位置,预处理完了查询就很简单了。 这题是最后10分钟出的,因为没有考虑value为{}的情

![]()