04_Initial Design/Floorplan实操2021-09-08上午

一共有7步,做完就可以去验证了

导入design→摆放stdcell→各个步骤

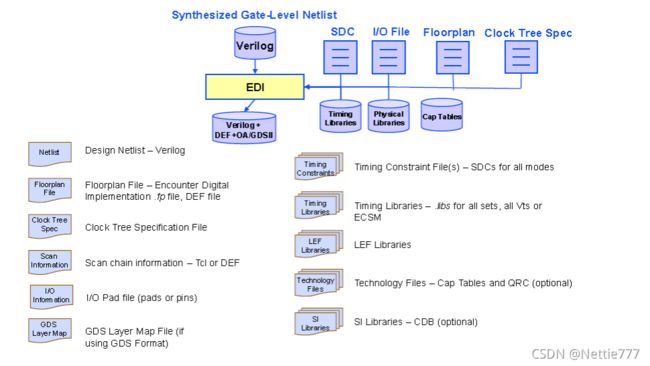

一、Import design

建立view definition文件

Foundry timing sign-off reference:

每套lib根据PVT的不同有8个lib

library set + RC tech file → delay corner

delay corner + sdc → analysis view

6lib set

6

12

一共24个 考虑到了所有PVT和RC corner

通过sign-off的第2列可以知道需要的lib set有哪些

通过第3列可以知道需要的RC corner 有哪些

组合2、3列即可得出delay corner有哪些

第一步:create_library_set:一共6个

第二步:create_rc_corner:一共6个

第三步:create_delay_corner:

第四步:create_constraint_mode:

delay Corner+constraint→view

第五步:create_analysis_view:

第六步:set_analysis_view:

图形化界面

二、init design

首先需要save一下

check design

◆ Netlist check:

check unique 检查网表中的module是否都是unique的

checkDesign –netlist 检查网表有没有input flotining

◆ LEF check:

checkDesign –physicalLibrary 检查有没有缺少LEF,或者LEF是否完整

◆ Timing lib check:

checkDesign –timingLibrary 检查有没有缺少lib

check_instance_library_in_view 检查每个analysis view的inst是否缺少lib

◆ sdc check:

check_timing -verbose > check_timing.rpt 检查sdc约束是否完整

◆ Report timing :

timeDesign –preplace –expandedViews 检查initial timing是否clean

检查Import Design过程中的log,注意出现的waring和error,知道原因,判断能否waive

三、Floorplan

衡量芯片的三大指标: Power、Performance、Area

➢ 布图规划与布局的合理与否直接关系到芯片的时序收敛、布线通畅、

电源稳定、以及良品率,因此在整个芯片设计中占据重要地位。

floorplan会影响placement, timing and routing.

➢ 布图规划的主要内容包含了对芯片大小(die size)的规划、芯片设

计输入输出(I/O)单元的规划、大量硬核或模块(hard core,

block)的规划等。

目标

• Partition design to physical blocks. ( partition)

• Decides the location of IO pads, number/location of power pads, and

power distribution . (power)

• Minimize congestion and the critical path delay. (routing & Performance)

• chip摆的尽可能的紧密,芯片小了时序也好收敛. (Area)

方法

Step 1 :determine the die size

Step 2 :根据PPA表格摆放IO cell

Step 3 :摆放IPs、special SRAM/module according to custom requirement.

Step 4 : 分析每个module之间的关系

Step 5 : 分析每个SRAM之间的关系

Step 6 :根据关系把SRAM摆在一起

Step 7 : 检查floorplan

Step 8 : Power planning

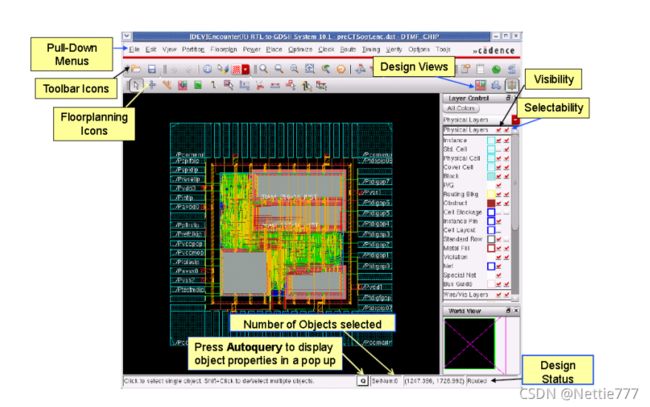

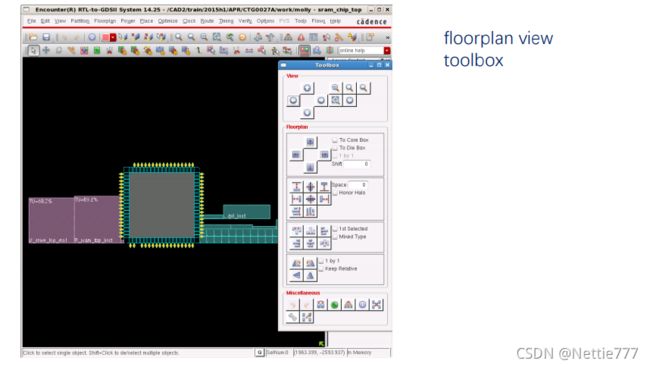

三种view方式

如何用这个工具摆floorplan

一点快捷键

move就是M

resixe就是s

reshape就是r

create ruler就是k

placement blockage

design broswer整个电路的树状图

一些highlight

第一步:决定size大小

12nm有off-grid的问题,要size的整数倍来定整个cell的大小

第二步:根据PPA cell摆放IO

PPA CHECK:

对于非signal io(power、break io等),如果PPA 中有,

design中没有,可先自己添加,没有instname 也可先自己添

加,再反馈给designer 确认。

• 对于signal io ,PPA中有,design中没有,反馈给designer

• 对于design 中有,PPA 中没有的,反馈给designer

Requirment :

是否有IO之间的spacing rule

是否添加IO filler

第三步:根据custom requirement摆放IP、特殊的SRAM/Moudule

要求 :

• Halo around MEM

• Halo around IPs

• location

Halo: 人为约束,禁止摆放std cell,随block 一起移动

IP的要求

Ex : halo 20um 独立power 供电

第四步:Analyze the relations between every module

同一个module的SRAM是摆放在一起的

第五步:分析每个SRAM之间的关系

第六步:根据关系把SRAM摆在一起

You can quickly access commonlyused commands during the

floorplanning stage with thefloorplan toolbox.

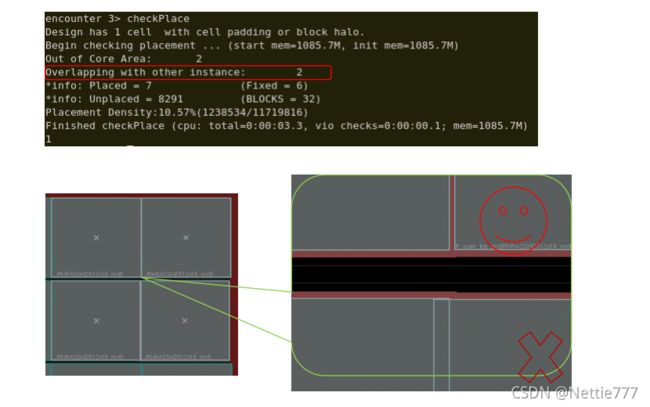

第七步:检查floorplan

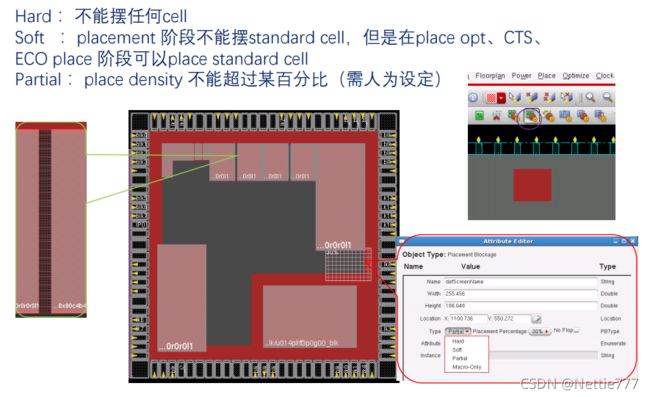

Blockage

Hard :不能摆任何cell

Soft :placement 阶段不能摆standard cell,但是在place opt、CTS、

ECO place 阶段可以place standard cell

Partial :place density 不能超过某百分比(需人为设定)

physical constraint

Physical constrains ,分为三种,fence、region、guide。是人为添加 的物理约束,作用对象是module(也可以是instance group)。

限制自己的stdcell能不能出,别的stdcell能不能进

- Guide (向导约束):

可进可出 ,属于该group的cell ,可放在guide区域以内,也可放在区域以外; - Region (区域约束) :

可进不可出, 属于该group的cell,只能放在region区域内,该区域也可放置group 以外的cell; - Fence (限制区域) :

不可进不可出, 属于该group的cell,只能放在fence区域内,且不允许其他cell放入该区域。

用小剪刀工具剪成异形

adjustment

• Adjust SRAMs location、direction、spacing(可以放buffer修时序,但是不能放function cell)

• 创建placement blockage ( hard、soft、partial)

• 创建place guide、region、fence

• set module density

• Add inst/cell padding

• Change nondefault rule

• Review power plan,if power IR allows

• Review the high pin count cell

• Design issues

• Chip resizing

• Add routing metal

例子

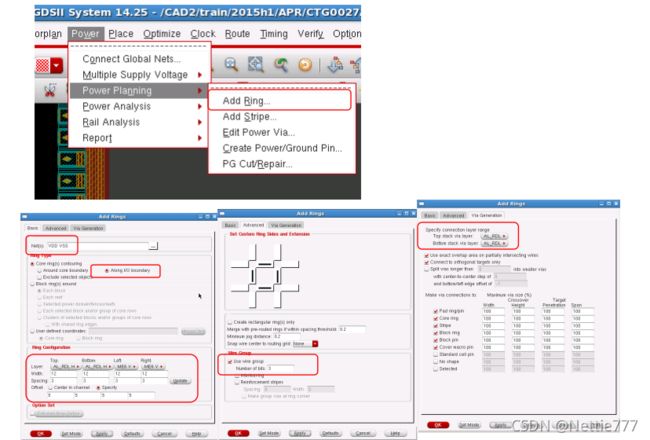

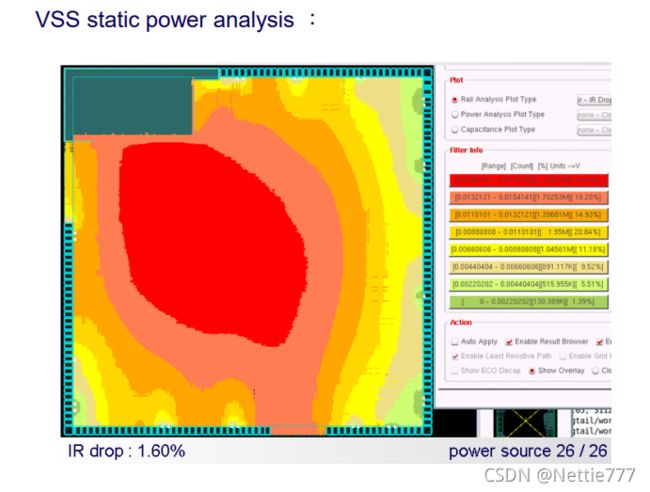

四、PowerPlan

目的:

- 将power pad和 logic cells’ VDD/VSS用金属线连接

- Minimize voltage drop

- Minimize ground bounce

- VDD voltage drop和VSS ground bounce之和小于5%*VDD. (Static)

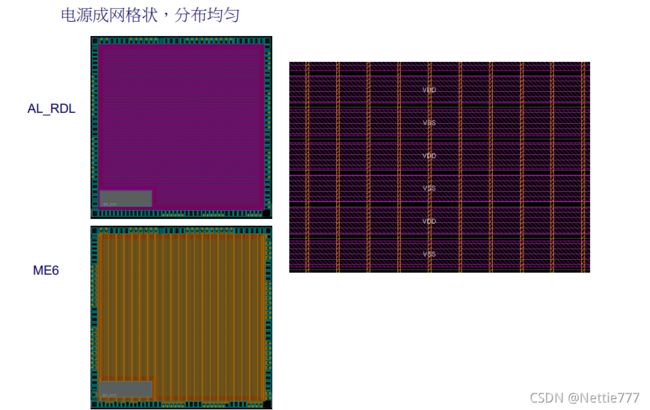

方法:

• Power 连接关系确定,global net connect

• IO power ring

• Core power ring

• IO cell power 与 core power ring 连接

• Core power stripe横横竖竖的条条

• Core std cell power followpin(统一高度后连一起的VDD和VSS)

• 添加power via —— 连接power stripe和power followpin

• Check (verify)

global net connect

power 连接关系及作用:

| 名称 | 解释 |

|---|---|

| VDD_PLL_A | PLL analog ground |

| VDD_PLL_D | PLL digital power |

| VSS_PLL_D | PLL digital ground |

| VDD_IO | IO cell power |

| VSS_IO | IO cell ground |

| VDD | core cell power |

| VSS | core cell ground |

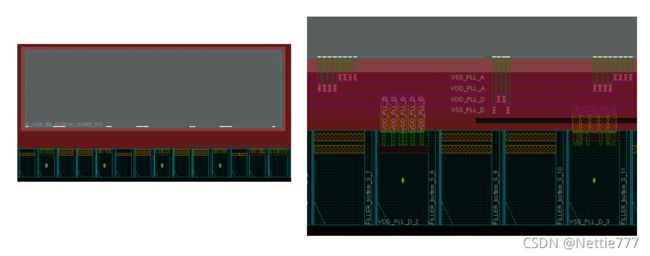

IO Power ring

IO cell & core power ring

core power stripe 细密比较好 但是小心超过density上限

打的时候不要孔,最后一起

VDD+VSS是一组set,所以set_to_set就是上一个VDD去下一个VDD

Block :

M4 出power pin shape,和M6 stripe 同向,

可拉M5 横向stripe 来衔接M6 M4 来给block 供电。

floorpin

IP Power

IP power : pll 有出M3 power pin

可根据出pin 位置,选择合适方式接至IP power pad

power via

verify

Save floorplan information:

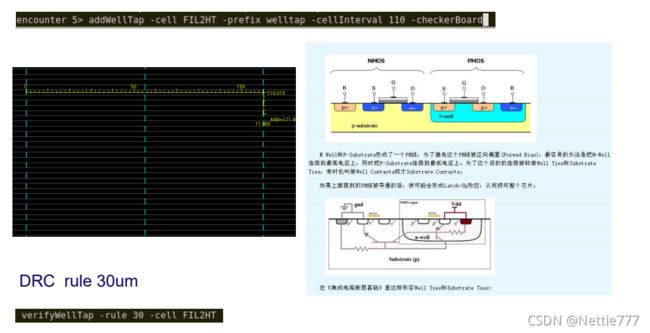

Add well tap cell

每个stdcell是不带well tap的 没有给衬底供电的,需要在多少um内加一个

Add end cap cell

保护作用,主要是为了避免PSE ( poly space effect)和OSE(od space effect)造成的影响,不能让poly和OD周围太空,不对称,密度太低,因此通过加endcap来满足均匀的密度, 使得std cell 周围的环境一致。

stdcell的上下左右边界处加上,保证每个stdcell的四周都是stdcell

补充:名词解释

• pad (输入输出)接口单元,接口

• P & R 布局布线

• partition 分割分块

• path 路径:

critical path 关键路径

false path 虚假 路径

min/max path 最快/最慢路径

multicycle path 多周期路径

• pin (输入输出)接口,端口

• pitch 布线(网格)间距

• place placement 布局

• block、cell、IO placement 模块布局,单元布局,IO 布局

• PLL phase-locked loop 锁相环

• PMOS p-channel MOS p型沟道金属氧化物半导体

• polysilicon 多晶硅

• polyside 多晶硅化物

• power 功耗

dynamic power 动态功耗

leakage power 泄漏功耗

low power 低功耗

static power 静态功耗

• powerplan ,powerplanning 电源规划

• followpins 电源端口连接

• power ring 电源环

• power stripe 电源带

• power trunk 电源干线

• PPA ,performance,power,area 性能,功耗,面积

• PSO ,power shutoff 电源关断

• PTV ,process temperature voltage 工艺温度电压(条件)

• RAM random access memory 随机存储器

• register 寄存器

• ROM read-only memory 只读存储器

• Route,routing 布线(线路),布线过程

• Clock routing 时钟布线

• detail routing 详细布线

• Global routing 全局布线

• Nano routing 纳米布线

• Routing track 线径,布线线路

• Special routing 特殊布线

• Timing-driven routing 时序控制布线

• Tial route 实验布线

• RTL register-transfer level 寄存器传输级

• SDC standard design constraints 标准设计约束

• SDF standard delay format 标准延时格式

• Sequential logic circuit 时序逻辑电路

• Setup,setup time 建立时间

• SI,signal integrity 信号完整性

• Skew 偏差

useful skew 有用偏差

• Slack (时间)松弛

• SoC ,SOC, system-on-chip 片上系统

• SPEF standard parasitic exchange format 标准寄生参数交换格式

• SPF standard parasitic format 标准寄生参数格式

• SRAM static random-access memory 静态随机存储器

• STA static timing analysis 静态时序分析

• substrate 衬底

• Synthesis (逻辑)综合

• Tape-out 出带

• transition transition time 转换(时间)

• uncertainty (时钟信号)不确定性

• violation 违反

• wafer 晶圆

• WC,wc,worst-case 最差条件

• WNS,worst negative slack 最坏负剩余时间

• Time,timing,时间,时序

check timing,timing check 检查时序

critical timing 关键时序

time borrowing 时序(间)借用

timing budgeting 时序(间)预算