DDR4时序标准规范(二)

DDR4时序标准规范

- 编码模式寄存器(MRx)

-

- 模式寄存器0(MR0)

-

- CAS延迟

- 测试模式TM

- 写恢复(WR)/读预充

- DLL(延时锁相环)复位

- 模式寄存器1(MR1)

-

- DLL(延时锁相环)使能/禁用

- ODT RTT(标称)值

- AL(附加延迟)

- 写入均衡

- 终端数据选通(TDQS)

- 模式寄存器2(MR2)

-

- CAS写延迟

- 低功耗自动自刷新

- 动态ODT

- 写循环冗余校验数据(CRC)总线

- 模式寄存器3(MR3)

-

- 多用途寄存器

- 当CRC/DM使能时,WRITE命令时延

- 精细化刷新频率间隔设置

- 温度传感器状态

- Per-DRAM可寻址能力

- Gear-down减速模式

- 模式寄存器4(MR4)

-

- 硬/软件封装后修复

- 写/读序言

- 读序言训练

- 温控刷新

- 命令地址延迟

- 内部VREF监视器

- 最大节电模式

- 模式寄存器5(MR5)

-

- 数据总线反转(DBI)

- 数据掩码(DM)

- CA校验持续模式

- 用于断电的ODT输入缓冲区

- CA校验状态位

- CRC状态位

- CA校验延迟模式

- 模式寄存器6(MR6)

编码模式寄存器(MRx)

为了应用程序的灵活性,各种功能、特性和模式可在设备提供的7个模式寄存器(MRn)中进行编程,作为用户定义的变量,必须通过模式寄存器集(MRS)命令进行编程。因为模式寄存器的默认值没有定义,模式寄存器的内容必须完全初始化和/或重新初始化;也就是说,它们必须在上电和/或重新设置后才能正常运行。模式寄存器的内容可以通过在正常操作期间重新执行MRS命令来更改。在编程模式寄存器时,即使用户选择只修改MRS字段的一个子集,也必须在MRS命令发出时重新定义所访问的模式寄存器中的所有地址字段。MRS和DLL RESET命令不影响存储空间内容,这意味着这些命令可以在上电后的任何时间执行,而不会影响存储空间内容。

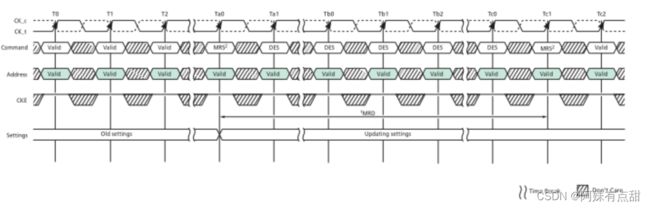

MRS命令循环时间tMRD是完成对模式寄存器的WRITE操作所必需的,它是tMRD时序图中显示的两个MRS命令之间所需的最小时间。

一些模式寄存器设置会影响地址/命令/控件输入功能。在这些情况下,可以在当前MRS命令更新的函数完成时允许下一个MRS命令。这些MRS命令不会遵循tMRD的时序要求;但是有些输入用例有独特的MR设置过程,因此请参考个别功能描述:

- Gear-down mode

- Per-DRAM addressability

- CMD address latency

- CA parity latency mode

- VREFDQ training value

- VREFDQ training mode

- VREFDQ training range

下图为tMRD的时序图:

MRS命令到非MRS命令的延迟tMOD是DRAM更新特性所必需的,但上面所指出的7个个别功能除外,其中各个功能描述可能指定不同的需求。tMOD为从MRS命令到非MRS命令(DES除外)所需的最短时间。

下图为tMOD的时序图:

模式寄存器内容可以在正常运行时使用相同的命令和时序要求更改,只要设备处于空闲状态;即所有bank都处于预充状态,tRP(预充电有效周期,在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行)满足,所有突发数据完成,写入模式寄存器之前CKE为高。如果在MRS命令之前和/或之后模式寄存器中启用了RTT(NOM)特性,ODT信号必须连续地拉低,以确保在MRS命令之前RTT处于关闭状态。

在tMOD过期后,ODT信号可能被拉高。如果在MRS命令之前和之后的模式寄存器中禁用了RTT(NOM)功能,那么在MRS命令之前、期间和之后,ODT信号可以被拉低或者拉高。模式寄存器根据功能和模式划分为不同的字段。

在某些模式寄存器设置的情况下,函数更新需要比tMOD更长的时间。这种类型的MRS与下一个有效命令的间隔不会遵循tMOD时序要求,DES除外。这些MRS命令输入用例的MR设置过程不同,请参考各自的功能说明。

模式寄存器0(MR0)

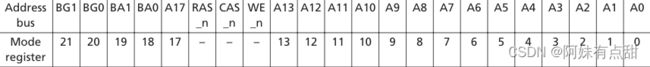

模式寄存器0 (MR0)控制各种设备运行模式,如下表所示。并非列出的所有设置都可以在片上使用;MR0是通过在控制BGx、BAx和Ax地址引脚的状态时发出MRS命令来写的。MRS命令期间的地址引脚映射见下表MR0寄存器定义。

注意:在MODE REGISTER SET命令期间,RAS_n、CAS_n和WE_n必须为LOW。

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:000=MR0 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 13,11:9 | WR(写恢复)/RTP(读-预充) |

| 0000 = 10 / 5 c l o c k s 1 0000 = 10 / 5 clocks^1 0000=10/5clocks1; 0001 = 12 / 6 c l o c k s 0001 = 12 / 6 clocks 0001=12/6clocks; 0010 = 14 / 7 c l o c k s 1 0010 = 14 / 7 clocks^1 0010=14/7clocks1 | |

| 0011 = 16 / 8 / c l o c k s 0011 = 16 / 8 / clocks 0011=16/8/clocks; 0100 = 18 / 9 c l o c k s 1 0100 = 18 / 9 clocks^1 0100=18/9clocks1; 0101 = 20 / 10 c l o c k s 0101 = 20 /10 clocks 0101=20/10clocks | |

| 0110 = 24 / 12 c l o c k s 0110 = 24 / 12 clocks 0110=24/12clocks; 0111 = 22 / 11 c l o c k s 1 0111 = 22 / 11 clocks^1 0111=22/11clocks1; 1000 = 26 / 13 c l o c k s 1 1000 = 26 / 13 clocks^1 1000=26/13clocks1 | |

| 1001 = 28 / 14 c l o c k s 2 1001 = 28 / 14 clocks^2 1001=28/14clocks2; 1010 到 1111 1010 到1111 1010到1111 = 保留 | |

| 8 | DLL复位:0=No,1=Yes |

| 7 | 测试模式 -仅供制造商使用 0=正常操作模式,必须编码为0 |

| 12,6:4,2 | CAS延迟(CL)——从内部READ命令到第一次数据输出的时钟周期延迟 |

| 00000 = 9 c l o c k s 1 00000 = 9 clocks^1 00000=9clocks1; 00001 = 10 c l o c k s 00001 = 10 clocks 00001=10clocks; 00010 = 11 c l o c k s 1 00010 = 11 clocks^1 00010=11clocks1 | |

| 00011 = 12 c l o c k s 00011 = 12 clocks 00011=12clocks; 00100 = 13 c l o c k s 1 00100 = 13 clocks^1 00100=13clocks1; 00101 = 14 c l o c k s 00101 = 14 clocks 00101=14clocks | |

| 00110 = 15 c l o c k s 1 00110 = 15 clocks^1 00110=15clocks1; 00111 = 16 c l o c k s 00111 = 16 clocks 00111=16clocks; 01000 = 18 c l o c k s 01000 = 18 clocks 01000=18clocks | |

| 01001 = 20 c l o c k s 01001 = 20 clocks 01001=20clocks; 01010 = 22 c l o c k s 01010 = 22 clocks 01010=22clocks; 01011 = 24 c l o c k s 01011 = 24 clocks 01011=24clocks | |

| 01100 = 23 c l o c k s 1 01100 = 23 clocks^1 01100=23clocks1; 01101 = 17 c l o c k s 1 01101 = 17 clocks^1 01101=17clocks1; 01110 = 19 c l o c k s 1 01110 = 19 clocks^1 01110=19clocks1 | |

| 10011 = 28 c l o c k s 10011 = 28 clocks 10011=28clocks; 10100 = 29 c l o c k s 1 10100 = 29 clocks^1 10100=29clocks1; 10101 = 30 c l o c k s 10101 = 30 clocks 10101=30clocks | |

| 10110 = 31 c l o c k s 1 10110 = 31 clocks^1 10110=31clocks1; 10111 = 32 c l o c k s 10111 = 32 clocks 10111=32clocks | |

| 3 | 突发类型(BT)——在读或写突发访问中进行数据突发排序 0=顺序;1=交织 |

| 1:0 | 突发长度(BL) -与每次读或写访问相关的数据突发大小 |

| 00 = BL8 (固定的) ;01 = BC4或BL8(即时) | |

| 10 = BC4 (固定的);11=保留 |

注意:在上面的表格中但凡是时钟后面标注了(1)的在gear-down mode为1/4rate时是不被允许的;后面标注了(2)的表示如果WR要求超过28个时钟或RTP超过14个时钟,则WR应设置为28个时钟,RTP应设置为14个时钟。

关于数据突发的类型,长度,排序以及起始列地址的问题如下表所示,突发长度选项包括固定BC4、固定BL8和动态(OTF),在读和写命令期间允许通过A12/BC_n同时选择BC4或BL8。

注意:

1、0…7比特数是CA(Column Address)[2:0]的值,它使该比特在突发中成为第一个读取。

2、当在MR0中将爆发长度设置为BC4(固定)时,内部WRITE操作比BL8模式早两个时钟周期开始,这意味着tWR和tWTR的起点将提前两个时钟周期。当在MR0中将突发长度设置为OTF时,内部WRITE操作与BL8同时开始(即使在使用A12/BC4_n的列时间中选择BC4),这意味着如果使用OTF MR0设置,tWR和tWTR的起始点将不会像BC4(固定)情况中所描述的那样提前两个时钟周期。

3、T=数据和选通信号的输出为High-Z状态;V=有效的逻辑电平(0或者1),但各自的缓冲区输入忽略引脚上的电平;X=任意值。

CAS延迟

CAS延迟(CL)设置在MR0寄存器定义表中定义。CAS延迟是以时钟周期为单位的内部READ命令和输出数据的第一位可用性之间的延迟。设备不支持半钟延时。整个的读延迟(RL)=额外的时延(AL)+CAS时延(CL)。

测试模式TM

正常工作模式由MR0[7]选择,所有其他位设置为MR0寄存器定义表中显示的所需值。将MR0[7]编程为1将设备置于DRAM制造商定义的测试模式中,仅供制造商使用,而不是终端用户使用。如果MR0[7] = 1,则不指定任何操作或功能。

写恢复(WR)/读预充

可编程写恢复(WR)值与tRP一起用于自动预充电功能,以确定tDAL。时钟周期内自动预充电的WR的最小值是通过将tWR(以ns为单位)除以tCK(以ns为单位),并使用将基于时间的规格转换为基于时钟周期的舍入算法舍入到下一个整数时钟周期来计算的。WR值必须编程为等于或大于tWR (最小值)。当模式寄存器中DM和写CRC都使能时,设备在将写数据发送到存储空间 之前计算CRC,并且tWR值也将改变。如果出现CRC校验错误,则阻断WRITE操作并丢弃数据。

时钟周期内自动预充的内部RTP (READ-to-PRECHARGE)命令延迟(最小值)的计算方法是将tRTP (ns)除以tCK (ns),并使用将基于时间的规格转换为基于时钟周期的舍入算法舍入到下一个整数时钟周期来计算的。模式寄存器中的RTP值必须编程为等于或大于RTP (最小值)。编程的RTP值与tRP一起用于确定到同一Bank的激活时间。

DLL(延时锁相环)复位

DLL重置位是自清除的,这意味着它在DLL reset功能发出后返回到值0。启用DLL(在MR1寄存器中启用)后,后续的DLL RESET被使能。在使用DLL RESET功能时,必须先满足tDLLK,才能使用需要DLL的功能。例如,READ命令或同步ODT操作。

模式寄存器1(MR1)

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:001=MR1 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 12 | 数据输出禁用(Qoff)–输出缓冲区禁用 0=使能(正常模式) 1=禁用(ODI和RTT) |

| 11 | 终端数据选通(TDQS)–附加终端引脚(仅x8配置)0=TDQS禁用 1=TDQS使能 |

| 10:8 | 标称ODT(RTT(NOM)–数据总线终端设置 |

| 000 = RTT(NOM) 禁用;001 = RZQ/4 (60Ω);010 = RZQ/2 (120Ω) | |

| 011 = RZQ/6 (40Ω);100 = RZQ/1 (240Ω);101 = RZQ/5 (48Ω) | |

| 110 = RZQ/3 (80Ω);111 = RZQ/7 (34Ω) | |

| 7 | 写入均衡(WL)–写入均衡模式 0=禁用(正常模式) 1=使能(进入WL模式) |

| 13,6,5 | Rx CTLE控制 |

| 000 = 供应商默认值;001 = 供应商定义;010 = 供应商定义 | |

| 011 = 供应商默认值;100 = 供应商定义;101 = 供应商定义 | |

| 110 = 供应商默认值;111 = 供应商定义 | |

| 4,3 | 附加延迟(AL)–命令附加延迟设置 |

| 00 = 0 ( A L 禁 用 ) ; 01 = C L − 1 1 00=0(AL禁用);01=CL-1^1 00=0(AL禁用);01=CL−11 | |

| 10 = C L − 2 10=CL-2 10=CL−2;11=保留 | |

| 2,1 | 输出驱动器阻抗(ODI)–输出驱动器阻抗设置小 |

| 00 = RZQ/7 (34Ω);01 = RZQ/5 (48 Ω) | |

| 10=保留(虽然没有JEDEC定义和测试,但此设置将提供RZQ/6或40欧姆);11=保留 | |

| 0 | DLL启用–DLL启用功能 0=DLL禁用 1=DLL使能(正常模式) |

注意:在上面的表格中但凡是后面标注了(1)的在gear-down mode为1/4rate时是不被允许的。

DLL(延时锁相环)使能/禁用

必须为正常操作启用DLL,并且在加电初始化期间以及在禁用DLL后恢复正常操作时需要该DLL。在正常操作期间(使用MR1[0]启用DLL),当进入SELF REFRESH操作时,DLL自动禁用,并在退出SELF REFESH操作时自动重新启用。无论何时启用DLL并随后重置,在发出READ或SYNCHRONOUS ODT命令以允许内部时钟与外部时钟同步之前,都必须出现tDLLK时钟周期。若同步的结果未能发生,可能会违反tDQSCK、tAON或tAOF参数。

在tDLLK期间,CKE必须连续被拉高。设备不需要DLL进行任何WRITE操作,除非启用了RTT(WR),并且需要DLL进行正确的ODT操作。

在DLL关闭模式下不支持直接ODT特性。ODT电阻必须通过连续将ODT引脚拉低和/或通过在DLL关闭模式下通过MRS命令编程RTT(NOM)位MR1[9,6,2] = 000来禁用。动态ODT特性在DLL关闭模式下不支持;要从外部禁用动态ODT,使用MRS命令设置RTT(WR), MR2[10:9] = 00。RTT(WR)是指可以动态改变ODT而不需要重新设置MR寄存器。

ODT RTT(标称)值

该设备能够提供三种不同的终止值:RTT(Park), RTT(NOM)和RTT(WR)。标称终止值RTT(NOM)在MR1中编程。在MR2中可以编程一个单独的值RTT(WR),以便在WRITE操作期间启用ODT时启用唯一的RTT值。即使禁用了RTT(NOM),也可以在WRITE命令中应用RTT(WR)值。第三个RTT值RTT(Park)在MR5中编程。RTT(Park)在ODT信号为LOW时提供终止值。

AL(附加延迟)

支持ADDITIVE LATENCY (AL)操作,以使命令和数据总线有效地实现设备中的可持续带宽。在此操作中,设备允许在ACTIVATE命令之后立即发出READ或WRITE命令(带或不带自动预充电)。该命令在设备内部发出之前一直保持AL的时间。读延迟(RL)由AL和CAS延迟(CL)寄存器设置的总和控制。写延迟(WL)由AL和CAS写延迟(CWL)寄存器设置的总和控制。

写入均衡

为了更好的信号完整性,该设备对命令、地址、控制信号和时钟使用fly-by。fly-by得益于减少存根数量和存根长度,但它会导致内存上每个DRAM上的时钟和选通信号之间的传输时间偏差。这使得控制器很难维持tDQSS、tDSS和tDSH。因此,该设备支持写入均衡功能,允许控制器对偏差进行弥补。

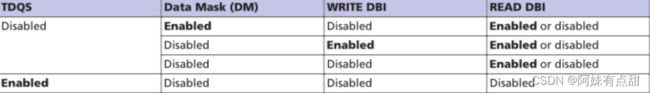

终端数据选通(TDQS)

终端数据选通(TDQS)是x8设备的一个特性,提供了额外的终端电阻输出,在某些系统配置中可能有用。由于此功能仅在x8配置中可用,因此必须禁用x4和x16配置。虽然在x4或x16配置中不支持TDQS,但当通过模式寄存器启用时,应用于TDQS引脚的相同终止电阻功能将应用于DQS引脚。TDQS、DBI和DM (DATA MASK)功能共用一个引脚。当通过模式寄存器使能TDQS功能时,不支持DM和DBI功能。当TDQS功能关闭时,DM和DBI功能可以分开开启。

模式寄存器2(MR2)

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:010=MR2 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 13 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 12 | 写入数据总线CRC 0=禁用 1=使能 |

| 11:9 | 动态ODT(RTT(WR))–写入期间的数据总线终止设置 |

| 000 = RTT(WR)禁用(WRITE不影响RTT值);001 = RZQ/2 (120Ω);010 = RZQ/1 (240Ω) | |

| 011 = 高阻态;100 = RZQ/3 (80Ω);101 = 保留 | |

| 110 = 保留;111 = 保留 | |

| 7,6 | 低功耗自动刷新(LPASR)–模式摘要 |

| 00=手动模式-正常工作温度范围(TC:-40°C–85°C;01=手动模式-降低工作温度范围(TC:-40°C–45°C) | |

| 10=手动模式-扩展工作温度范围(TC:-40°C–105°C);11=ASR模式即在所有模式之间自动切换 | |

| 5:3 | CAS WRITE latency(CWL)–从内部WRITE命令到1tCK WRITE前导码中第一个数据的时钟周期延迟 |

| 000 = 9 ( D D R 4 − 1600 ) 1 000 =9(DDR4-1600)^1 000=9(DDR4−1600)1 ; 001 = 10 ( D D R 4 − 1866 ) 001 = 10 (DDR4-1866) 001=10(DDR4−1866); 010 = 11 ( D D R 4 − 2133 / 1600 ) 1 010 = 11 (DDR4-2133/1600)^1 010=11(DDR4−2133/1600)1 | |

| 011 = 12 ( D D R 4 − 2400 / 1866 ) 011 = 12 (DDR4-2400/1866) 011=12(DDR4−2400/1866); 100 = 14 ( D D R 4 − 2666 / 2133 ) 100 = 14 (DDR4-2666/2133) 100=14(DDR4−2666/2133); 101 = 16 ( D D R 4 − 2933 , 3200 / 2400 ) 101 = 16 (DDR4-2933,3200/2400) 101=16(DDR4−2933,3200/2400) | |

| 110 = 18 ( D D R 4 − 2666 ) 110 = 18 (DDR4-2666) 110=18(DDR4−2666); 111 = 20 ( D D R 4 − 2933 , 3200 ) 111 = 20 (DDR4-2933, 3200) 111=20(DDR4−2933,3200) | |

| CAS WRITE latency(CWL)–从内部WRITE命令到2tCK WRITE前导码中的第一个数据的时钟周期延迟 | |

| 000 = N / A 000 = N/A 000=N/A; 001 = N / A 001 = N/A 001=N/A; 010 = N / A 010 = N/A 010=N/A | |

| 011 = N / A 011 = N/A 011=N/A; 100 = 14 ( D D R 4 − 2400 ) 100 = 14 (DDR4-2400) 100=14(DDR4−2400); 101 = 16 ( D D R 4 − 2666 / 2400 ) 101 = 16 (DDR4-2666/2400) 101=16(DDR4−2666/2400) | |

| 110 = 18 ( D D R 4 − 2933 , 3200 / 2666 ) 110 = 18 (DDR4-2933, 3200/2666) 110=18(DDR4−2933,3200/2666); 111 = 20 ( D D R 4 − 2933 , 3200 ) 111 = 20 (DDR4-2933, 3200) 111=20(DDR4−2933,3200) | |

| 8,2 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 1:0 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

CAS写延迟

CAS写延迟(CWL)由MR2[5:3]定义,如MR2寄存器定义表所示。CWL是以时钟周期为单位,在内部WRITE命令和输入数据的第一位可用性之间的延迟。设备不支持任何半时钟周期延迟。总体写时延定义为AL (additive latency) +PL (parity latency) + CAS写时延:WL = AL +PL + CWL。

低功耗自动自刷新

设备支持低功耗LPASR (auto self refresh)功能。在不同的温度范围内需要SELF REFRESH操作的应用程序可以使用此功能优化给定温度范围内的IDD6电流,如MR2寄存器定义表中指定的那样。

动态ODT

在某些应用中,为了进一步增强数据总线上的信号完整性,需要在不发出MRS命令的情况下改变设备的终端电阻。这可以通过配置MR2中的动态ODT (RTT(WR))设置来实现[11:9]。在写均衡模式下,只有RTT(NOM)可用。

写循环冗余校验数据(CRC)总线

设备已添加写时CRC (write cyclic redundancy check)数据总线特性。当通过模式寄存器启用时,数据传输大小从正常的8位(BL8)帧变为更大的10位UI帧,额外的两个UI用于CRC信息。

模式寄存器3(MR3)

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:011=MR3 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 13 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 12:11 | 多用途寄存器(MPR) -读取格式 |

| 00 =串行;01 =并行 | |

| 10 =交错;11 =预留 | |

| 10:9 | 当启用CRC/DM时,写CMD延迟 |

| 00 = 4CK (DDR4-1600);01 = 5CK (DDR4-1866/2133/2400/2666) | |

| 10 = 6CK (DDR4-2933/3200);11=保留 | |

| 8:6 | 精细化刷新频率间隔设置 |

| 000 =正常模式(固定1x);001 =固定2x | |

| 010 = 固定4x;011 =保留 | |

| 100 =保留;101 =即时1x/2x | |

| 110=即时1x/4x;111=保留 | |

| 5 | 温度传感器状态 0=禁用;1=使能 |

| 4 | Per-DRAM可寻址能力 0=正常操作模式 (禁用);1=使能 |

| 3 | Gear-down减速模式-内部时钟与外部数据速率的比率 |

| 0 = [1:1];(1/2数据速率);1 = [2:1];(1/4数据速率) | |

| 2 | 多用途寄存器(MPR)访问,0=正常操作模式;1= MPR的数据流 |

| 1:0 | MPR页面选择 |

| 00=Page0;01=Page1 | |

| 10=Page2;11=Page3(仅限DRAM制造商使用) |

多用途寄存器

多用途寄存器(WPR)用于多种功能:

- MRn寄存器内容的读出;

- 用于数据总线校准的WRITE和READ系统模式;

- 启用命令地址奇偶校验特性时错误帧的读出;

为了启用MPR,向MR3[2] = 1发出MRS命令。MR3[12:11]定义从MPR读取数据的格式。在发出MRS命令之前,所有Bank必须处于空闲状态(所有Bank都已预充电且tRP已满足)。启用MPR后,任何后续的RD或RDA命令将被重定向到特定的模式寄存器。

模式寄存器的位置是由READ命令中的地址位指定的,MR被分成上下两部分以对齐8位的突发长度限制,在MPR模式下不允许下电模式、自刷新或别的非 RD/RDA或者是非WR/WRA指令。MPR模式支持复位功能,需要重新初始化设备。

当CRC/DM使能时,WRITE命令时延

当同时启用写CRC和DM时,必须设置WRITE命令延时(WCL)。当启用写CRC和DM时,这提供了完成WRITE突发所需的额外时间。这意味着当数据速率小于或等于1600 MT/s时,使用4nCK,不允许使用5nCK或6nCK;当数据速率大于1600mt /s且小于或等于2666mt /s时,则使用5nCK,不允许使用4nCK或6nCK;当数据速率大于2666 MT/s且小于等于3200 MT/s时,则使用6nCK;不允许使用4nCK或5nCK

精细化刷新频率间隔设置

此模式已添加到DDR4,以帮助对抗高密度刷新锁定导致的性能损失。缩短tRFC和减少周期时间允许更多的访问芯片,并允许增加调度灵活性。

温度传感器状态

该模式指示DRAM在MPR Page 2, MPR0[4,3]处更新温度传感器状态。温度传感器设置应在32毫秒内更新;当温度传感器状态位发生MPR读取时,温度传感器状态应不大于32ms,这个MPR 每个Page上的内容其实已经定义好了,感兴趣的可以去DDR4_JESD79_标准规范里查看。

Per-DRAM可寻址能力

这种模式允许在每个设备的基础上屏蔽命令,提供一个级别的任何设备(共享相同命令和地址信号的设备)单独编程。例如,该特性可用于在给定的等级内对DRAM设备上编写不同的ODT或VREF值。

Gear-down减速模式

设备默认为1/2速率(1N)时钟模式,并在1/4速率(2N)模式下使用低频MRS命令和同步脉冲来对齐适当的时钟边缘,以操作控制线CS_n, CKE和ODT。对于1/2速率模式的操作,不需要MRS命令或同步脉冲。

模式寄存器4(MR4)

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:100=MR4 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 13 | 硬件封装后修复(hppr模式) ,0=禁用;1=使能 |

| 12 | 写序言设置 |

| 0=1 tck触发;1=2tck触发(当在 2t CK WRITE 前同步码模式下运行时,CWL 必须编程为至少比适用的 t CK 范围内支持的最低 CWL 设置大 1 个时钟的值) | |

| 11 | 读序言设置 0=1 tck触发;1=2tck触发 |

| 10 | 读序言训练 0=禁用 1=使能 |

| 9 | 自刷新中止模式;0=禁用 1=使能 |

| 8:6 | CMD (CAL)地址延迟 |

| 000 = 0 c l o c k s 000 =0 clocks 000=0clocks (禁用); 001 = 3 c l o c k s 1 001 =3 clocks^1 001=3clocks1 | |

| 010 = 4 c l o c k s 010 = 4 clocks 010=4clocks; 011 = 5 c l o c k s 1 011 =5 clocks^1 011=5clocks1 | |

| 100 = 6 c l o c k s 100 = 6 clocks 100=6clocks; 101 = 8 c l o c k s 101 =8 clocks 101=8clocks | |

| 110 = 保 留 110=保留 110=保留; 111 = 保 留 111=保留 111=保留 | |

| 5 | 软件封装后修复 0=禁用;1=使能 |

| 4 | 内部VREF监控器 0=禁用;1=使能 |

| 3 | 温控刷新模式 0=禁用;1=使能 |

| 2 | 温控刷新范围 0=常温模式;1= 扩展温度模式 |

| 1 | 最大节电模式 0=正常操作模式;1=使能 |

| 0 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

硬/软件封装后修复

这块推荐看下下面的参考资料,讲的很详细。

写/读序言

这块推荐看下下面的参考资料,讲的很详细。

读序言训练

可编程READ前导训练可设置为1tCK或2tCK。存储控制器能够用这种模式来训练或者读取它的数据选通接收器的电平值。

温控刷新

当开启温控刷新模式时,设备可能会跳过外部refresh命令,通过适当的齿轮传动比将内部刷新周期调整为大于正常温度范围的tREFI。例如,DRAM温度传感器检测到小于45°C。常温模式覆盖-40°C ~ 85°C,扩展温度范围覆盖-40°C ~ 105°C。

命令地址延迟

CAL是一种节能特性,可以通过MRS设置启用或禁用。CAL被定义为一个CS_n信号拉低与其对应的CMD/ADDR之间的时钟周期延迟(tCAL)。CAL的值(以时钟为单位)必须根据将基于时间的规范转换为基于时钟的要求一节中的tCAL(ns)/tCK(ns)舍入算法编程到模式寄存器中。

内部VREF监视器

此模式使能内部生成的用来监视DQ0\DQ1\DQ2\DQ3的输出。在训练和测试 V R E F D Q VREF_{DQ} VREFDQ中可能会用到。当处于该模式时, R T T R_{TT} RTT需要设置为高阻状态。如果DQ负载为0pf, V R E F t i m e VREF_{time} VREFtime必须增加到10ns,再加上每1pf负载增加15ns。此测量是为了验证目的,不是外部电压供应引脚。

最大节电模式

该模式为最低功耗模式,无需保留数据。当设备处于最大节电模式时,不需要保证数据保留或响应任何外部命令(除了最大节电模式 EXIT命令和RESET_n信号低有效期间)。

模式寄存器5(MR5)

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:101=MR5 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 13 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 12 | 数据总线反转(DBI) -DBI读使能 0=禁用;1=使能 |

| 11 | 数据总线反转(DBI) -DBI写使能 0=禁用;1=使能 |

| 10 | 数据掩码 0=禁用 1=使能 |

| 9 | CA校验持续模式;0=禁用 1=使能 |

| 8:6 | ODT停靠值( R T T ( P a r k ) R_{TT(Park)} RTT(Park)) |

| 000 = R T T ( P a r k ) R_{TT(Park)} RTT(Park) (禁用);001 =RZQ/4(60欧姆) | |

| 010 =RZQ/2(120欧姆);011 =RZQ/6(40欧姆) | |

| 100 =RZQ/1(240欧姆);101 =RZQ/5(48欧姆) | |

| 110 =RZQ/3(80欧姆);111 =RZQ/7(34欧姆) | |

| 5 | 用于断电的ODT输入缓冲 0=缓冲使能;1=缓冲禁用 |

| 4 | CA校验错误状态 0=清除;1=错误 |

| 3 | CRC错误状态 0=清除;1=错误 |

| 2:0 | CA校验延迟模式 |

| 000=禁用;001= 4个时钟(DDR-1600/1866/2133) | |

| 010=5个时钟 ( D D R − 2400 / 2600 ) 1 (DDR-2400/2600)^1 (DDR−2400/2600)1;011=6个时钟(DDR-2933/3200) | |

| 100=保留;101=保留;110=保留;111=保留 | |

| 注意:右上标带有1的当1/4 rate gear-down模式使能时是不被允许的 |

数据总线反转(DBI)

DBI功能仅在x8/x16的配置设备上支持,不支持x4配置。DBI功能和DM以及TDQS功能共用引脚。DBI功能在读写操作上均支持,当DM功能使能时不能使能写DBI,具体参考TDQS的功能表(MR1_A11),了解DBI\DM\TDQS三个功能的配置关系。在MPR读操作期间不允许DBI;在MPR读取期间,DRAM忽略MR5A12中的读DBI使能设置。3DS设备不支持DBI,应该在MR5中禁用。

数据掩码(DM)

DM功能也可理解为局部的写操作,同样该功能仅在x8/x16的配置设备上支持,不支持x4配置。DM功能和DBI以及TDQS功能共用引脚。DM功能仅应用于写操作,不能和DBI写功能同时使能,具体参考TDQS的功能表(MR1_A11),了解DBI\DM\TDQS三个功能的配置关系。

CA校验持续模式

正常的CA校验模式是将CA检验持续模式给禁用,在校验错误状态位设置为1时不再执行CA校验。但是,如果启用了CA校验持续模式,当奇偶校验状态位设置为1时,将继续进行CA奇偶校验。

用于断电的ODT输入缓冲区

该特性决定在断电期间ODT输入缓冲区是打开还是关闭。如果输入缓冲区配置为on(在断电期间启用),ODT输入信号必须处于有效的逻辑电平。如果输入缓冲区被配置为关闭(断电时禁用),ODT输入信号可能是浮动的,设备不提供RTT(NOM)终止。然而,该设备可以根据MR设置提供RTT(Park)终止。这主要是为了节省额外的电力。

CA校验状态位

一旦检测到一个校验位出错,就会将该状态位拉高,直到设备控制器用MRS指令清除它。

CRC状态位

一旦检测到一个CRC位出错,就会将该状态位拉高,直到设备控制器用MRS指令清除它。

CA校验延迟模式

当一个依赖于tCK的延迟值被设定时,CA校验会被使能。这个说明了设备内部的校验计算延迟。CA校验的正常状态是禁用状态,如果CA校验使能,必须确保设备在使能之前不存在任何的校验错误。CA校验信号包括ACT_n、RAS_n/A16 ,CAS_n/A15, WE_n/A14,和包含bank地址和bank group的地址总线,不包括控制信号CKE、ODT、CS_n。

模式寄存器6(MR6)

| 模式寄存器位 | 描述 |

|---|---|

| 21 | RFU(Reserved for Future Use) ,0=必须编码;1=保留 |

| 20:18 | 寄存器选择:110=MR6 |

| 17 | N/A(Not Applicable), 0=必须编码;1=保留 |

| 12:10 | 数据速率, |

| 000=数据速率<=1333Mb/s(1333Mb/s) | |

| 001=1333Mb/s<数据速率<=1866Mb/s(1600,1866Mb/s) | |

| 010=1866Mb/s<数据速率<=2400Mb/s(2133,2400Mb/s) | |

| 011=2400Mb/s<数据速率<=2666Mb/s(2600Mb/s) | |

| 100=2600Mb/s<数据速率<=3200Mb/s(2933,3200Mb/s) | |

| 101=保留;110=保留;111=保留 | |

| 13,9,8 | RFU(Reserved for Future Use) 默认=000,必须编码为000 |

| 7 | VREF校准使能 0=禁用;1=使能 |

| 6 | VREF校准范围 0=范围1;1=范围2 |

| 5:0 | VREF校准值 参见VREFDQ校准部分中的VREFDQ范围和电平表 |

参考链接:

ASIC.ddr.ddr3.常用操作

DRAM时序

DDR3命令状态(二)

DDR 学习时间 (Part B - 1):DRAM 刷新

DDR中寄存器的问题

DDR模式寄存器

DDR的工作时序及原理

DDR扫盲

DDR Mermory工作原理

从原理上解释什么是DDR的ZQ校准

DDR 学习时间 (Part B - 3):Write Leveling

内存对抗损坏的坚实堡垒:封装后修复(PPR)是什么?

DDR中write preamble 和 read preamble

DDR4 SDRAM数据手册

DDR4_JESD79_标准规范