计算机组成原理知识总结——存储器篇

存储器

- 1.概述

-

- 1.1 存储器的分类

- 1.2 存储器的层次结构

- 2.主存储器

-

- 2.1 概述

- 2.2 半导体存储芯片简介

- 2.3 随机存取存储器(RAM)

- 2.4 只读存储器ROM

- 2.5 存储器和CPU的连接

-

- 2.5.1 存储容量的扩展

- 2.5.2 存储器与CPU的连接

- 2.6 存储器的校验

- 2.7 提高访存速度的措施

- 3.高速缓冲存储器(Cache)

-

- 3.1 概述

- 3.2 Cache的基本结构

-

- 3.2.1 Cache存储体

- 3.2.2 地址映射变换机构

- 3.2.3 替换机构

- 3.2.4 Cache读写操作

- 3.3 Cache的改进

- 4.辅助存储器

1.概述

1.1 存储器的分类

按存储介质分类:半导体存储器(易失)、磁表面存储器、磁芯存储器、光盘存储器。(这三种都是非易失)

按存取方式分类:随机存储器(RAM,random access memory),只读存储器(read only memory),顺序存取存储器(如:磁带),直接存取存储器(如磁盘)。

注意RAM又分为静态RAM(用触发器存储信号)和动态RAM(用电容存储信号),断电后信息都会消失。

ROM断电后信息不消失。

1.2 存储器的层次结构

存储器的性能指标:速度、价格、容量。通常三者不能同时达到最优。

存储器的层次结构:主存-辅存结构、缓存-主存结构

主存-辅存结构用来提升容量,缓存-主存结构用来提升速度。

2.主存储器

2.1 概述

在有些主存中,MAR和MDR在主存内部,所以数据传输过程是地址总线->MAR->M->MDR->数据总线。

存储单元地址分配:地址总线的位数决定地址的范围,而采用字寻址方式还是字节寻址方式,决定了寻址范围。有的机器,1个字=2个字节,有的机器,1个字=4个字节.

主存的技术指标:存储容量、存储速度(前两者是主要的)、存储器带宽。

存储容量= 存储单元的个数*存储字长

存储速度由存取时间和存取周期决定,通常存取时间<存取周期

存储器带宽:单位时间内存储器存取的信息量。

2.2 半导体存储芯片简介

- 其容量由地址线和数据线共同构成。

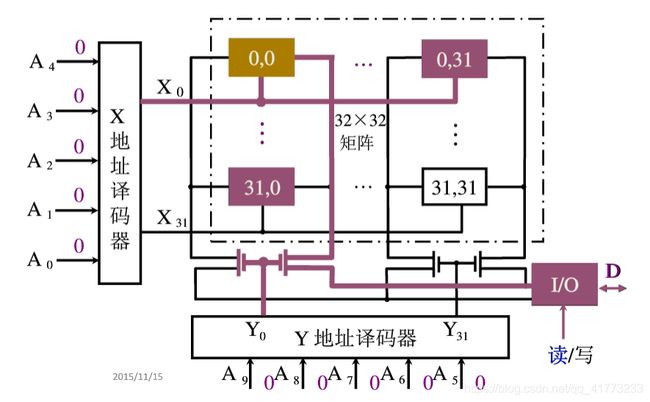

- 译码驱动方式分为线选法和重合法。

线选法:用一根字选择线,直接选中一个存储单元的各个位。

优点: 结构简单;

缺点: 不适于容量大的存储芯片,因为是直接通过地址线选择,如果有10根地址线,则容量为1K,需要引出210条字线

重合法:用两根字选择线,同时选中时,才能选中一个存储单元的一个位。

优点: 适用于容量大的芯片,比如10根地址线,容量为1K,但是只需要引出2*25条字线

缺点: 结构复杂

2.3 随机存取存储器(RAM)

静态RAM:以触发器为基本电路,速度快,断电后信息消失,属于易失性半导体存储器,价格高,集成度相对低

动态RAM:基于电容存储电荷,来存储信息。即使不断电,信息也会消失,因此需要刷新。价格低,集成度相对高。

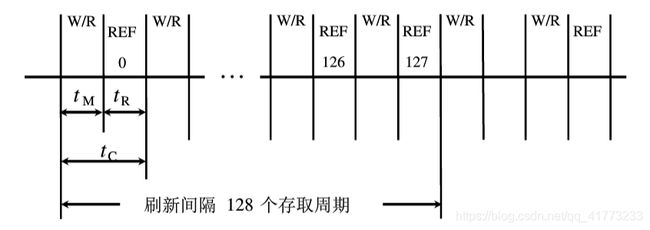

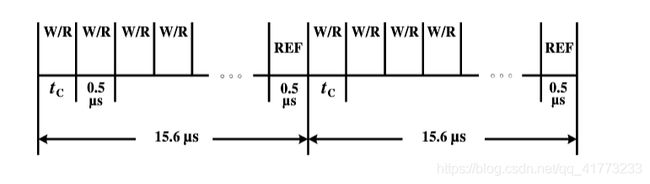

动态RAM刷新的三种方式:集中刷新、分散刷新、异步刷新。

集中刷新: 如下图所示,它在最后的128个周期内刷新,此时存储器不能做任何的读写操作,因此“死区”占比:128/4000*100%=3.2%

分散刷新: 如下图所示,它将刷新时间分散到每个存取周期内完成,每个存取周期做这两件事情,第一件事是进行读/写操作或者维持信息,第二件事情是刷新操作,因此刷新操作是不会占用读/写时间的,因此无死区。但存取周期被拉长了,整个系统的速度降低了。

异步刷新: 如下图所示,结合以上两种方式,把128次刷新均匀地分布在2ms中,通过合理地安排刷新时间(比如安排在CPU不访存的时间),就能减少死区时间,同时系统速度不被拉低。

2.4 只读存储器ROM

- 掩膜ROM:只能读,用MOS管构成。

- PROM:可以改写一次,用双极型电路和熔丝构成。

- EPROM:可以改写多次,但是改写时间很长,比较费事。用浮动栅雪崩注入型MOS管构成。

- EEPROM:电可擦式可编程只读存储器,改写极为方便。用电气的方式构成。

2.5 存储器和CPU的连接

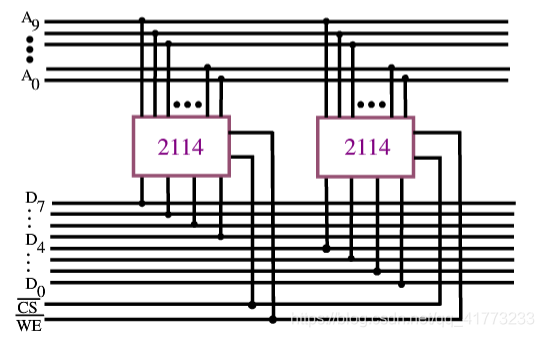

2.5.1 存储容量的扩展

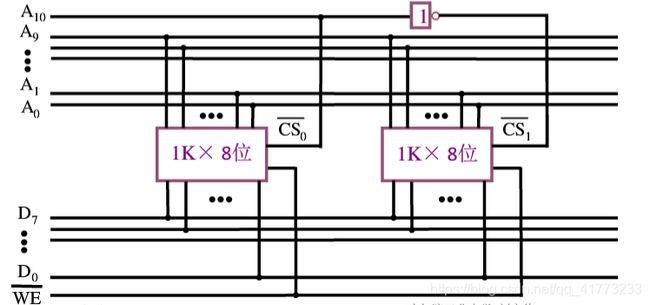

字扩展:通过多增加一根数据线,并加上非门,来实现同一地址下,存储字长的增加。

位扩展:通过连在不同的地址总线上,增加存储的容量,可以访问更多的空间。

字、位扩展:顾名思义,字扩展和位扩展同时用上,既增加寻址范围,又增加某一地址的存储字长。

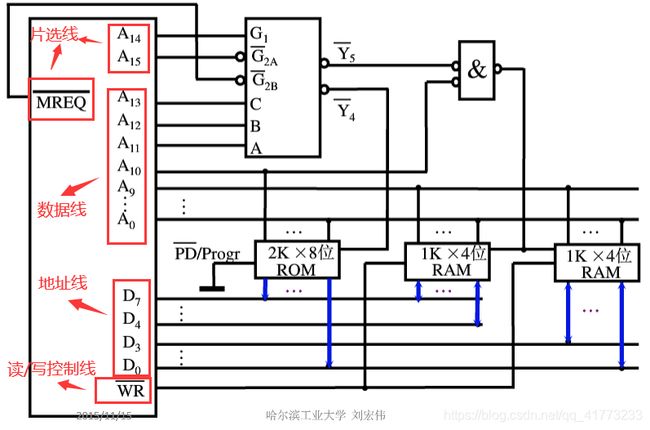

2.5.2 存储器与CPU的连接

地址线的连接:地址线的条数,应该与存储单元个数有关。数据线的连接:数据线的条数,应该与芯片的存储字长有关读写控制命令的连接:只有RAM才接这玩意,ROM不接片选线的连接:地址码-地址线=片选线,注意还要加上CPU的MREQ(上面还有一横但没办法打出来。 这是控制访存信号)合理选择芯片:即ROM与RAM的类型与数量

2.6 存储器的校验

数据在存储的过程中出现可能差错,为了发现错误并纠正错误,可以将原数据配成汉明编码。

汉明码的组成:真正的数据位+检测位。通常检测位会散布在数据位中,这样通过排列检测位,并直接读取检测位的值,就可以知道哪个数据位出现了错误。

检测位i在2i-1上。 检测位既可以按照配寄原则,也可以按照配偶原则

比如:

按照配偶原则接受到的汉明码是:0100111,试分析哪一位出错?

第1位是检测位,它负责让1,3,5,7的“1”的个数为偶数,分析后发现,确实都是偶数,那就为0;

第2位是检测位,它负责让2,3,6,7的“1”的个数为偶数,分析后发现,此时是奇数个,那说明这个检测位管理的组有问题,那么C2就为1;

第4位是检测位,它负责让4,5,6,7的“1”的个数为偶数,分析后发现,此时是奇数个,那说明这个检测位管理的组有问题,那么C4就为1;(配奇原则同理)

因此C4C2C1=110;因此是第6位出错,故原正确数据应该为:0100101

小技巧:对于检测位控制的组的位数很好记,只要记住第i组的检测位为2i-1,其余的可以用检测位的组合的方式给出。

比如,四个检测位

1号检测位,控制:1,3,5,7,9,11,13,15;

2号检测位,控制:2,3,6,7,10,11,14,15;

4号检测位,控制:4,5,6,12,7,14,13,15;

8号检测位,控制:8,9,10,12,11,13,14,15;

2.7 提高访存速度的措施

-

单体多字系统

-

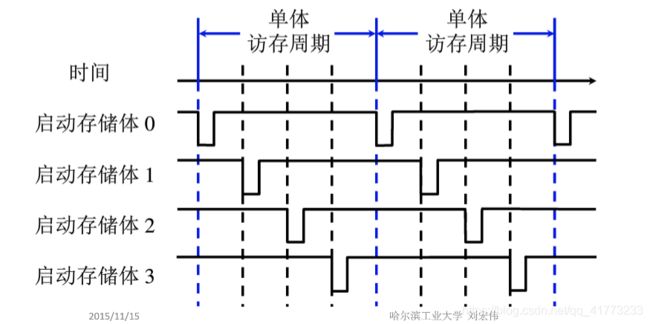

多体并行系统。多体并行系统又可以分为低位交叉编址和高位交叉编址。

高位交叉编址又称为顺序存储。如下图所示,优点:扩容方便;缺点:对速度的提升几乎不大。

低位交叉编址又称为交叉存储。如下图所示,优点:对存储器的带宽提升巨大,因为它可以在一个访存周期内交叉访问存储体;缺点:扩容不便。

-

用高性能存储芯片

同步DRAM、Rambus DRAM、带cache的DRAM等

3.高速缓冲存储器(Cache)

3.1 概述

Cache的出现是为了解决CPU的运行速度和存储器的速度之间的差异,让CPU直接在Cache访问数据能大幅提升计算机的运行速度。

Cache利用了程序访问的局部性,即访存的时候,所需要的数据或者指令通常在物理上都是连续存放的;而且访问过一次的内存,很大概率会再次访问。

在正式了解Cache之前需要考虑以下几个问题:

- Cache的容量肯定是远小于主存的容量,那么Cache的地址和主存的地址应该如何对应呢?

- 如何评价Cache的访问效率?

在解决第二个问题之前,先了解命中率这一概念。

命中率h h=(Nc)/(Nc + Nm),其中Nc是访问Cache的命中次数,Nm是访问主存的命中次数。

访问效率e e = (tc)/(h*tc+(1-h)*tm)。tc是访问Cache的时间,tm是访问主存所需的时间。

块长与命中率之间的关系这个关系较为复杂,在块长较小的时候

3.2 Cache的基本结构

3.2.1 Cache存储体

Cache存储体以块为单位与主存交换信息,且Cache访存的优先级最高。

3.2.2 地址映射变换机构

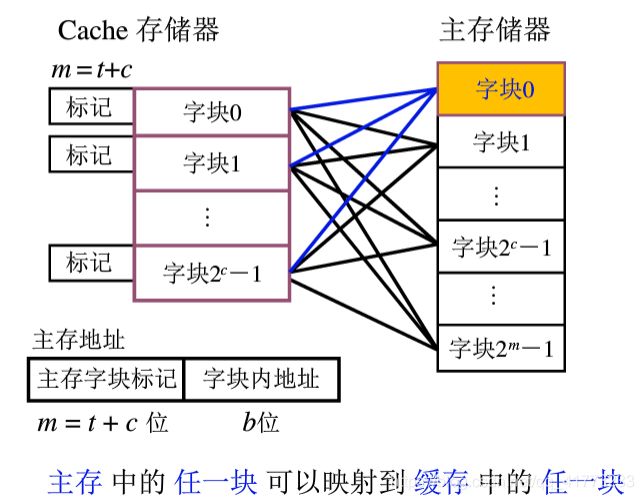

直接映射:主存每个区的固定位置的字块给Cache固定位置的字块。t位的标记是用来标记字块来自哪个区。

全相联映射:主存的任意字块可以放在任意Cache的字块中。这样能够充分利用Cache的空间,但同时标记的位数必须从t位增加到t+c位(也就是主存的字块个数为2t+c),逻辑电路就变得复杂很多。

组相联映射(现代计算机常用的方法)。综合直接映射和全相联映射的特点。还是把主存的字块分区,每个区的固定位置放在固定的组里,组里满了的话,还想装那个位置的字块就装不下了。此时标记的位数为t+r要小于t+c。当r=1时,又称为二路组相联。

3.2.3 替换机构

- 先进先出算法(First In First Out)

- 近期最少使用算法(Least Recently Used),这种方法最科学。

- 随机法

3.2.4 Cache读写操作

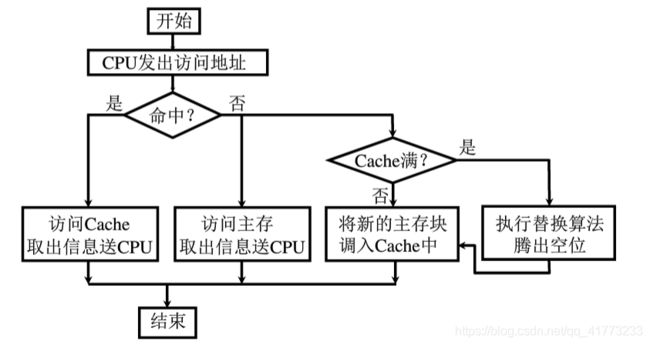

- 读操作简单,如果Cache里有数据,那么CPU直接访问Cache,如果Cache没有数据,那么CPU访问内存,同时把这个字块放到Cach里(如果Cache满了的话,可以用LRU算法替换)

- 写操作。有两种方法,一种是写直达法(又称存直达法),写操作的时候既写入Cache,又写入主存。另一种方法是写回法(又称拷回法),即先只写入Cache,一旦Cache那部分要被替换出去了,就写入主存,显然这种方法更加科学,但是要增加一个标志位,来识别是否Cache与主存一致。

3.3 Cache的改进

- 单一缓存和两级缓存

单一缓存:CPU和主存之间只有一个缓存。

两级缓存:CPU <-> 缓存1 <-> 缓存2 <->主存。 - 统一缓存和分立缓存

统一缓存:指令和数据放在一个cache里

分立缓存:指令和数据放在不同cache里,有单独的指令Cache和单独的数据Cache。

4.辅助存储器

辅存属于非易失性存储器;而主存因为大多是由半导体芯片构成,所以是易失性存储器。

常用的辅存有:硬磁盘、软磁盘、磁带、光盘等,具体原理就不一一叙述了。

最后,创作不易,希望大家能顺手点个赞。如果觉得有帮助,可以加个收藏,给作者更大的创作动力