小猫爪:i.MX RT1050学习笔记3-CCM

小猫爪:i.MX RT1050学习笔记3-CCM

- 1 前言

- 2 RT时钟的管理

- 3 CCM的结构

- 4 CCM的时钟树

- 5 时钟模块的具体功能

-

- 5.1 生成时钟

-

- 5.1.1 时钟源

- 5.1.2 7个PLLs

- 5.1.3 PFD

- 5.1.4 LPCG

- 5.2 支持DVFS

- 5.3 低功耗模式

- 6 相关寄存器

- 6 应用实例

1 前言

时钟是MCU的心脏,每一款MCU都有自己的心脏,其生成和控制着整个MCU不同模块的时钟。

2 RT时钟的管理

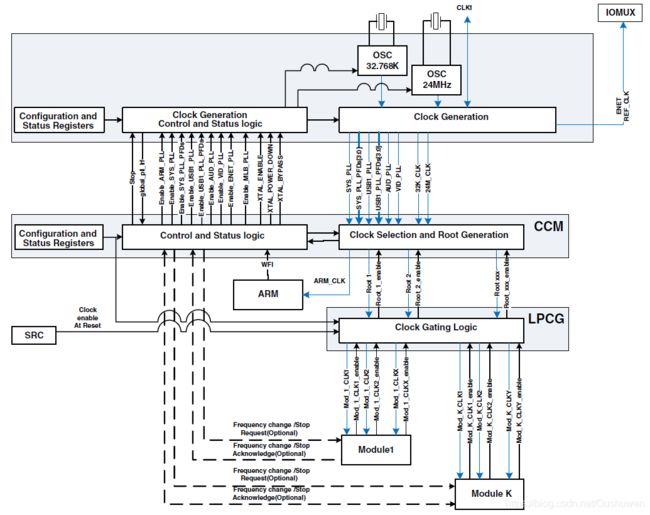

首先让我们来看一看RT1050的时钟管理,下图为RT1050的时钟管理图。

从图中我们看到时钟的产生总共经过了三个环节,分别是时钟源,CCM,LPCG三个部分。

①时钟源

时钟源的作用非常简单,就是选择时钟输入(外部晶振和内部RC)产生各种时钟源。

②CCM(Clock Control Module)

CCM控制着RT1050内部根时钟的生成,选择不同的时钟源(PLLs, PFDs, OSC24M)后再进行相关分频产生各种根时钟。

③LPCG(Low Power Clock Gating)

这个部分就是相当于一个时钟开关,控制着各种时钟的关闭和开始。

3 CCM的结构

下图为CCM模块的结构图。

从图中可以看到其实由几个模块共同组成,下面就来具体来介绍一下每个模块的作用。(红色框框的部分就是CCM)

CCM_ANALOG: CCM的模拟部分,它的主要作用为将低频率的时钟输入信号(通常就是外部晶振输入的信号)经过PLL电路倍频至较高频率然后输出下一个模块CCM_CLK_SWITCHER。

CCM_CLK_SWITCHER:该模块接收PLLs的信号,在结合PLLs的旁支电路输出开关时钟信号(pll3_sw_clk)至下一个模块CCM_CLK_ROOT_GEN。其中两个PLL配备了4个PFD(Phase Fractional Dividers),两者结合可生成多种频率的时钟信号。

CCM_CLK_ROOT_GEN:接收PLL和PFD信号, 然后经过处理(选择和分频)输出根时钟源至LPCG模块。

CCM_HND_SK:该模块负责时钟变换时时钟之间的同步。

CCM_LPM:低功耗模式管理,提供信号至CCM_CLK_LOGIC。

CCM_CLK_LOGIC:接收CCM_LPM和CCM_IP的信号生成时钟管理信号至LPCG模块,可以理解为时钟的开关信号,控制相关时钟开启和关闭来达到降低功耗的目的。

LPCG:接收时钟信号和时钟控制信号,输出系统各个部分时钟。

4 CCM的时钟树

CCM具体产生系统时钟的过程可以通过时钟树来进行描述,CCM的时钟树结构如下图所示:

可以看出系统时钟的产生大致有三个过程

5 时钟模块的具体功能

5.1 生成时钟

5.1.1 时钟源

①支持32kHz和32.768kHz外部低速晶振。

②支持外部24Mhz高速时钟,同时内部内嵌内部振荡器。

5.1.2 7个PLLs

RT1050内部有7个PLL,分别是PLL1~7, 其中PLL2和PLL3还配备PFD,,它们有着不同的应用,所以它们还分别被称为:

其中PLL还具有启用和禁用功能,PLL禁用和启用通过模拟模块完成。在使用模拟寄存器禁用PLL之前,软件应首先将从特定PLL生成的所有时钟移至另一个源。这个替代源可以是另一个PLL,或者由另一个PLL驱动的PFD。又或者,软件可以直接绕过PLL并使用PLL的参考时钟(通常为24 MHz)作为输出时钟,其中绕过PLL是通过设置该PLL的控制寄存器中的模拟BYPASS位来完成的。

5.1.3 PFD

每个PFD输出都会产生相关PLL VCO频率的分数倍数。在输出频率等于Fvco * 18 / N的情况下,N可以在12-35的范围内。PFD允许时钟频率改变,而不会强制重新锁定根PLL。

5.1.4 LPCG

LPCG将根时钟分成各个时钟分支提供给每个模块,其中每个分支都是可控,其控制信号可以来自以下四个来源:

①来自CCM的时钟使能信号

②来自模块的时钟使能信号

③来自复位控制器(SRC)的时钟使能信号

④来自FUSE的配置使能。

5.2 支持DVFS

RT1050支持DVFS。

5.3 低功耗模式

RT1050拥有三种低功耗模式。

①RUN Mode:这就是CPU正常运行的模式。

②WAIT Mode: 在这种模式下,CPU时钟被门控。所有其他时钟都可以正常工作,并且可以在所有ARM内核处于WFI且L2缓存和SCU处于空闲状态时通过对其CGR位进行编程来进行门控。

③STOP Mode: 在这种模式下,所有系统时钟包括CPU、系统总线和所有PLL一起停止。

6 相关寄存器

下面例举了CCM有关的寄存器,控制着时钟分支的分频以及使能。

| 绝对地址(hex) | 名称 | 宽度(bit) | 访问类型 | 重置值(hex) |

|---|---|---|---|---|

| 400F_C000 | CCM控制寄存器(CCM_CCR) | 32 | R / W | 0401_167Fh |

| 400F_C008 | CCM状态寄存器(CCM_CSR) | 32 | R | 0000_0010h |

| 400F_C00C | CCM时钟切换器寄存器(CCM_CCSR) | 32 | R / W | 0000_0100h |

| 400F_C010 | CCM ARM时钟根寄存器(CCM_CACRR) | 32 | R / W | 0000_0000h |

| 400F_C014 | CCM总线时钟分频寄存器(CCM_CBCDR) | 32 | R / W | 000B_8600h |

| 400F_C018 | CCM总线时钟多路复用器寄存器(CCM_CBCMR) | 32 | R / W | 2DA2_8324h |

| 400F_C01C | CCM串行时钟多路复用器寄存器1(CCM_CSCMR1) | 32 | R / W | 0490_0080h |

| 400F_C020 | CCM串行时钟多路复用器寄存器2(CCM_CSCMR2) | 32 | R / W | 0319_2C06h |

| 400F_C024 | CCM串行时钟分频器寄存器1(CCM_CSCDR1) | 32 | R / W | 0049_0B00h |

| 400F_C028 | CCM时钟分频寄存器(CCM_CS1CDR) | 32 | R / W | 0EC1_02C1h |

| 400F_C02C | CCM时钟分频寄存器(CCM_CS2CDR) | 32 | R / W | 0003_36C1h |

| 400F_C030 | CCM D1时钟分频寄存器(CCM_CDCDR) | 32 | R / W | 33F7_1F92h |

| 400F_C038 | CCM串行时钟分频器寄存器2(CCM_CSCDR2) | 32 | R / W | 0002_9B48h |

| 400F_C03C | CCM串行时钟分频寄存器3(CCM_CSCDR3) | 32 | R / W | 0001_4841h |

| 400F_C048 | CCM分频器握手进程内寄存器(CCM_CDHIPR) | 32 | R | 0000_0000h |

| 400F_C054 | CCM低功耗控制寄存器(CCM_CLPCR) | 32 | R / W | 0000_0079h |

| 400F_C058 | CCM中断状态寄存器(CCM_CISR) | 32 | W1C | 0000_0000h |

| 400F_C05C | CCM中断屏蔽寄存器(CCM_CIMR) | 32 | R / W | FFFF_FFFFh |

| 400F_C060 | CCM时钟输出源寄存器(CCM_CCOSR) | 32 | R / W | 000A_0001h |

| 400F_C064 | CCM通用寄存器(CCM_CGPR) | 32 | R / W | 0000_FE62h |

| 400F_C068 | CCM时钟门控寄存器0(CCM_CCGR0) | 32 | R / W | FFFF_FFFFh |

| 400F_C06C | CCM时钟门控寄存器1(CCM_CCGR1) | 32 | R / W | FFFF_FFFFh |

| 400F_C070 | CCM时钟门控寄存器3(CCM_CCGR3) | 32 | R / W | FFFF_FFCFh |

| 400F_C078 | CCM时钟门控寄存器4(CCM_CCGR4) | 32 | R / W | FFFF_FFFFh |

| 400F_C07C | CCM时钟门控寄存器5(CCM_CCGR5) | 32 | R / W | FFFF_FFFFh |

| 400F_C080 | CCM时钟门控寄存器6(CCM_CCGR6) | 32 | R / W | FFFF_FFFFh |

| 400F_C088 | CCM模块使能覆盖寄存器(CCM_CMEOR) | 32 | R / W | FFFF_FFFFh |

除了以上寄存器,还需要配置PLL以及PFD,这些则需要操作CCM_ANALOG相关的寄存器,这里就不一一例举了,大家可以参考官方Reference Manual。

6 应用实例

下面可以结合NXP官方的demo具体看一下RT1050时钟配置的实现过程。

①保存系统时钟频率和低速时钟频率,这样做的目的是为了以后涉及大系统时钟和低速时钟频率的计算。

②初始化内部时钟,随后初始化外部晶振,再将时钟源切换至外部晶振。

③设置PeriphClk2Mux和PeriphMux,确保ARM核在PLL工作前拥有稳定的时钟源。

④设置VDD_SOC为1.275V,这样做的目的是为了让AHB的频率能够达到600MHz。

⑤使能各个分支时钟,并且设置其分频。

⑥初始化PLL和PFD。

⑦切换各个分支时钟的时钟源。

void BOARD_BootClockRUN(void)

{

/* Init RTC OSC clock frequency. */

CLOCK_SetRtcXtalFreq(32768U);

/* Enable 1MHz clock output. */

XTALOSC24M->OSC_CONFIG2 |= XTALOSC24M_OSC_CONFIG2_ENABLE_1M_MASK;

/* Use free 1MHz clock output. */

XTALOSC24M->OSC_CONFIG2 &= ~XTALOSC24M_OSC_CONFIG2_MUX_1M_MASK;

/* Set XTAL 24MHz clock frequency. */

CLOCK_SetXtalFreq(24000000U);

/* Enable XTAL 24MHz clock source. */

CLOCK_InitExternalClk(0);

/* Enable internal RC. */

CLOCK_InitRcOsc24M();

/* Switch clock source to external OSC. */

CLOCK_SwitchOsc(kCLOCK_XtalOsc);

/* Set Oscillator ready counter value. */

CCM->CCR = (CCM->CCR & (~CCM_CCR_OSCNT_MASK)) | CCM_CCR_OSCNT(127);

/* Setting PeriphClk2Mux and PeriphMux to provide stable clock before PLLs are initialed */

CLOCK_SetMux(kCLOCK_PeriphClk2Mux, 1); /* Set PERIPH_CLK2 MUX to OSC */

CLOCK_SetMux(kCLOCK_PeriphMux, 1); /* Set PERIPH_CLK MUX to PERIPH_CLK2 */

/* Setting the VDD_SOC to 1.275V. It is necessary to config AHB to 600Mhz. */

DCDC->REG3 = (DCDC->REG3 & (~DCDC_REG3_TRG_MASK)) | DCDC_REG3_TRG(0x13);

/* Waiting for DCDC_STS_DC_OK bit is asserted */

while (DCDC_REG0_STS_DC_OK_MASK != (DCDC_REG0_STS_DC_OK_MASK & DCDC->REG0))

{

}

/* Set AHB_PODF. */

CLOCK_SetDiv(kCLOCK_AhbDiv, 0);

/* Disable IPG clock gate. */

CLOCK_DisableClock(kCLOCK_Adc1);

CLOCK_DisableClock(kCLOCK_Adc2);

CLOCK_DisableClock(kCLOCK_Xbar1);

CLOCK_DisableClock(kCLOCK_Xbar2);

CLOCK_DisableClock(kCLOCK_Xbar3);

/* Set IPG_PODF. */

CLOCK_SetDiv(kCLOCK_IpgDiv, 3);

/* Set ARM_PODF. */

CLOCK_SetDiv(kCLOCK_ArmDiv, 1);

/* Set PERIPH_CLK2_PODF. */

CLOCK_SetDiv(kCLOCK_PeriphClk2Div, 0);

/* Disable PERCLK clock gate. */

CLOCK_DisableClock(kCLOCK_Gpt1);

CLOCK_DisableClock(kCLOCK_Gpt1S);

CLOCK_DisableClock(kCLOCK_Gpt2);

CLOCK_DisableClock(kCLOCK_Gpt2S);

CLOCK_DisableClock(kCLOCK_Pit);

/* Set PERCLK_PODF. */

CLOCK_SetDiv(kCLOCK_PerclkDiv, 1);

/* Disable USDHC1 clock gate. */

CLOCK_DisableClock(kCLOCK_Usdhc1);

/* Set USDHC1_PODF. */

CLOCK_SetDiv(kCLOCK_Usdhc1Div, 1);

/* Set Usdhc1 clock source. */

CLOCK_SetMux(kCLOCK_Usdhc1Mux, 0);

/* Disable USDHC2 clock gate. */

CLOCK_DisableClock(kCLOCK_Usdhc2);

/* Set USDHC2_PODF. */

CLOCK_SetDiv(kCLOCK_Usdhc2Div, 1);

/* Set Usdhc2 clock source. */

CLOCK_SetMux(kCLOCK_Usdhc2Mux, 0);

/* In SDK projects, SDRAM (configured by SEMC) will be initialized in either debug script or dcd.

* With this macro SKIP_SYSCLK_INIT, system pll (selected to be SEMC source clock in SDK projects) will be left unchanged.

* Note: If another clock source is selected for SEMC, user may want to avoid changing that clock as well.*/

#ifndef SKIP_SYSCLK_INIT

/* Disable Semc clock gate. */

CLOCK_DisableClock(kCLOCK_Semc);

/* Set SEMC_PODF. */

CLOCK_SetDiv(kCLOCK_SemcDiv, 7);

/* Set Semc alt clock source. */

CLOCK_SetMux(kCLOCK_SemcAltMux, 0);

/* Set Semc clock source. */

CLOCK_SetMux(kCLOCK_SemcMux, 0);

#endif

/* In SDK projects, external flash (configured by FLEXSPI) will be initialized by dcd.

* With this macro XIP_EXTERNAL_FLASH, usb1 pll (selected to be FLEXSPI clock source in SDK projects) will be left unchanged.

* Note: If another clock source is selected for FLEXSPI, user may want to avoid changing that clock as well.*/

#if !(defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1))

/* Disable Flexspi clock gate. */

CLOCK_DisableClock(kCLOCK_FlexSpi);

/* Set FLEXSPI_PODF. */

CLOCK_SetDiv(kCLOCK_FlexspiDiv, 2);

/* Set Flexspi clock source. */

CLOCK_SetMux(kCLOCK_FlexspiMux, 1);

#endif

/* Disable CSI clock gate. */

CLOCK_DisableClock(kCLOCK_Csi);

/* Set CSI_PODF. */

CLOCK_SetDiv(kCLOCK_CsiDiv, 1);

/* Set Csi clock source. */

CLOCK_SetMux(kCLOCK_CsiMux, 0);

/* Disable LPSPI clock gate. */

CLOCK_DisableClock(kCLOCK_Lpspi1);

CLOCK_DisableClock(kCLOCK_Lpspi2);

CLOCK_DisableClock(kCLOCK_Lpspi3);

CLOCK_DisableClock(kCLOCK_Lpspi4);

/* Set LPSPI_PODF. */

CLOCK_SetDiv(kCLOCK_LpspiDiv, 4);

/* Set Lpspi clock source. */

CLOCK_SetMux(kCLOCK_LpspiMux, 2);

/* Disable TRACE clock gate. */

CLOCK_DisableClock(kCLOCK_Trace);

/* Set TRACE_PODF. */

CLOCK_SetDiv(kCLOCK_TraceDiv, 3);

/* Set Trace clock source. */

CLOCK_SetMux(kCLOCK_TraceMux, 0);

/* Disable SAI1 clock gate. */

CLOCK_DisableClock(kCLOCK_Sai1);

/* Set SAI1_CLK_PRED. */

CLOCK_SetDiv(kCLOCK_Sai1PreDiv, 3);

/* Set SAI1_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Sai1Div, 1);

/* Set Sai1 clock source. */

CLOCK_SetMux(kCLOCK_Sai1Mux, 0);

/* Disable SAI2 clock gate. */

CLOCK_DisableClock(kCLOCK_Sai2);

/* Set SAI2_CLK_PRED. */

CLOCK_SetDiv(kCLOCK_Sai2PreDiv, 3);

/* Set SAI2_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Sai2Div, 1);

/* Set Sai2 clock source. */

CLOCK_SetMux(kCLOCK_Sai2Mux, 0);

/* Disable SAI3 clock gate. */

CLOCK_DisableClock(kCLOCK_Sai3);

/* Set SAI3_CLK_PRED. */

CLOCK_SetDiv(kCLOCK_Sai3PreDiv, 3);

/* Set SAI3_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Sai3Div, 1);

/* Set Sai3 clock source. */

CLOCK_SetMux(kCLOCK_Sai3Mux, 0);

/* Disable Lpi2c clock gate. */

CLOCK_DisableClock(kCLOCK_Lpi2c1);

CLOCK_DisableClock(kCLOCK_Lpi2c2);

CLOCK_DisableClock(kCLOCK_Lpi2c3);

/* Set LPI2C_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Lpi2cDiv, 0);

/* Set Lpi2c clock source. */

CLOCK_SetMux(kCLOCK_Lpi2cMux, 0);

/* Disable CAN clock gate. */

CLOCK_DisableClock(kCLOCK_Can1);

CLOCK_DisableClock(kCLOCK_Can2);

CLOCK_DisableClock(kCLOCK_Can1S);

CLOCK_DisableClock(kCLOCK_Can2S);

/* Set CAN_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_CanDiv, 1);

/* Set Can clock source. */

CLOCK_SetMux(kCLOCK_CanMux, 2);

/* Disable UART clock gate. */

CLOCK_DisableClock(kCLOCK_Lpuart1);

CLOCK_DisableClock(kCLOCK_Lpuart2);

CLOCK_DisableClock(kCLOCK_Lpuart3);

CLOCK_DisableClock(kCLOCK_Lpuart4);

CLOCK_DisableClock(kCLOCK_Lpuart5);

CLOCK_DisableClock(kCLOCK_Lpuart6);

CLOCK_DisableClock(kCLOCK_Lpuart7);

CLOCK_DisableClock(kCLOCK_Lpuart8);

/* Set UART_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_UartDiv, 0);

/* Set Uart clock source. */

CLOCK_SetMux(kCLOCK_UartMux, 0);

/* Disable LCDIF clock gate. */

CLOCK_DisableClock(kCLOCK_LcdPixel);

/* Set LCDIF_PRED. */

CLOCK_SetDiv(kCLOCK_LcdifPreDiv, 1);

/* Set LCDIF_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_LcdifDiv, 3);

/* Set Lcdif pre clock source. */

CLOCK_SetMux(kCLOCK_LcdifPreMux, 5);

/* Disable SPDIF clock gate. */

CLOCK_DisableClock(kCLOCK_Spdif);

/* Set SPDIF0_CLK_PRED. */

CLOCK_SetDiv(kCLOCK_Spdif0PreDiv, 1);

/* Set SPDIF0_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Spdif0Div, 7);

/* Set Spdif clock source. */

CLOCK_SetMux(kCLOCK_SpdifMux, 3);

/* Disable Flexio1 clock gate. */

CLOCK_DisableClock(kCLOCK_Flexio1);

/* Set FLEXIO1_CLK_PRED. */

CLOCK_SetDiv(kCLOCK_Flexio1PreDiv, 1);

/* Set FLEXIO1_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Flexio1Div, 7);

/* Set Flexio1 clock source. */

CLOCK_SetMux(kCLOCK_Flexio1Mux, 3);

/* Disable Flexio2 clock gate. */

CLOCK_DisableClock(kCLOCK_Flexio2);

/* Set FLEXIO2_CLK_PRED. */

CLOCK_SetDiv(kCLOCK_Flexio2PreDiv, 1);

/* Set FLEXIO2_CLK_PODF. */

CLOCK_SetDiv(kCLOCK_Flexio2Div, 7);

/* Set Flexio2 clock source. */

CLOCK_SetMux(kCLOCK_Flexio2Mux, 3);

/* Set Pll3 sw clock source. */

CLOCK_SetMux(kCLOCK_Pll3SwMux, 0);

/* Init ARM PLL. */

CLOCK_InitArmPll(&armPllConfig_BOARD_BootClockRUN);

/* In SDK projects, SDRAM (configured by SEMC) will be initialized in either debug script or dcd.

* With this macro SKIP_SYSCLK_INIT, system pll (selected to be SEMC source clock in SDK projects) will be left unchanged.

* Note: If another clock source is selected for SEMC, user may want to avoid changing that clock as well.*/

#ifndef SKIP_SYSCLK_INIT

#if defined(XIP_BOOT_HEADER_DCD_ENABLE) && (XIP_BOOT_HEADER_DCD_ENABLE == 1)

#warning "SKIP_SYSCLK_INIT should be defined to keep system pll (selected to be SEMC source clock in SDK projects) unchanged."

#endif

/* Init System PLL. */

CLOCK_InitSysPll(&sysPllConfig_BOARD_BootClockRUN);

/* Init System pfd0. */

CLOCK_InitSysPfd(kCLOCK_Pfd0, 27);

/* Init System pfd1. */

CLOCK_InitSysPfd(kCLOCK_Pfd1, 16);

/* Init System pfd2. */

CLOCK_InitSysPfd(kCLOCK_Pfd2, 24);

/* Init System pfd3. */

CLOCK_InitSysPfd(kCLOCK_Pfd3, 16);

/* Disable pfd offset. */

CCM_ANALOG->PLL_SYS &= ~CCM_ANALOG_PLL_SYS_PFD_OFFSET_EN_MASK;

#endif

/* In SDK projects, external flash (configured by FLEXSPI) will be initialized by dcd.

* With this macro XIP_EXTERNAL_FLASH, usb1 pll (selected to be FLEXSPI clock source in SDK projects) will be left unchanged.

* Note: If another clock source is selected for FLEXSPI, user may want to avoid changing that clock as well.*/

#if !(defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1))

/* Init Usb1 PLL. */

CLOCK_InitUsb1Pll(&usb1PllConfig_BOARD_BootClockRUN);

/* Init Usb1 pfd0. */

CLOCK_InitUsb1Pfd(kCLOCK_Pfd0, 33);

/* Init Usb1 pfd1. */

CLOCK_InitUsb1Pfd(kCLOCK_Pfd1, 16);

/* Init Usb1 pfd2. */

CLOCK_InitUsb1Pfd(kCLOCK_Pfd2, 17);

/* Init Usb1 pfd3. */

CLOCK_InitUsb1Pfd(kCLOCK_Pfd3, 19);

/* Disable Usb1 PLL output for USBPHY1. */

CCM_ANALOG->PLL_USB1 &= ~CCM_ANALOG_PLL_USB1_EN_USB_CLKS_MASK;

#endif

/* DeInit Audio PLL. */

CLOCK_DeinitAudioPll();

/* Bypass Audio PLL. */

CLOCK_SetPllBypass(CCM_ANALOG, kCLOCK_PllAudio, 1);

/* Set divider for Audio PLL. */

CCM_ANALOG->MISC2 &= ~CCM_ANALOG_MISC2_AUDIO_DIV_LSB_MASK;

CCM_ANALOG->MISC2 &= ~CCM_ANALOG_MISC2_AUDIO_DIV_MSB_MASK;

/* Enable Audio PLL output. */

CCM_ANALOG->PLL_AUDIO |= CCM_ANALOG_PLL_AUDIO_ENABLE_MASK;

/* Init Video PLL. */

uint32_t pllVideo;

/* Disable Video PLL output before initial Video PLL. */

CCM_ANALOG->PLL_VIDEO &= ~CCM_ANALOG_PLL_VIDEO_ENABLE_MASK;

/* Bypass PLL first */

CCM_ANALOG->PLL_VIDEO = (CCM_ANALOG->PLL_VIDEO & (~CCM_ANALOG_PLL_VIDEO_BYPASS_CLK_SRC_MASK)) |

CCM_ANALOG_PLL_VIDEO_BYPASS_MASK | CCM_ANALOG_PLL_VIDEO_BYPASS_CLK_SRC(0);

CCM_ANALOG->PLL_VIDEO_NUM = CCM_ANALOG_PLL_VIDEO_NUM_A(0);

CCM_ANALOG->PLL_VIDEO_DENOM = CCM_ANALOG_PLL_VIDEO_DENOM_B(1);

pllVideo = (CCM_ANALOG->PLL_VIDEO & (~(CCM_ANALOG_PLL_VIDEO_DIV_SELECT_MASK | CCM_ANALOG_PLL_VIDEO_POWERDOWN_MASK))) |

CCM_ANALOG_PLL_VIDEO_ENABLE_MASK |CCM_ANALOG_PLL_VIDEO_DIV_SELECT(31);

pllVideo |= CCM_ANALOG_PLL_VIDEO_POST_DIV_SELECT(1);

CCM_ANALOG->MISC2 = (CCM_ANALOG->MISC2 & (~CCM_ANALOG_MISC2_VIDEO_DIV_MASK)) | CCM_ANALOG_MISC2_VIDEO_DIV(3);

CCM_ANALOG->PLL_VIDEO = pllVideo;

while ((CCM_ANALOG->PLL_VIDEO & CCM_ANALOG_PLL_VIDEO_LOCK_MASK) == 0)

{

}

/* Disable pfd offset. */

CCM_ANALOG->PLL_VIDEO &= ~CCM_ANALOG_PLL_VIDEO_PFD_OFFSET_EN_MASK;

/* Disable bypass for Video PLL. */

CLOCK_SetPllBypass(CCM_ANALOG, kCLOCK_PllVideo, 0);

/* DeInit Enet PLL. */

CLOCK_DeinitEnetPll();

/* Bypass Enet PLL. */

CLOCK_SetPllBypass(CCM_ANALOG, kCLOCK_PllEnet, 1);

/* Set Enet output divider. */

CCM_ANALOG->PLL_ENET = (CCM_ANALOG->PLL_ENET & (~CCM_ANALOG_PLL_ENET_DIV_SELECT_MASK)) | CCM_ANALOG_PLL_ENET_DIV_SELECT(1);

/* Enable Enet output. */

CCM_ANALOG->PLL_ENET |= CCM_ANALOG_PLL_ENET_ENABLE_MASK;

/* Enable Enet25M output. */

CCM_ANALOG->PLL_ENET |= CCM_ANALOG_PLL_ENET_ENET_25M_REF_EN_MASK;

/* DeInit Usb2 PLL. */

CLOCK_DeinitUsb2Pll();

/* Bypass Usb2 PLL. */

CLOCK_SetPllBypass(CCM_ANALOG, kCLOCK_PllUsb2, 1);

/* Enable Usb2 PLL output. */

CCM_ANALOG->PLL_USB2 |= CCM_ANALOG_PLL_USB2_ENABLE_MASK;

/* Set preperiph clock source. */

CLOCK_SetMux(kCLOCK_PrePeriphMux, 3);

/* Set periph clock source. */

CLOCK_SetMux(kCLOCK_PeriphMux, 0);

/* Set periph clock2 clock source. */

CLOCK_SetMux(kCLOCK_PeriphClk2Mux, 0);

/* Set per clock source. */

CLOCK_SetMux(kCLOCK_PerclkMux, 0);

/* Set lvds1 clock source. */

CCM_ANALOG->MISC1 = (CCM_ANALOG->MISC1 & (~CCM_ANALOG_MISC1_LVDS1_CLK_SEL_MASK)) | CCM_ANALOG_MISC1_LVDS1_CLK_SEL(0);

/* Set clock out1 divider. */

CCM->CCOSR = (CCM->CCOSR & (~CCM_CCOSR_CLKO1_DIV_MASK)) | CCM_CCOSR_CLKO1_DIV(0);

/* Set clock out1 source. */

CCM->CCOSR = (CCM->CCOSR & (~CCM_CCOSR_CLKO1_SEL_MASK)) | CCM_CCOSR_CLKO1_SEL(1);

/* Set clock out2 divider. */

CCM->CCOSR = (CCM->CCOSR & (~CCM_CCOSR_CLKO2_DIV_MASK)) | CCM_CCOSR_CLKO2_DIV(0);

/* Set clock out2 source. */

CCM->CCOSR = (CCM->CCOSR & (~CCM_CCOSR_CLKO2_SEL_MASK)) | CCM_CCOSR_CLKO2_SEL(18);

/* Set clock out1 drives clock out1. */

CCM->CCOSR &= ~CCM_CCOSR_CLK_OUT_SEL_MASK;

/* Disable clock out1. */

CCM->CCOSR &= ~CCM_CCOSR_CLKO1_EN_MASK;

/* Disable clock out2. */

CCM->CCOSR &= ~CCM_CCOSR_CLKO2_EN_MASK;

/* Set SAI1 MCLK1 clock source. */

IOMUXC_SetSaiMClkClockSource(IOMUXC_GPR, kIOMUXC_GPR_SAI1MClk1Sel, 0);

/* Set SAI1 MCLK2 clock source. */

IOMUXC_SetSaiMClkClockSource(IOMUXC_GPR, kIOMUXC_GPR_SAI1MClk2Sel, 0);

/* Set SAI1 MCLK3 clock source. */

IOMUXC_SetSaiMClkClockSource(IOMUXC_GPR, kIOMUXC_GPR_SAI1MClk3Sel, 0);

/* Set SAI2 MCLK3 clock source. */

IOMUXC_SetSaiMClkClockSource(IOMUXC_GPR, kIOMUXC_GPR_SAI2MClk3Sel, 0);

/* Set SAI3 MCLK3 clock source. */

IOMUXC_SetSaiMClkClockSource(IOMUXC_GPR, kIOMUXC_GPR_SAI3MClk3Sel, 0);

/* Set MQS configuration. */

IOMUXC_MQSConfig(IOMUXC_GPR,kIOMUXC_MqsPwmOverSampleRate32, 0);

/* Set ENET Tx clock source. */

IOMUXC_EnableMode(IOMUXC_GPR, kIOMUXC_GPR_ENET1RefClkMode, false);

/* Set GPT1 High frequency reference clock source. */

IOMUXC_GPR->GPR5 &= ~IOMUXC_GPR_GPR5_VREF_1M_CLK_GPT1_MASK;

/* Set GPT2 High frequency reference clock source. */

IOMUXC_GPR->GPR5 &= ~IOMUXC_GPR_GPR5_VREF_1M_CLK_GPT2_MASK;

/* Set SystemCoreClock variable. */

SystemCoreClock = BOARD_BOOTCLOCKRUN_CORE_CLOCK;

}