Transpose转置SRAM(TSRAM)论文阅读简记

1、A 0.62mW Ultra-Low-Power Convolutional-NeuralNetwork Face-Recognition Processor and a CIS Integrated with Always-On Haar-Like Face Detector

isscc2017

下图即为TSRAM的具体结构,添加了一个解耦MOS管,其源端、漏断分别连接到图中所示的蓝色与红色线;

与正常SRAM一样采用行读取模式时,这两根线分别为H_RDWL与H_RDBL;

此时进行读取,则H_RDBL与正常位线一样预充电到高电平,根据交叉耦合的反相器中存储的是0还是1来决定这根线是否放电;

猜测此时的H_RDWL为低电平;

进行TSRAM的列读取模式时,则此时交换两根线的角色,分别成为下面括号中的信号;

此时猜测V_RDWL预充电到高电平,V_RDBL仍为低电平,则此时可以根据反向器中存储值在V_RDBL上得到不同的电压差值;

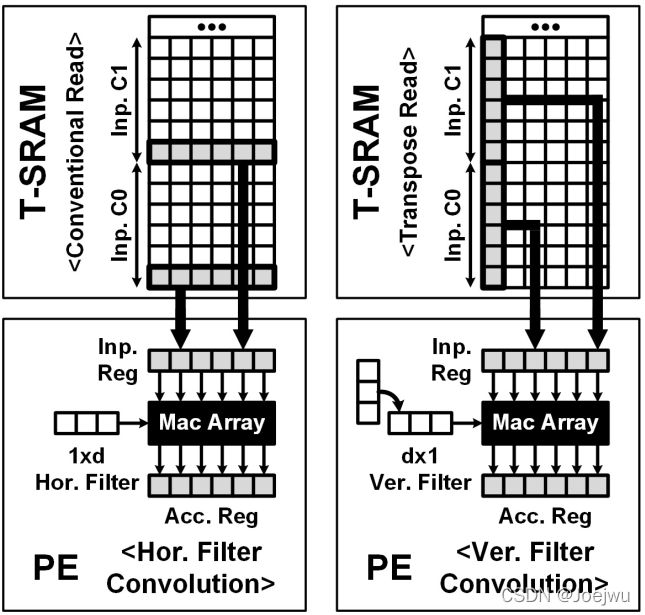

此图中即为正常模式下的行读取与TSRAM下的列读取模式;

2、A 65nm 0.39-to-140.3TOPS/W 1-to-12b Unified NeuralNetwork Processor Using Block-Circulant-Enabled Transpose-Domain Acceleration with 8.1× Higher TOPS/mm2and 6T HBST-TRAM-Based 2D Data-Reuse Architecture

2019 ISSCC

SRAM还是6Tcell,只不过加了几根信号线以及一个控制单元即HBST cell;

所以该SRAM能够实现转置,工作在两种模式下:正常模式读写、转置模式读写;

所以也就能够水平写进去,然后垂直着读出来;

正常读写模式:

由WL\HWL\LBL\LBLB\HGBL\HGBLB信号来完成控制;

尽管一个局部单元阵列中有8个SRAM存储单元,但是无论是哪种模式下,每次也只能读写这个单元阵列中的一个存储单元;

转置读写模式:

由VWL\WL\HWL\LBL\LBLB\VGBL\VGBLB信号来完成控制;

这里用到的HWL主要是为了在每次读写完之后给LBL\LBLB充电;

而且这个TSRAM与上面2017年的对比如下;主要是这个是基于block的转置,而2017年的属于是基于cell实现的转置;

然后19年的可以实现读写,而17年的只能读,但是很多时候是不是我们只需要有读的功能就行了;

3、A 28nm 15.59µJ/Token Full-Digital Bitline-Transpose CIM-Based Sparse Transformer Accelerator with Pipeline/Parallel Reconfigurable Modes

2022 ISSCC

这里实现的是相当于将原本的CIM+Transpose buffer集成到一起;

然后实现的这个BLT-CIM, 在原本的CIM单元阵列中添加上几个外围控制电路,包括每个SRAM单元都需要添加一个4T的NOR或非门;

因为这里的位线都是被水平放置的,所以能够实现按列写入,然后在按行进行乘累加计算并送到下面的Macro累加器中进行计算;

因为现在需要的不是集合有存内计算功能的转置SRAM,而只想SRAM能实现一下转置,所以这种较为复杂的方案就不予考虑了;

4、A 16Kb Transpose 6T SRAM In-Memory-Computing Macro based on Robust Charge-Domain Computing

2021 ASSCC

这里说的转置6T SRAM然后来实现存内计算;

先看一下这个结构,是128*128的SRAM cell组成,然后水平方向分成8组,竖直方向分为16组,但是还是按照竖直方向分的16组的每组称之为local CIM cell;

然后在FF前向的时候,即128列同时得到输入,先以一行来看,这一行的所有128个SRAM cell都进行binary的乘法,然后控制一下这一行cell之间的连通,实现电荷共享,此即完成了乘之后的累加操作;

然后剩下的15行local CIM都执行同样的操作,最终即得到16个乘累加的结果,且是排在列方向上,将他们全部读出来,此即文中所说的转置;

BP暂且不考虑;

5、Deep Neural Network Training Accelerator Designs in ASIC and FPGA

2020 ISOCC

文中提出,前向时非转置与反向时转置的存储与访问,均可以在现有的SRAM上做,就不改动原有的SRAM,即实现转置;

具体做法就是将卷积核的每一行,都如上图中左边所示的,存储成一个循环阵列的形式,然后如果前向的时候就直接读取一行;

如果是反向的时候,需要转置后的结果,那就在整个矩阵的每一列都读取一个数字,如图中蓝色框所示;

好像确实可以,但是是不是需要消耗很大的存储空间啊?

以上仅作为该方向探索的一点简单记录。