基于FPGA的幅频均衡带通滤波器的设计

目录

1.算法描述

2.仿真效果预览

3.MATLAB核心程序

4.完整MATLAB

1.算法描述

数字通信系统中,由于多径传输、信道衰落等影响,在接收端会产生严重的码间干扰,增大误码率。为了克服码间干扰,提高通信系统的性能,在接收端需采用均衡技术。均衡是指对信道特性的均衡,即接收端的均衡器产生与信道特性相反的特性,用来减小或消除因信道的时变多径传播特性引起的码间干扰。幅频均衡就是在幅度和频率上的均衡。

数字幅频均衡功率放大器设计,其难点主要数字幅频均衡。采用何种方案以及方案的优劣直接决定了能够达到指标的高低和实现起来的难易程度,下面我们就数字幅频均衡方案选择进行介绍。

均衡器用于实现对带阻网络频率特性的补偿,以获得平坦的幅频响应。

方案一:采用自适应滤波器。它以最小均方误差为准则,根据输入信号的改变,通过滤波器输出信号与参考信号之间的误差,自动调整滤波器的系数,以达到时变最佳滤波器,适合于未知信号或非平稳信号的处理。

方案二:采用无限冲激响应滤波器(IIR)。IIR滤波器设计简单,实现的阶数较低。但它具有非线性相位,且由于其为反馈型结构(即传递函数存在极点),对滤波器参数的精度要求较高,否则可能引起振荡或发散。

方案三:采用有限冲激响应滤波器(FIR)。FIR滤波器采用非递归结构,可以得到严格的线性相位,运算误差较小,且传递函数不存在极点,稳定性好。但与IIR滤波器相比,相同条件下需要的阶数更高,导致延迟时间较长,而且对于硬件资源会有更高的要求。

由于本系统对固定网络进行幅频均衡,方案一的优势无法体现。鉴于FPGA具有快速的数据处理能力,为保证系统的稳定性,同时又要考虑系统资源的可行性,选取方案三。

带通滤波器在数字幅频均衡功率放大器中一个重要的组成部分,在介绍带通滤波器之前,我们首先来详细介绍一下数字幅频均衡功率放大器。

本系统要求的指标为:

本题要求在输入电压有效值为5mV的条件下,放大倍数达到400倍。而且20Hz到20kHz衰减不能超过1dB。-1 dB转化为信号幅值变化为11%,可以说指标要求很高。我们可以选择使用PGA或AD620实现这一指标。

根据以上分析,系统的整体框图如图4-2所示。输入信号首先通过前置放大电路放大到一定幅度,经过带阻网络后,信号的幅频特性发生变化。由于AD输入幅度限制,信号先经过衰减网络衰减两倍,再经过抗混叠滤波并使用AD对输入信号进行采样,将采样结果送入FPGA做幅频均衡。最后通过DA输出并滤波,经过D类功放后即可得到大功率信号。

数字幅频均衡模块的原理图如图4-3所示,如果要实现对带阻网络的完全补偿,那么FIR滤波器应与带阻网络互为逆系统.带阻网络的系统函数可以通过点频法测得,然后使用MATLAB求出加窗后FIR滤波器应该具有的单位脉冲响应。因为FIR系统具有线性相位特性,所以由其幅频响应就可以求得其系统函数。

·D/A输出电路设计

根据题目的指标及系统频率的要求,我们需要一款频率超过40KHz的模数输出芯片。DAC904是一款14bits、最高采样频率165MHz的的DA器件,由于以前使用过该芯片,所以仍选用DAC904作为数模输出芯片。

·功率放大电路设计

D类功放第一部分为调制器,输入信号接比较器的正输入端,与三角波相比较。当正端上的电位高于负端三角波电位时,比较器输出为高电平,反之则输出低电平。这样,比较器输出的波形就是一个脉冲宽度被音频信号幅度调制后的波形,称为SPWM波。D类功放后级输出电路是一个脉冲控制的大电流开关放大器,正半周期比较器输出高电平,MOSFET晶体管Q1导通,且Q2截止,负半周期比较器输出高电平Q2导通,且Q1截止,这样它就把比较器输出的PWM信号变成高电压、大电流的大功率PWM信号,最后只需要通过一个二阶低通滤波器就可以把声音信息还原出来。

以上就是这个系统的基本结构,在本课题中,我们主要需要设计的是其带通滤波器部分,即数字幅频均衡部分。

对于这个部分,一般有如下的几种方案:

方案一:理论推导带阻网络的传递函数,得出带阻网络的系统结构,然后对实际的带阻网络进行模式识别,得出其实际的传递函数。对输入的信号在时域进行频率测量,根据传递函数计算得出其幅频衰减的程度,然后对其损失的幅度进行补偿。

方案二:利用FFT算法分析信号的频谱,得到信号的频率值,然后再根据带阻网络的传输特性进行补偿。

方案三:对所给的带阻网络电路进行仿真,求出其幅频特性曲线及中心频率,并以实际带阻网络验证其准确性。运用数字信号处理技术,利用可编程逻辑器件,构建相同于带阻网络对应的数字带通滤波器,对通过带阻网络所衰减的幅度进行补偿。

由于方案一和方案二对处理器的速度有很大要求,而且实时性比较高,很难达到同步输出,而方案三采用FPGA并行处理的优势,在其内部用硬件构建带通滤波器,可实时的对信号进行数字幅频均衡。

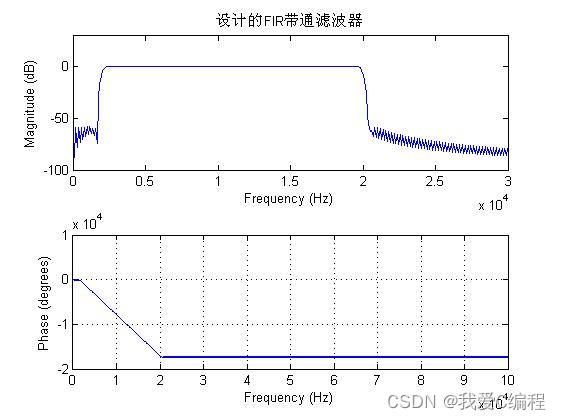

2.仿真效果预览

matlab2022a仿真结果如下:

3.MATLAB核心程序

module FIR_module(

i_clk,

i_rst,

i_data,

o_data

);

input i_clk;

input i_rst;

input signed[15:0] i_data;

output signed[34:0] o_data;

firs firs_u(

.clk (i_clk),

.reset_n (i_rst),

.ast_sink_data (i_data),

.ast_sink_valid (1'b1),

.ast_source_ready (1'b1),

.ast_sink_error (2'b00),

.ast_source_data (o_data),

.ast_sink_ready (),

.ast_source_valid (),

.ast_source_error ()

);

endmodule

A1404.完整MATLAB

V