【Xilinx Vivado时序分析/约束系列7】FPGA开发时序分析/约束-FPGA单沿采样数据input delay时序约束实操

目录

问题引入

分析问题

实际工程解决

新建工程

顶层代码

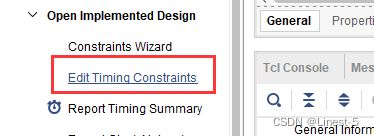

编辑时序约束

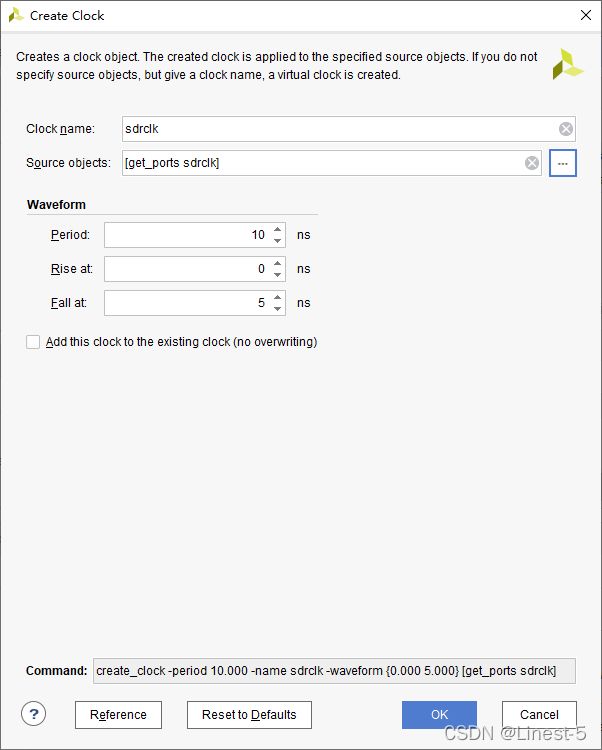

生成时序报告

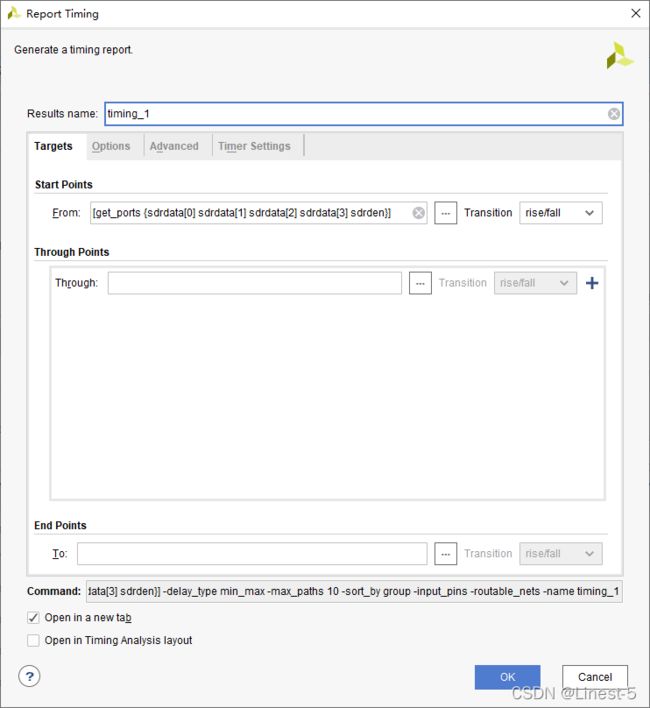

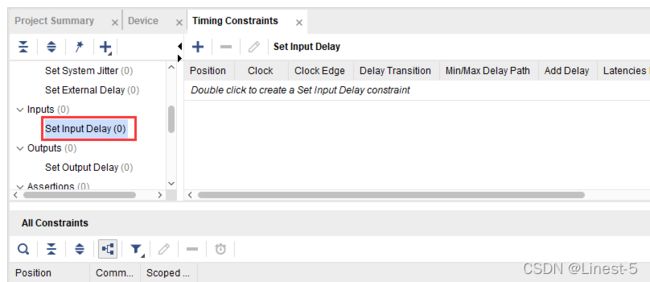

设置输入延迟

具体分析

Data Path:表示数据实际到达的时间

Destination Clock Path:目的时钟路径

往期系列博客

根据第六节的内容,本篇文章以实操讲解。

本次以实际工程进行(Vivado)

问题引入

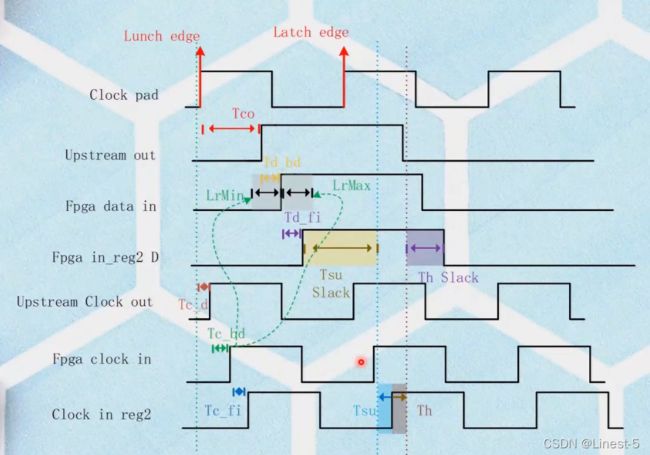

FPGA管脚处时钟上升沿到达之后3ns是数据到达时间,时钟周期为10ns,如何约束input delay和察看时序报告?

分析问题

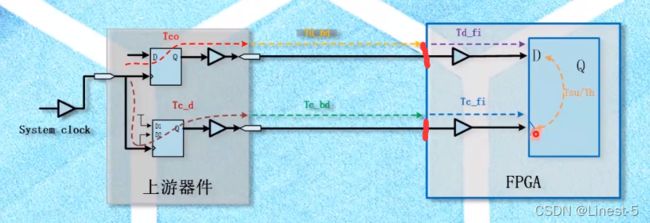

从上面的时序图结合题目可以知道,因为FPGA管脚处时钟上升沿到达之后3ns是数据到达时间,则会就说明不存在Lrmin和Lrmax,也就是不考虑PCB布线长短的问题,在FPGA clock in的上升沿到来之后的3ns,FPGA data in数据拉高到来。

实际工程解决

新建工程

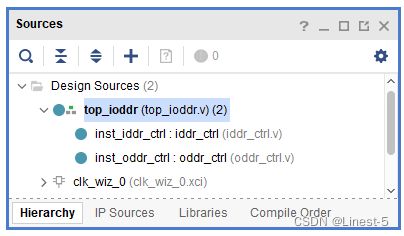

基本内容和之前分析建立时间保持时间差不多,只不过在顶层文件代码中多了几路时钟、使能信号、数据等,并在最后打了两拍。

顶层代码

module top_ioddr(

input wire rx_clk,

input wire rx_ctrl,

input wire [3:0] rx_dat,

//tx

output wire tx_clk,

output wire [3:0] tx_d,

output wire tx_dv,

input wire sdrclk,

input wire [3:0] sdrdata,

input wire sdrden,

output reg tout

);

wire rst;

wire rx_clk_90;

wire rx_en;

wire [7:0] rx_data;

reg tx_en1,tx_en2;

reg [7:0] tx_data1,tx_data2;

assign rst =0;

assign rx_clk_90 = rx_clk;

/*

clk_wiz_0 clk_gen0

(

// Clock out ports

.clk_out1(rx_clk_90), // output clk_out1

// Clock in ports

.clk_in1(rx_clk)); // input clk_in1

*/

always @(posedge rx_clk_90 or posedge rst) begin

if (rst == 1'b1) begin

tx_data1 <= 'd0;

end

else if (rx_en == 1'b1) begin

tx_data1 <= rx_data+ rx_data -1;

end

end

always @(posedge rx_clk_90 or posedge rst) begin

if (rst == 1'b1) begin

tx_data2 <= 'd0;

end

else if (tx_en1 == 1'b1) begin

tx_data2 <= tx_data1+ tx_data1 -5;

end

end

always @(posedge rx_clk_90 ) begin

tx_en1 <= rx_en;

end

always @(posedge rx_clk_90 ) begin

tx_en2 <= tx_en1;

end

iddr_ctrl inst_iddr_ctrl

(

.rx_clk_90 (rx_clk_90),

.rst (rst),

.rx_dat (rx_dat),

.rx_ctrl (rx_ctrl),

.rx_en (rx_en),

.rx_data (rx_data)

);

oddr_ctrl inst_oddr_ctrl

(

.sclk (rx_clk_90),

.tx_dat (tx_data2),

.tx_en (tx_en2),

.tx_c (rx_clk_90),

.tx_data (tx_d),

.tx_dv (tx_dv),

.tx_clk (tx_clk)

);

//sdr clock domain

reg [3:0] sdrdata_r1,sdrdata_r2;

reg sdrden_r1,sdrden_r2;

//打两拍

always @(posedge sdrclk ) begin

{sdrdata_r2,sdrdata_r1} <= {sdrdata_r1,sdrdata};

end

always @(posedge sdrclk ) begin

{sdrden_r2,sdrden_r1} <= {sdrden_r1,sdrden};

end

always @(posedge sdrclk) begin

if(sdrden_r2 == 1'b1) begin

tout <= (&sdrdata_r1)|(&sdrdata_r2);

end

else begin

tout <= (^sdrdata_r2);

end

end

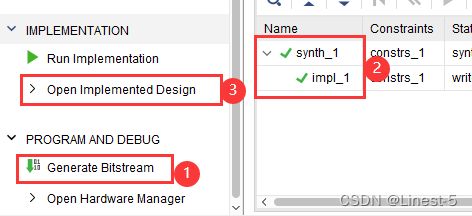

endmodule和之前的操作类似,生成比特流文件,然后打开布线设计。

编辑时序约束

这里大部分的操作和之前建立时间和保持时间约束的操作差不多,这里不多阐述

输入的sdrclk约束设置如下图,根据题目条件周期为10ns,设置约束时钟名字和所对应的时钟保持一致,也可以自己设置,并且让他对应sdrclk。

生成时序报告

点击report timing,进行添加四个输出数据以及使能信号

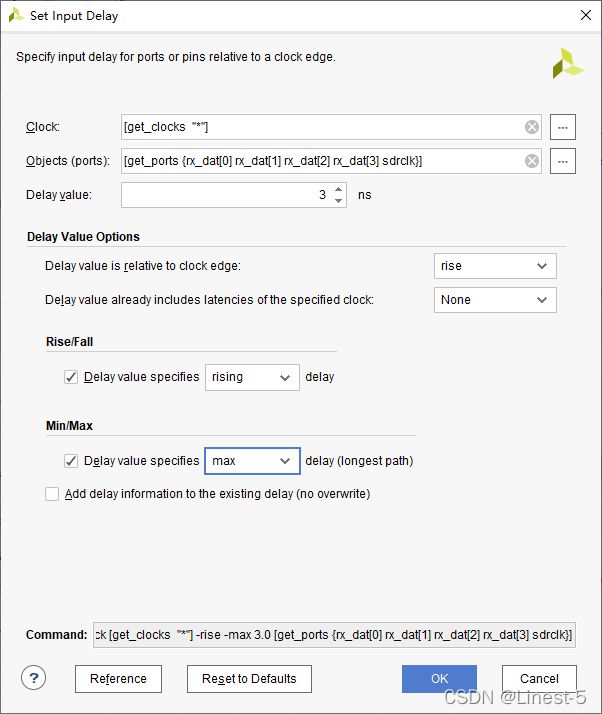

设置输入延迟

按照题目要求,分别设置最大输入延时和最小输入延时,根据题目意思,最大和最小是一致的,都是3ns

延时值相对于时钟沿:rise 上升沿(和时序图保持一致)

延时值已经包含特定的时钟延时:none 无

设置为上升沿延时

此设置为最大延时量(另一个设置为最小延时量)

注:add delay information to the existing delay(no overwrite)添加延时信息到现有的延时中(不覆盖)

这个指的是如果你第一次设置为上升沿延时,第二次设置为下降沿延时,如果要想第二次的延时不对第一次的设置覆盖,这时候就需要勾选,如果只是改变延时量,这个是互不影响的,这个情况是不需要勾选的。

由于更改了输入延时,所以需要重新report timing

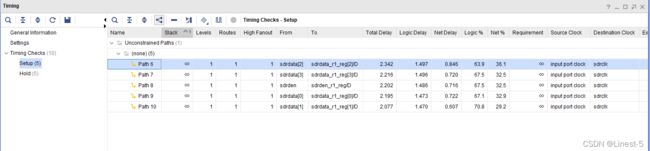

可以看到原来没有添加输入延时的时候,每条路径的slack(建立时间余量)都是无穷大,这是因为我们设置约束的时候,洗头膏默认帮我们设置的很大,避免报错。

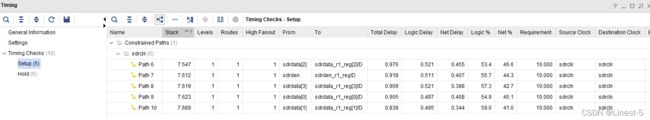

在添加约束后,就可以看到slack不再是无穷大,而是有了一定的限制值。

具体分析

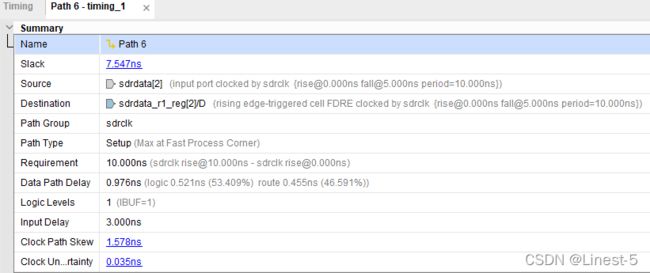

随意双击点开一条路径进行分析(以path 6为例)

Summary:汇总了一些信息

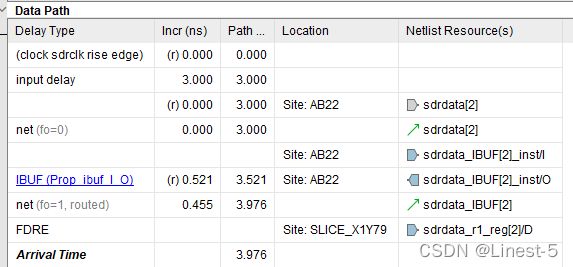

Data Path:表示数据实际到达的时间

input delay:这是刚刚添加的约束,输入延时3ns;

IBUF(Prop ibuf I O)

IBUF的输入到输出所经历的延时0.521ns;

net:PCB布线的延时时间0.455ns;

总共合计数据实际到达的时间为3.976ns。

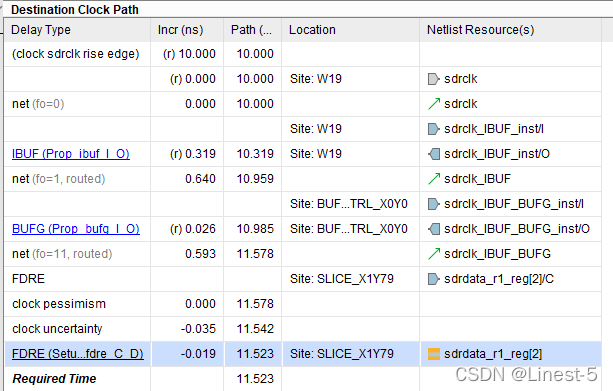

Destination Clock Path:目的时钟路径

clock sdrclk rise edge:采样时钟为源时钟的一个时钟周期之后,周期为10ns;

IBUF(Prop ibuf I O)

IBUF的输入到输出所经历的延时0.319ns;

net:PCB布线延时0.640ns;

BUFG(Prop bufg I O)

BUFG的输入到输出所经历的延时0.026ns;

net:PCB布线延时0.593ns;

clock pessimism:这个参数由于没有约束,所以为0;

clock uncertainty:时钟的不确定性,这个有芯片自身决定。

总共合计数据所被要求到达的时间为11.523ns。

根据建立时间的余量(setup slack)的定义

建立时间余量=数据所被要求到达的时间 - 数据实际到达的时间

可以验证输入延迟约束加上之后是符合预期的。

至此,就把通过添加输入延迟,其中建立时间余量的部分分析完毕,

在保持时间余量的操作和建立时间余量大同小异,分析方法也是近似。

往期系列博客

【Xilinx Vivado时序分析/约束系列1】FPGA开发时序分析/约束-寄存器间时序分析

【Xilinx Vivado时序分析/约束系列2】FPGA开发时序分析/约束-建立时间

【Xilinx Vivado时序分析/约束系列3】FPGA开发时序分析/约束-保持时间

【Xilinx Vivado时序分析/约束系列4】FPGA开发时序分析/约束-实验工程上手实操

【Xilinx Vivado时序分析/约束系列5】FPGA开发时序分析/约束-IO时序分析

【Xilinx Vivado时序分析/约束系列6】FPGA开发时序分析/约束-IO时序输入延时