浅谈pcie硬件验证方案

目录

1.1.pcie起源

1.2.pcie应用

2.1.pcie架构介绍

2.2.pcie耦合电容与detect

2.3.pcie均衡技术

3.1.Chip-to-Chip测试指标

3.1.1.无源参数指标

3.1.1.有源参数指标

3.2.无源+有源仿真

无源参数仿真

有源仿真

3.4.有源信号测试

100MHz时钟测试

PCIE data lane信号测试

- pcie概述

本章主要介绍pcie总线的起源、发展、以及目前在市面上以不同形式、不同行业呈现的应用。

1.1.pcie起源

PCIE全称peripheral component interconnect express,是为了取代跟不上时代发展的PCI提出的,并在相关技术的不断发展中迸发出来了无限潜力。

PCIE脱胎与PCI总线,在物理结构上的区别在于一个是并行的,一个是串行的。在协议上PCIE兼容PCI,并在其基础上不断升级,并在升级的过程中逐渐摆脱PCI的身影。

Pcie的发展过程中伴随着行业巨头博弈和改变的血泪史,一步一步成长起来的。第一代ISA总线与1981年始于IBM的PCXT机型上,带宽是4.77MB/s。经过一代的发展,IBM把位宽提升了一倍,速率提升到8MB/s。但是,IBM为了垄断,在PS/2产品线上推出了MCA总线。迫使其他厂商联合起来推出了EISA总线,在这期间,速率提升非常缓慢。

直到486时代,随着cpu主频提升到33MHz,发展出了兼容速率的VLB总线。接踵而来的奔腾时代又迅速的淘汰了VLB。Intel在1992年推出了PCI总线,兼容奔腾66MHz的内核,并召集各位小伙伴成立了PCI-sig联盟,负载标准的制定和推广。

12年后,Intel再一次革了PCI的命。2004年,正式推出了pcie,经历了几代的发展,目前已经发展到gen5.

1.2.pcie应用

随着电子化、智能化的发展,Pcie接口几乎应用在各个行业,通信、汽车、家电、PC等。Pcie也衍生出了一些兄弟接口,如mipi M-Phy、M.2、SATA等。

Pcie物理接口也各种样式,在PCIe-SIG给出的定义中有Chip-to-Chip、board-to-board、Card Electro-Mechanical、U.2等各种样式。

- pcie物理层技术解析

根据PCIE应用场景的的不同,应用的物理层测试标准和架构也会有变化,本章主要从物理层技术来介绍pcie总线。

2.1.pcie架构介绍

一个典型的结构是一个root port和一个endpoint直接组成一个点对点连接对,而Switch可以同时连接几个endpoint。一个root port和一个endpoint对就需要一个单独的PCI bus。而PCI是在同一个总线上的设备共享同一个bus number。过去主板上的PCI插槽都公用一个PCI bus。

PCIe的连线是由不同的lane来连接的,这些lane可以合在一起提供更高的带宽。譬如两个1lane可以合成2lane的连接,写作x2。两个x2可以变成x4,最大直到x16,来满足不同的带宽需求。

PCIE时钟支持3种架构,最常用的是同源时钟、经过分频器传输给CR和EP,这种架构支持SSC扩频时钟。第二种是分别使用两个不同源的100MHz时钟;第三章是只有CR有pcie时钟,EP经过CDR恢复后的时钟用例采用和工pcie device工作。

2.2.pcie耦合电容与detect

PCIE Detect原理

Detect通过集成在发送器(Transmitter)中的接收器检测(Receiver Detection)电路实现,电路的功能在于检测接收器内的等效对地阻抗ZRX是否在40 Ω-60 Ω之间。PCIe总线支持热插拔,因此当对端设备没有插入时其ZRX为开路,则检测电路可以据此判断出对端无设备;而板内PCIe链路的芯片在复位状态或未上电等异常状态下其阻抗也会呈开路状态。

在位检测步骤如下:

发送器的输出保持在稳定的共模电平上;

发送器对共模输出差分对的D+和D-充电;

检测电路通过线路上电平变换的速率来判断接收器是否在位。

由图1可知若对端设备不在位,则CTX之后的电路不存在,此时的充电时间常数为ZTX (CTX + Cpad + Cinterconnect),其中ZTX为发送器内阻,约为50Ω,CTX开路,Cpad为芯片引脚的寄生电容,Cinterconnect为链路的寄生电容,这两个参数都极小(pF级别)因而此时充电时间常数较低。

若对端设备在位,则充电时间常数约为ZTX (CTX + Cpad + Cinterconnect),其中CTX为耦合电容的容值,其取值在75nF至265nF,远大于对端设备不在位时的两个电容参数(1nF=1000pF)。因而在位时充电时间常数较大。

在实际的电气信号中,充电时间常数的测量是通过发送器输出共模的脉冲信号,当对端接收器不在位时发送器可以检测到脉冲信号的幅度几乎没有衰减;而当对端接收器在位时,脉冲信号需要对链路的耦合电容充电,因而幅度会明显降低。接收器在位检测电路通过脉冲幅度来判断充电时间常数的大小,进而得出接收器是否在位的结论

Detect子状态机

Detect状态主要有两个子状态Detect.Quiet、Detect.Active。

1、Detect.Quiet

当设备冷启动、复位或从Polling、L2等其他状态进入Detect状态时,首先进入Detect.Quiet状态。

在此状态下,发送器处在电气闲(Electrical Idle)状态。电气闲状态是指发送器的D+和D-保持在同一恒定电平下,主要用于节点状态和非活动状态。发送器和对端的接收器之间通过电容串联耦合,因此在电气闲状态下接收器端差分信号两端都是0V电平。

Detect.Quiet在12ms超时后会进入下一子状态Detect.Active,或者检测到退出电气闲也会进入到Detect.Active状态。

2、Detect.Active

进入Detect.Active状态后立即进行接收器在位检测,如果所有的未配置Lane都检测到了接收器在位,则设备进入Polling状态;如果所有Lane都没有检测到接收器在位则进入Detect.Quiet状态。一个Lane指的是一组发送差分信号和一组接收差分信号。

其余情况为至少有一个Lane检测到了设备在位,但也有未配置的Lane未检测到接收器在位。此情况下回首先等待12ms,然后再次进行接收器在位检测。

如果检测结果与上次一致,且检测到在位的Lane可以组成1个或多个Link,则设备进入Polling状态。

否则设备进入Detect. Quiet

Detect可能遇到的问题

由于各种原因导致连接断开或连接不良会导致Detect出现异常,使链路卡在Detect状态。体现到链路上的现象可能是发送信号线上都是0V电平或者24ms间隔的脉冲信号。24ms是由Detect.Quiet子状态的12ms超时和Detect.Active状态中等待12ms组成。

1、物理连接问题

这种情况多数是电容失效导致的,失效后短路、断路或容值偏移都会导致检测不到对端在位;另外连接器装配、芯片焊接不良也有可能出现此现象。

2、设置问题

对端设备处在复位或断电状态下,或是PCIe控制器未配置或使能,则会检测不到接收器在位。

在FPGA使用PCIe IP核的情况下,大量配置需要编程人员调整。其中检测接收器在位的阈值寄存器在默认值不合理的情况下则会导致误判为接收器不在位。默认值是经过大量验证的,一般情况下不会出现这种情况。

当出现链路Detect相关问题时,首先应该排查对端设备电源、复位和时钟状态,其次排查链路是否有失效器件或连接器问题。当难以判断是可以尝试在耦合电容连接接收器的一侧接50Ω电阻到GND,若此时设备可以通过Detect到达Polling状态或之后的状态,则基本可以确定问题在对端设备或是耦合电容之后的链路中。

调试方法

在耦合电容后接电阻到GND后,可以保证在位检测电路可以正常检测到接收器在位,因此若设备正常则会进入到下一个状态。反之如果操作之后还是卡在Detect状态,则需要仔细排查本端设备的问题。

2.3.pcie均衡技术

说起pcie,就不得不提到其serdes均衡技术,原理性的资料网上非常多,在此就简单的介绍一下。

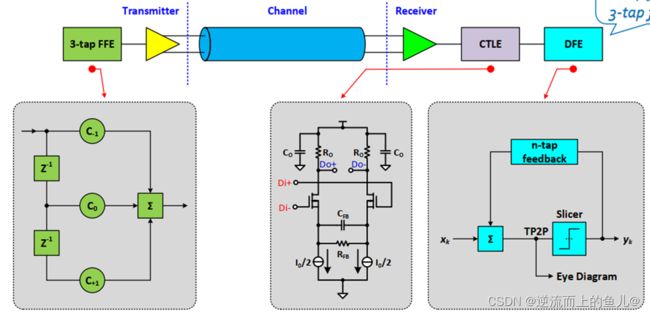

如下图,pcie的transmitter采用了fft加重技术,PCIE gen3采用1阶、Gen 4采用2阶、Gen 5采用3阶。Receiver采用了线性均衡ctle和前向反馈均衡dfe。

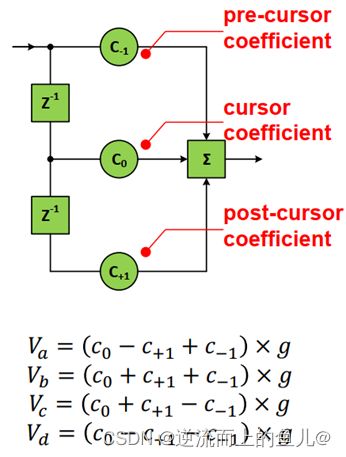

由于receiver一般采用自适应的配置,比较少关注,这里重点介绍发生端的dfe/ffe。Ffe的基本结构就是一个多抽头的fir滤波器,通过调节每个抽头的增益去改变。调节pre-cursor、main-cursor、post-cursor不同的值,信号的波形会发生相应的变化。

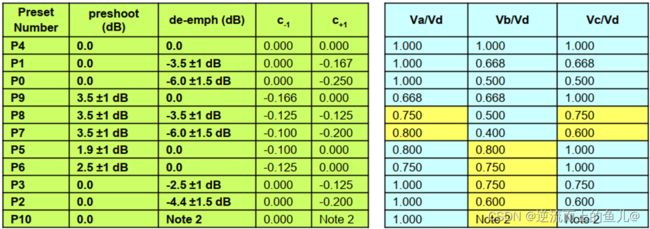

PCIE 3.0对应的预加重可调节范围,pcie-sig规定了10个挡位,如下图前8个挡位采用了ffe,后两个采用了dfe,这样可以根据channel和transmitter特性去灵活的调整。

另外,每个挡位还设置了微调范围,比如设置P1后,可以在-3.5+/-1dB范围内调整。

- pcie物理层测试

pcie的物理层测试规范主要定义了CEM的测试标准,对于我们产品使用的chip-chip模型并不完全适用。对应chip-chip,我们采取测试接收端波形和保证整个无源通道预算的方式去保证硬件链路的可靠性。

3.1物理层标准

PCIE sig组织是制定pcie的标准组织,主要由各大芯片、设备、测量仪器厂商联合成立。如下图,有负责电气、协议、插卡、线材、测试标准的5个工作组组成。

对于物理层来说,我们主要关注PCIE Base specification、PCIE CEM specification和PCIE compliance Testing这三份标准。

PCIE Base specification主要定义了芯片端的测试标准,以及芯片内的制造标准。PCIE CEM specification主要定义了Board-To-Board、Board-To-Card等插槽或者SMA连接器对插拓扑的连接器处,经过channel calibration后的指标。PCIE compliance Testing主要定义了CBB、CLB测试夹具、一致性测试标准、测试分析软件等。

根据上述的介绍可见,我们使用的Chip-To-Chip的拓扑,无法直接套用上述的任何一种标准。但是,我们根据上述拓扑可以分离出我们需要的指标。

对于无源参数,由于chip-to-chip就包含了上述的整个链路,标准可以选取Base Spec中的全链路(除Rx chip package)插损和回损作为测试标准。

对于有源参数,我们只关注接收侧的标准,可以选用Base Spec标准中Rx的电气参数作为标准判据。

Chip-to-chip的测试主要测试链路的无源S参数和接收端有源参数指标。Pcie-sig定义了无源链路的分段s参数插损、回损模板和时钟、数据的电参数指标。具体下面会一一介绍。

3.1.1.无源参数指标

在3.0的base specification上无源参数指标定义了回损和插损指标的mask。

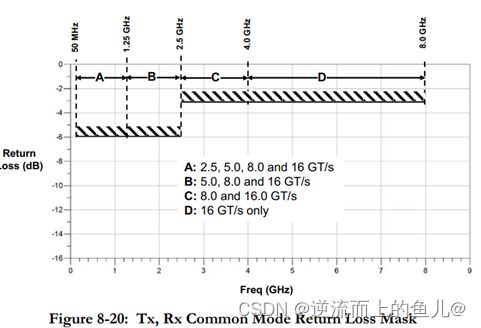

下图为规范要求的Return Loss的模板:

Insert Loss的模板要求:

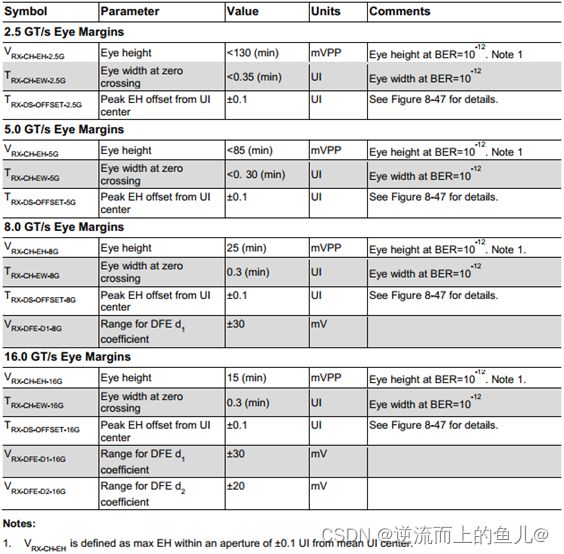

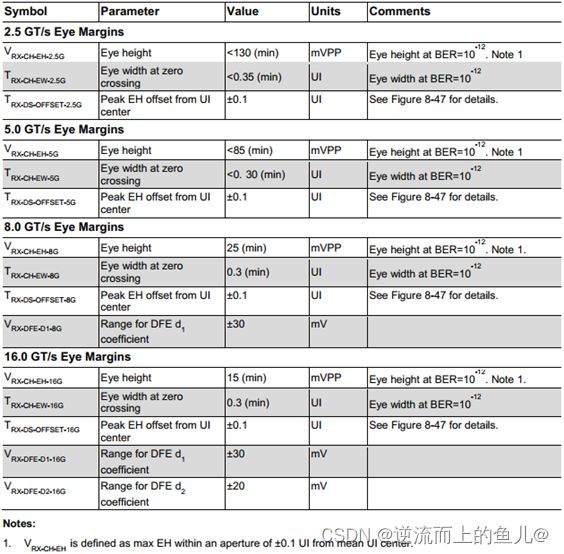

3.1.1.有源参数指标

有源信号这里主要描述了规范要求的参考时钟和data lane的信号质量要求。

Clk lane的信号质量和时序参数要求如下:

Data lane的mask要求:

3.2.无源+有源仿真

Pcie的信号仿真目的是为了验证3.1章中无源和有源参数的合规性。所以,也自然包含了无源s参数和有源仿真验证。

无源参数仿真

Pcie 3.0的工作速率为8Gbps,规范定义了1GHz~4GHz频率的模板。但是,为了后续的有源信号仿真能更好的体现出信号的真实情况,我们仿真频率扫描到信号的5倍频,即最高工作频率的5次谐波20GHz。

基于这个要求,普通的2D、2.5D仿真软件就失去了精度,就必须使用3D电磁场仿真软件去提取了。下面选择ansys公司HFSS仿真软件提取一个产品上的pcie实例。

如下图是使用HFSS提取的pcb trace上的s参数曲线:

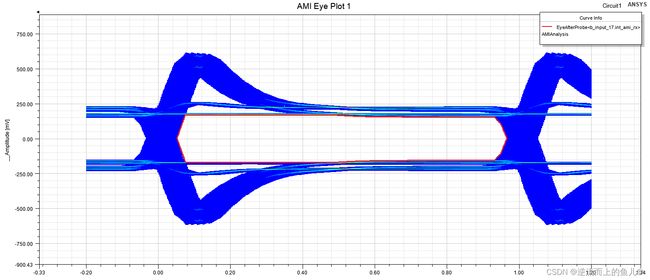

有源仿真

有源仿真需要使用使用厂家提供的芯片ibis或者ibis-ami模型去计算接收端的信号波形和眼图,来判断合规性。

如上图,tx端采用IC厂商给出的ibis-ami模型(包含行为模型ibis文件、算法ami文件和一个dll动态链接库)和芯片的封装package寄生参数文件,通道使用前面提取寄生参数文件,RX同样使用芯片的package文件和rx-ami模型。

| After source |

|

| After channel |

|

| After probe |

|

| 近场 辐射 |

3.4.有源信号测试

100MHz时钟测试

| 通过标准 满足标准要求 |

|||

| Spec |

|||

| 测试步骤 |

|||

| 指标 |

描述 |

规格 |

测量结果 |

| Rising Edge Rate |

上述沿斜率 |

0.6V/ns~4V/ns |

|

| Falling Edge Rate |

下降沿斜率 |

0.6V/ns~4V/ns |

|

| VIH |

差分输入高电平 |

>150mV |

|

| VIL |

差分输入低电平 |

<-150mV |

|

| Vcross |

单端交叉点 |

250mV~550mV |

|

| Vcross-delta |

单端交叉点偏移 |

<140mV |

|

| Tccj |

周期性抖动 |

<150ps |

|

| Vmax |

差分最小值 |

<1,15V |

|

| Vmin |

差分最大值 |

>-0.3V |

|

| Duty cycle |

占空比 |

40%~60% |

|

PCIE data lane信号测试

| 通过标准 满足标准要求 |

| Spec |

| 测试步骤 |