全减器---Verilog实现(结构描述,数据流描述,行为描述,层次结构描述)

Verilog实现全减器

前言

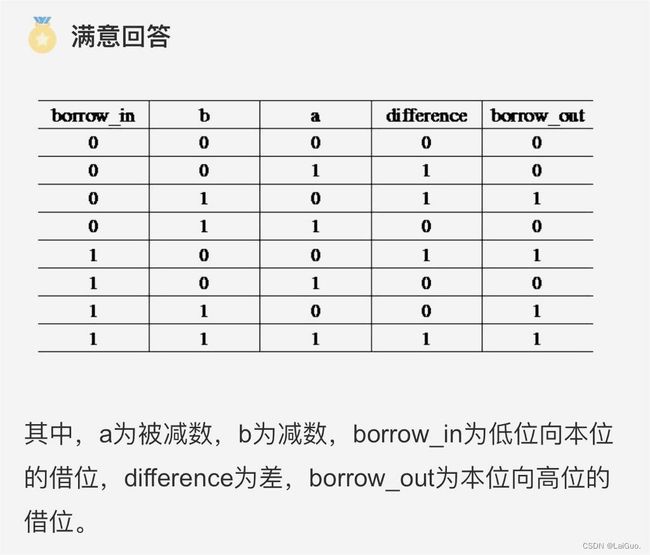

全减器真值表—>引用知乎:链接: 全减器真值表怎么理解

一、任务要求

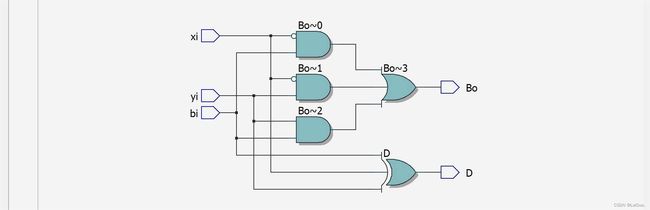

二、门极结构描述

代码部分

//门级结构化描述

module full_subtraction(xi,yi,bi,D,Bo);

input xi,yi,bi;//xi被减数,yi减数,bi被减数向高位的借位

output D,Bo; //D差值,Bo低位向被减数的借位

wire r1,r2,r3,r4,r5;//连接线

xor (r1,xi,yi),(D,r1,bi) ;//异或门

and (r5,r2,yi),(r4,bi,r3) ;//与门

or (Bo,r4,r5) ;//或门

not (r2,xi),(r3,r1);//非门

endmodule

原理图

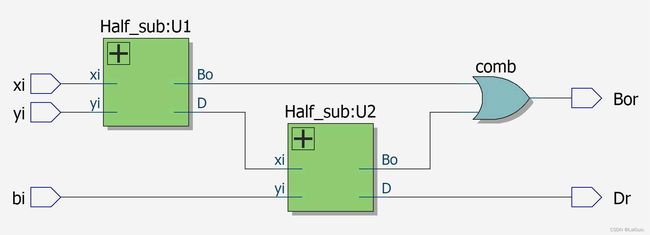

三、数据流描述

代码部分

//数据流描述

module full_subtraction(xi,yi,bi,D,Bo);

input xi,yi,bi;//xi被减数,yi减数,bi被减数向高位的借位

output D,Bo; //D差值,Bo低位向被减数的借位

assign D=xi^yi^bi;//差值表达式

assign Bo=~xi&bi|~xi&yi|yi&bi;//进位表达式

endmodule

原理图

四、行为描述

代码部分

//行为描述

module full_subtraction(xi,yi,bi,D,Bo);

input xi,yi,bi;//xi被减数,yi减数,bi被减数向高位的借

output reg D,Bo; //D差值,Bo低位向被减数的借位

always @*

begin

{Bo,D}=xi-bi-yi;

end

endmodule

原理图

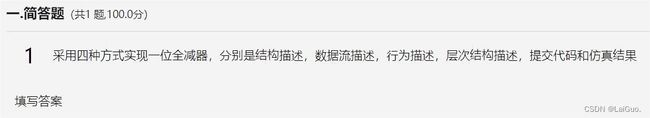

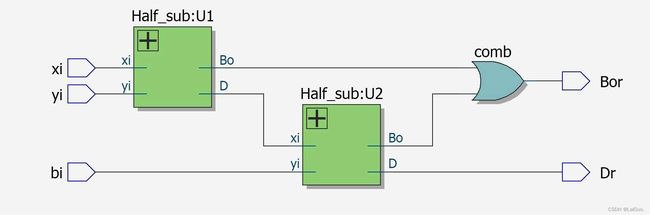

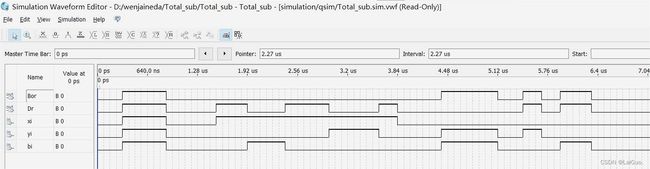

五、结构描述

代码部分

//半减器

module Half_sub(xi,yi,D,Bo);

input wire xi,yi;//输入被减数xi,减数yi,

output wire D,Bo;//输出差值D,被减数向高位借位Bo

assign D=xi^yi;//

assign Bo=~(xi)&yi;

endmodule

//调用半减 构成全减

//全减器,顶层文件

module Total_sub(xi,yi,bi,Dr,Bor);

input wire xi,yi,bi;//输入被减数xi,减数yi,低位向被减数的借位

output wire Bor,Dr;//输出差值Bor,被减数向高位借位Bo

wire D_1,Bor_1,Bor_2;//定义连接导线

Half_sub U1(.xi(xi),.yi(yi),.D(D_1),.Bo(Bor_1));//被调用的模块名,自定义名; .被调用接口(顶层接口)

Half_sub U2(.xi(D_1),.yi(bi),.D(Dr),.Bo(Bor_2));

or(Bor,Bor_1,Bor_2);

endmodule