数电知识点小结

文章目录

- 一、逻辑代数基础

- 二、逻辑门电路

- 三、组合逻辑电路

- 四、触发器

- 五、脉冲波形的产生与整形

- 六、时序逻辑电路

- 七、数字系统概述

- 八、半导体存储器

- 九、可编程逻辑器件

- 十、数模和模数转换

一、逻辑代数基础

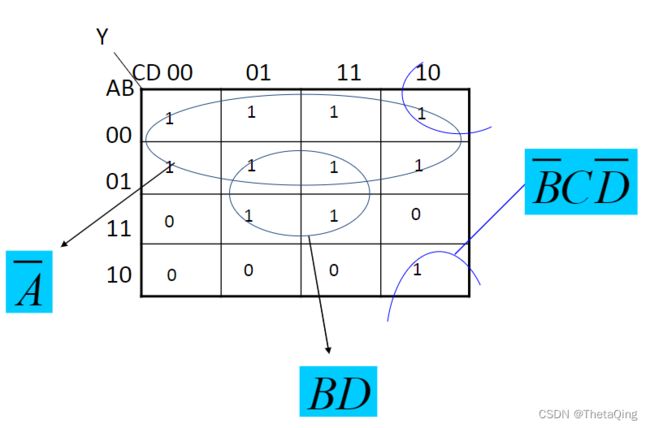

- 卡诺图基本原则

(1)若两个最小项相邻,可合并为一项消去一对不同因子;

(2)若四个最小项相邻,可合并为一项消去两对不同因子;

(3)若八个最小项相邻,可合并为一项消去三对不同因子;

注意:最小项是乘积项,最大项是和的形式;卡诺图中如果只有三个项,则高一位,低两位;排列顺序是00 01 11 10,最小项的序号从左到右依次是m0 m1 m3 m2

- 逻辑函数的表示方法有哪几种?它们之间如何转换?

逻辑函数的表达方式有四种,分别是逻辑函数式、逻辑真值表、逻辑图、卡诺图。

- 逻辑函数式转换为真值表,首先需要将输入逻辑变量的组成情况按顺序写出,再一一判断输出逻辑变量。

- 真值表转换为函数式,首先要把输出逻辑变量为1的情况标出,再看对应的输入逻辑变量——1对应原变量,0对应反变量,每一组组内变量相乘,组外相加。

- 其它方式转换为逻辑图,最好统一转换为函数式,再根据函数式的情况分类画图,最后统一起来。 其它方式转换为卡诺图

二、逻辑门电路

- 试说明在vi1接高电平(3.4V)的情况下,用万用电表测量图2.1的vi2端得到的电压为多少?图中的与非门为74系列的TTL电路,万用电表使用5V量程,内阻为20kΩ/V。(1.4V)

- 由TTL反相器的电压传输特性可知,其阈值电压VTH是( 1.4 )V左右。

- OC门(集电极开路门):当输入有低电平时,可认为此时门的输出端为高阻状态。

- TS门(三态门):除了高低电平之外,还有第三个状态。

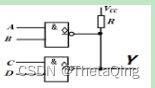

- OC门主要用于线与:

下图所示电路Y输出为:

- CMOS门电路在外部特性上与TTL门电路有哪些区别?

电源范围更宽,更低功耗,抗干扰能力更强,连接方便

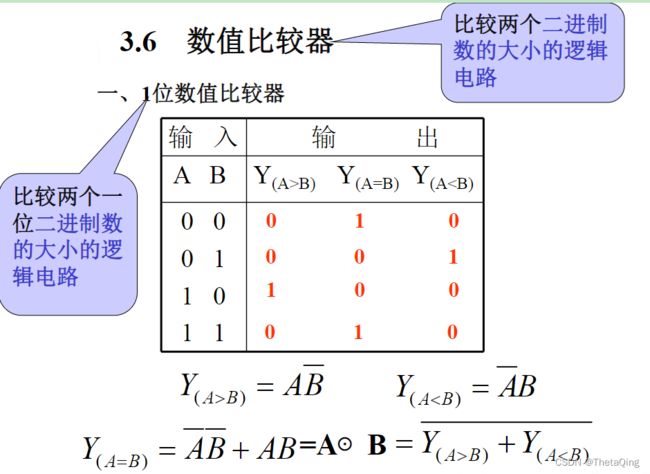

三、组合逻辑电路

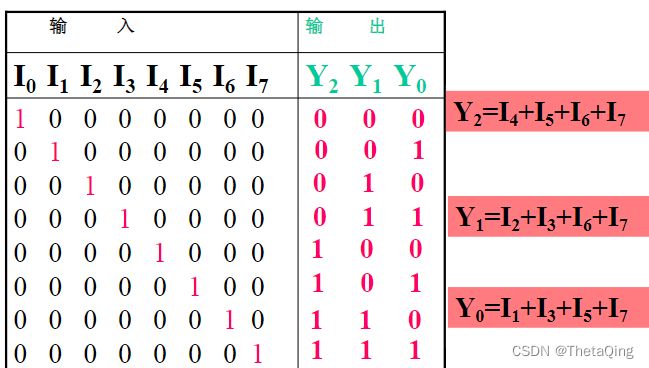

(2)优先编码器:在优先编码器中,对每一位输入都设置了优先权,因此允许两位以上的输入信号同时有效,但优先编码器只对优先级较高的输入进行编码,从而保证编码器工作的可靠性。

图为高电平有效的8线-3线优先编码器功能表,I7优先级最高,I0优先级最低

(3)74LS148

低电平有效的。

~S为选通输入端,当~S=1时,所有的输出端均被封锁在高电平;只有在~S=0时,编码器才能正常工作。~Ys为选通输出端,当~S=0,~Ys=0时,表示电路工作,但无编码输入。~Yex为拓展段,当且~S=0,~Yex=0时,表示电路工作,而且有编码输入。- 表中

~I7的优先权最高,~I0的优先级最低,注意编码也是取的反码

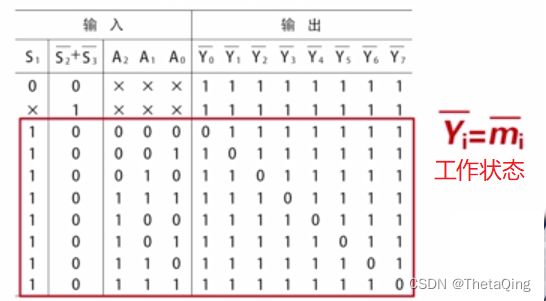

- 译码器:将二进制代码译成对应输出的高、低电平信号的电路,称为译码器。

S1, ~S2, ~S3为片选输入端,控制多片连接,拓展功能。- 当

S1=1, ~S2+~S3=0时,译码器工作,否则译码器被禁止,所有的输出端被封锁在高电平。- 输出取

反码

3线-8线译码器辅以门电路后,更适用于实现3输入多输出的组合逻辑函数,因为它的每个输出都对应输入3位代码的最小项的非。

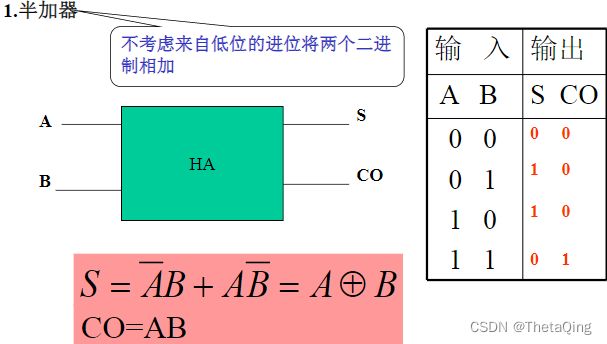

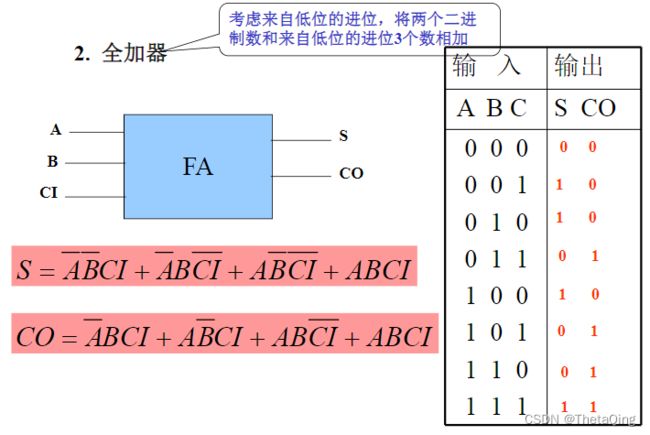

- 加法器

四、触发器

- 触发器是指能够记忆一位二值信号的基本逻辑单元电路,具有的特点:

(1)两个能自动保持稳定的状态,“1”态和“0”态;

(2)根据不同的输入信号,可以置成“1”态和“0”态;

(3)输入信号消失后,获得的新状态能自行保持下来。

- 触发器的分类

(1)从电路结构不同:直接型、同步型、主从型、边沿型。

(2)从逻辑功能不同:RS 触发器、JK触发器、T触发器、T’ (翻转型)触发器。

(3)从存储数据的原理不同:静态、动态。

- 基本触发器

~SD为置位段,低电平有效;~RD为复位端,低电平有效;~SD和~RD不能同时作用,约束条件~SD+~RD=1;

- 同步触发器

S为置位段,高电平有效;R为复位端,高电平有效;S和R不能同时作用,约束条件:SR=0;CP=0,触发器的状态保持不变;CP=1,输入信号能随时多次改变触发器的状态。

- 主从触发器:一个主触发器,一个从触发器。

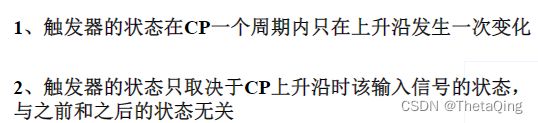

- 边沿触发器

五、脉冲波形的产生与整形

- 获取矩形脉冲波形的途径

- 利 用 各 种 形 式 的 多 谐 振 荡 器 电 路 直 接 产 生 所 需 要 的矩 形 脉 冲 ;

- 通 过 各 种 整 形 电 路 把 已 有 的 周 期 性 变 化 波 形 变 换 为 符 合 要 求 的 矩 形 脉 冲

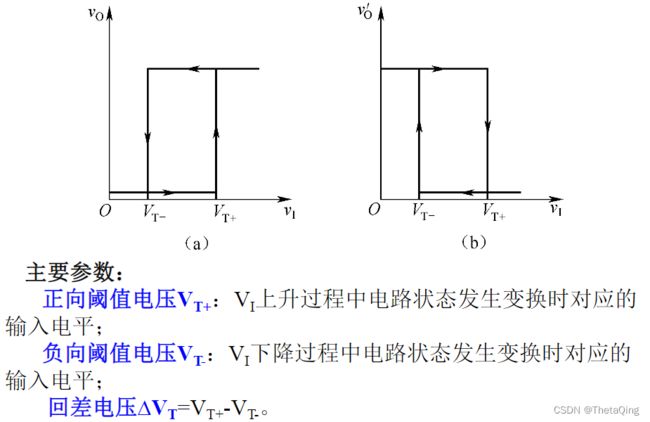

- 施密特触发器

性 能 特 点

1 ) 输 出 从 低 电 平 跳 到 高 电 平 时 对 应 的 输 入 电 平 , 与 输 出 从 高 电 平 跳 到 低 电 平 时 对 应 的 输 入 电 平 不 同 , 电 路 有 两 个 不 同 的 阈 值 电 压 。

2 ) 在 电 路 状 态 转 换 时 , 通 过 电 路 内 部 的 正 反 馈 过 程使 输 出 电 压 波 形 的 边 沿 变 得 很 陡 。利 用 这 两 个 特 点 不 仅 能 将 边 沿 变 化 缓 慢 的 信 号 波 形 整 形 为 边 沿 陡 峭 的 矩 形 波 , 而 且 可 以将 叠 加 在矩形 脉冲 高 、 低 电 平 上 的 噪 声 有 效 地 清 除 。

- 单稳态触发器

(1) 工 作 特 点

1 ) 它 有 稳 态 和* 暂 稳 态* 两 个 不 同 的 工 作 状 态 :

2 ) 在 外 界 触 发 脉 冲 作 用 下 , 能 从 稳 态 翻 转 到 暂 稳 态 , 在 暂 稳 态 维 持 一 段 时 间 以 后 , 再 自 动 返 回 稳 态 :

3 ) 暂 稳 态 维 持 时 间 的 长 短 取 决 于 电 路 本 身 的 参 数 , 与 触 发 脉冲 的 宽 度 和 幅 度 无 关 。

由 于 具 备 这 些 特 点,单 稳 态 触 发 器 被 广 泛 应 用 于 脉 冲 整 形 、 延 时 ( 产 生 滞 后 于 触 发 脉 冲 的 输 出 脉 冲 》 以 及 定 时 《 产 生 固 定 时 间 宽 度 的 脉 冲 信 号 ) 等 。

主要参数:暂稳态脉冲宽度tw(脉冲宽度tw是指从脉冲前沿到达__0.5___Vm起,到脉冲后沿到达__0.5___Vm为止的一段时间。)

- 多谐振荡器

( 1 ) 特 点

多 谐 振 荡 器 是 一 种 自 激 振 荡 器 , 也 称 为== 无 稳 态 触 发 器== 。* 在 接 通 电 源 以 后 , 不 需 外 加 触 发 信 号 , 便 能自 动 输 出 一 定 频 率 的 矩 形 脉 冲* 。 由 于 矩 形 波 中 含 有 丰 富 的 高 次 谐 波 分 量 , 所 以 习 惯 上 又 把 矩 形 波 振 荡 器 叫 做 多 谐 振 荡 器 。

( 2 ) 主 要 参 数

振 荡 周 期 T 或 振 荡 频 率 f

- 三种电路特点比较

(1)三 种 电 路 中 , 只 有 多 谐 振 荡 器 属 于 脉 冲 波 形 的 *产 生 电 路 *, 而 施 密 特 触 发 器 和 单 稳 态 触 发 器 都 属 于 脉 冲 波 形 的 整 形 电 路 ;

《 2 》 三 种 电 路 中 , *多 谐 振 荡 器 没 有 稳 态 , 施 密 特 触 发 器 有 两 个 稳 态 , 单 稳 态 触 发 器 只 有 一 个 稳 态 *。

- 555定时器

(1) 由555定时器不可以组成____D______。

A.单稳态触发器

B.多谐振荡器

C.施密特触发器

D.JK触发器

(2)施密持触发器常用于对脉冲波形的______C_____。

A.定时

B.计数

C.整形

D.产生

六、时序逻辑电路

- 时序逻辑电路是指电路任意时刻的输出信号不仅取决于该时刻的输入信号,还与电路的原来状态有关,主要由(组合逻辑电路)和(存储电路)组成。

- 时序逻辑电路的分类:

(1)根据存储电路中触发器的动作特点分为:

- 同步时序逻辑电路:所有触发器的状态在同一时刻发生变化;

- 异步时序逻辑电路:触发器的状态不是在同一时刻发生变化。

(2)根据输出变量的特点分为:- 米利型:Y=F(X,Q);

- 穆尔型:Y=F(Q).

- 描述时序逻辑电路逻辑关系的三大方程分别是 驱动方程、输出方程和状态方程。

- 同步时序逻辑电路的分析方法:

A. 分 析 方 法 的 任 务 :

给 定 时 序 逻 辑 电 路 , 找 出 其 变 化 规 律

B. 步 骤 :

1). 写 出 驱 动 方 程

2). 写 出 输 出 方 程

3). 求 状 态 方 程

4). 计 算 状 态 转 换 表

5). 画 状 态 转 换 图

6). 画 时 序 图

7). 说 明 其 逻 辑 功 能

- 时序逻辑电路的设计

(1)时 序 逻 辑 电 路 的 设 计 的 任 务

要 求 设 计 者 根 据 给 出 的 具 体 逻 辑 问 题 , 求 出 实 现 这 一 逻 辑 功 能 的 逻 辑 电 路 。

(2) 时 序 逻 辑 电 路 的 设 计 的 原 则 :所 得 到 的 设 计 电 路 结 果 应 力 求 简 单 。

a. SSI 设 计 : 电 路 最 简 的 标 准 是 所 用 的 触 发 器 和 门 电 路 的 数 目 最 少 , 而 且 触 发 器 和 门 电 路 的 输 入 端 数 目 也 最 少 。

b. MSI 设 计 电 路 最 简 的 标 准 则 是 使 用 的 集 成 电 路 数 目 最 少 , 种 类 最 少 。 而 且 互 相 间 的 连 线 也 最 少 。

(3)同步时序逻辑电路的设计步骤

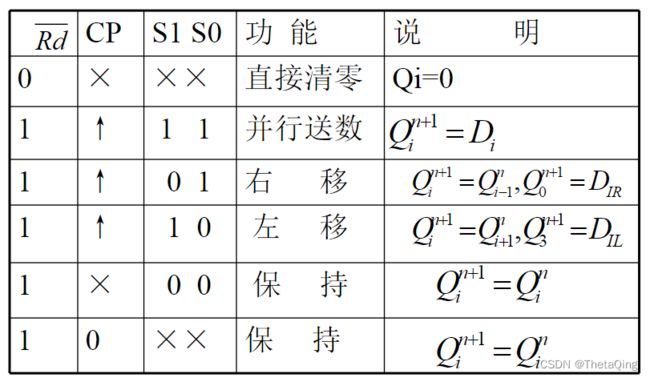

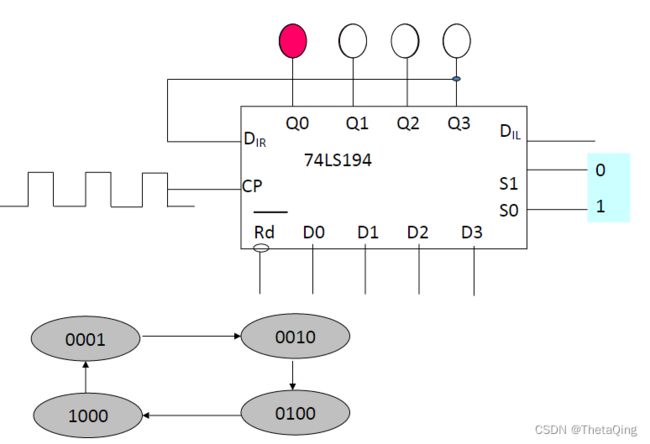

- 寄存器:寄存器是由触发器组成的用来暂存一组二进制数码的逻辑部件,它是构成计算机CPU中最基本的逻辑部件,主要功能:清除数码、接收数码、暂存数码、输出数码、移位功能。

- 寄存器的工作模式:

(1)两拍接收工作模式:发清零脉冲、准备数据、发接收脉冲。

(2)单拍接收工作模式:准备数据、发接收脉冲。

(3)多位数码接收工作模式:并出并入。

(4)串行移位接收工作模式:串入并出。

(5)环形移位工作模式;

(6)扭环形移位工作模式。

- 寄存器类型:

- 寄存器的应用:

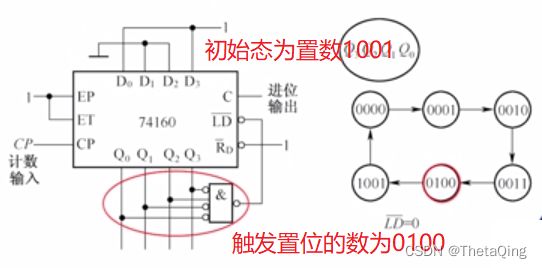

- 计数器分类:

a. 按 工 作 方 式 分 : 异 步 计 数 器 , 同 步 计 数 器

b. 按 编 码 方 式 分 : 二 进 制 计 数 器 , 二 一 十 进 制 计 数 器 , 任 意 进 制 计 数 器

c. 按 工 作 特 点 分 : 加 法 计 数 器 , 减 法 计 数 器 , 可 逆 计 数 器

七、数字系统概述

- 数字系统分为功能拓展和系统综合两大类。其中:

(1)功能拓展:由多片同一类型芯片组成的数字系统称为功能拓展,主要分为:

a. 中规模集成组合逻辑电路的功能拓展

例 : 由 2 片 3-8 译 码 器 74LS138 扩 展 成 4-16 线 译 码 器 。

b. 中 规 模 集 成 *时 序 逻 辑 电 路 *的 功 能 扩 展

例 : 用 2 片 74161 构 成 256 以 内 的 任 意 进 制 计 数 器 。

c. 存 储 器 容 量 的 扩 展

例 : 将 多 片 存 储 器 组 合 起 来 , 形 成 一 个 大 容 量 的 存 储 器 。(2)系统综合:由多片不同类型芯片组成的数字系统称为系统综合,主要分为:

a. 组 合 复 合 型 : 由 多 片 *不 同 组 合 逻 辑 芯 片 *构 成 的 数 字 系 统 称 为 组 合 复 合 型 。

例 : 由 2 片 74LS283 和 1 片 74LS85 组 成 BCD 码 加 法 器

b. 时 序 复 合 型 :由 多 片 *不 同 时 序 逻 辑 芯 片 *构 成 的 数 字 系 统 称 为 时 序 复 合 型 。

例 :由74LS194和 74LS160 组 成 跳 频 信 号 发 生 器 。

c. 组 合 时 序 型: 由 组 合 逻 辑 芯 片 控 制 时 序 逻 辑 芯 片 所 构 成 的 数 字 系 统 称 为 组 合

例 : 用 8 线 一 3 线 优 先 编 码 器 74LS148 和 同 步 四 位 二 进 制 计 数 器 74LS161 组 成 的 可 控 分 频 器

d. 时 序 组 合 型 : 由 时 序 逻 辑 芯 片 控 制 组 合 逻 辑 芯 片 所 构 成 的 数 字 系 统 称 为 时 序 组 合 型 。

例 :74LS161 和 74LS138 组 成 顺 序 脉 冲 发 生 器;74Ls161 和 74LS151 组 成 的 序 列 信 号 发 生 器 。

- 数字系统的一般分析方法:模块化分析方法步骤

步骤:

(1)模块功能: 列 出 各 功 能 模 块 的 逻 辑 功 能 。

( 不 必 从 模 块 内 部 电 路 分 析 , 把 各 模 块 看 成 黑 箱 处 理 )

( 2 )模块关系: 根 据 给 出 的 电 路 图 理 清 各 模 块 之 间 的 连 接 关 系 或 控

制 关 系 。

( 3 )工作状态: 根 据 给 定 条 件 分 析 各 模 块 的 工 作 状 态 以 及 整 个 系 统

的 工 作 状 态 。

( 4 ) 状态分析:列 出 整 个 系 统 的 功 能 表 或 状 态 转 换 图 或 者 画 出 其 时

序 图 。

( 5 ) 总结:说 明 整 个 系 统 的 逻 辑 功 能 。

- 数字系统的模块化设计方法步骤

( 1 ) 逻 辑 抽 象 : 确 定 输 入 、 输 出 逻 辑 变 量 和 电 路 状 态 数

( 2 ) 确 定 系 统 的 时 钟 信 号 。

( 3 ) 根 据 系 统 的 设 计 要 求 , 划 分 系 统 的 模 块 。

( 4 ) 根 据 各 功 能 模 块 的 要 求 选 用 SSI 、 MS 1 、 LSI 实 现 。

( 5 ) 画 出 数 字 系 统 电 路 图 。

八、半导体存储器

- 半导体存储器的分类:只读存储器(ROM)和随机存取存储器(RAM)。

- ROM(Read Only Memory)是存储固定信息的存储器件,即先把信息和数据写入到存储器中,在正常工作时它存储的数据是固定不变的,只能读出,不能迅速写入。

特点:掉电之后存储的数据不会丢失。

电路结构:包含存储矩阵、地址译码器和输出缓冲器三个组成部分。

用途:

( 1 ) 存 储 各 种 程 序 代 码 ;

( 2 ) 实 现 多 输 入 、 多 输 出 逻 辑 函 数 真 值 表 ;

( 3 ) 代 码 的 变 换 、 符 号 和 数 字 显 示 等 有 关 数 字 电 路 及 存 储 各 种 函 数 等 。

- PROM(可编程只读存储器):出厂时,制作的是一个完整的二极管或三极管存储单元矩阵,相当于所有的存储单元全部存入1。在每个单元的三极管发射极上接有快速熔丝。

- 一片8K×8位的ROM存储器需要( 13 )根地址线。

8k*8表示:内存共有8K个单元(每单元8位二进制数)

则内存容量为8KB=8x1024B =8192B =2^13 B

地址线至少需13根

- EPROM(可擦除可编程存储器):

(1)UVEPROM:采用浮栅型MOS器件,紫外线照射擦除。

(2)E^2PROM:采用浮栅工艺,但可利用一定宽度电脉冲擦除。

(3)快闪存储器:既 吸 收 了 EPROM 结 构 简 单 、 编 程 可 靠 的 优 点 , 又 保 留 了 E2PROM 用 隧 道 效 应 擦 除 的 快 捷 特 性 , 而 且 集 成 度 可 以 做 得 很 高 。

- RAM(Random Access Memory)是随机存取存储器,读写方便。

特点:所存储信息会因断电而丢失。

用途:常 用 来 放 一 些 采 样 值 、 运 算 的 中 间 结 果 , 数 据 暂 存 、 缓 冲 和 标 志 位 等 。

- SRAM(静态随机存取存储器):通常由存储矩阵、地址译码器和读/写控制电路三部分组成,其静态存储单元由六管NMOS静态存储单元组成。

- DRAM(动态随机存取存储器),由三管MOS构成动态存储单元。

- 存储器的主要技术指标:

(1)存储容量:该存储器基本存储单元的总数,存储器中的存储容量写成(字数×位数)的形式。

(2)存储时间:一般用读(或写)周期描述,周期越短,工作速度越快。

- 存储器的应用:

(1)作函数运算表电路;

(2)实现组合逻辑函数;

- 本章所讲的半导体存储器和前面所学的寄存器、锁存器等有什么区别和联系?

存储器用于存储数据,寄存器主要用于存放硬件地址,而锁存器一般用于做控制

寄存器存在于CPU中,速度很快,数目有限;

存储器就是内存,速度稍慢,但数量很大;

计算机做运算时,必须将数据读入寄存器才能运算。

九、可编程逻辑器件

- 数 字 系 统 的 实 现 方 法

(1) 通 用 型 SS | 、 MSI 、 LS | · 一 模 块 化 设 计 方 法 。 使 用 方 便 灵 活 。 但 是 系 统 体 积、 功 能 、 重 量 较 大 ,可 靠 性 和 可 维 护 性 较 差 。

(2)专 用 集 成 电 路 (ASIC) 一 · 能 把 所 设 计 的 数 字 系 统 做 成 一 片 大 规 模 集 成 电 路 , 体 积 小 、 重 量 轻 、 功 耗 低 , 可 靠 性 高 。 但 是 成 本 很 高 , 而 且 设 计 、 制 造 的 周 期 较 长 。

(3) 可 编 程 逻 辑 器 件 ( PLD) 一 · 作 为 一 种 通 用 器 件 生 产 的 , 但 它 的 逻 辑 功 能 是 由 用 户 通 过 对 器 件 编 程 来 设 定 。

- PLD一般由输入电路、与阵列、或阵列和输出电路组成。

- FPLA(现场可编程逻辑阵列),一般由可编程的与逻辑阵列和可编程的或逻辑阵列以及输出缓冲器组成。任何一个复杂的逻辑函数式都可以变换成与-或表达式,所以可利用FPLA实现逻辑函数。

- FPLA与(P)ROM的基本结构比较:

(1)PROM的基本结构:由于 PROM 的“ 与 ” 阵 列 为 --全 译 码 制-- , 当 输 入 有 n 个 变 量 时 , 有 2^n 个 与 项 , 阵 列 较 大 、 开 关 时 间 较 长

(2)FPLA 与 ( P ) ROM 的 比 较

1 ) *电 路 结 构 极 为 相 似 , 都 是 由 一 个 与 逻 辑 阵 列 、 或 逻 辑 阵 列 和 输 出 缓 冲 器 组 成 。

2 ) ( P ) ROM 的 与 逻 辑 阵 列 是 固 定 的 , 而 FPLA 的 与 逻 辑 阵 列 是 可 编 程 *的 。

3 ) §ROM 的 与 逻 辑 阵 列 将 输 入 变 量 的 全 部 最 小 项 都 译 出 了 , 而 FPLA 的 与 逻 辑 阵 列 只 产 生 所 需 要 的 少 得 多 的 乘 积 项 。

- PAL(可编程阵列逻辑),PAL器件一般由可编程的与逻辑阵列、固定的或逻辑阵列和输出电路三部分组成。

- PAL的输出结构类型:

(1)专用输出结构:

a. 其 输 出 端 是 一 个 与 或 门 、 与 或 非 门 或 者 是 互 补 输 出 结 构 :

b. 其 共 同 特 点 是 所 有 设 置 的 输 出 端 只 能 用 作 输 出 使 用 ;

c. 该 结 构 的 PAL 器 件 只 能 用 来 产 生 组 合 逻 辑 函 数 。

(2)可编程输入/输出结构:

输 出 端 是 一 个 具 有 可 编 程 控 制 端 的 三 态 缓 冲 器 , 控 制 端 由 与 逻 辑 阵 列 的 一 个 乘 积 项 给 出 。 同 时 。 输 出 端 又 经 过 一 个 互 补 输 出 的 缓 冲 器 反 馈 回 与 逻 辑 阵 列 。

(3)寄存器输出结构:

a. 该 结 构 在 输 出 三 态 缓 冲 器 和 与 - 或 逻 辑 阵 列 的 输 出 之 间 串 进 了 由 D 触 发 器 组 成 的 寄 存 器 。 同 时 , 触 发 器 的 状 态 又 经 过 互 补 输 出 的 缓 冲 器 反 馈 回 与 逻 辑 阵 列 的 输 入 端 。

b. 该 结 构 不 仅 可 以 存 储 与 或 逻 辑 阵 列 的 输 出 的 状 态 , 而 且 能很方便的组成各种时序逻辑电路。

- PAL 器 件 使 用 时 的 优 缺 点

优点: (1) PAL 选 定 芯 片 型 号 后 , 其 输 出 结 构 就 选 定

(2) PAL 有 20 多 种 不 同 的 型 号 可 供 用 户 使 用

(3) PAL 器 件 的 出 现 为 数 字 电 路 的 研 制 工 作 和 小 批 量 产 品 的 生 产 提 供 了 很 大 的 方 便

缺点:(4) PAL 采 用 的 是 双 极 型 熔 丝 工 艺 , 只 能 一 次 性 编 程

(5) PAL 输 出 方 式 是 固 定 的 , 不 能 重 新 组 态 , 因 而 编 程 灵 活 性 较 差 。

- GAL(通用阵列逻辑),特点:

(1) GAL 采 用 电 可 擦 除 的 CMOS (E2CMOS) 工 艺 制 造 , 可 反 复 多 次 编 程

(2)G A L 采 用 可 编 程 的 输 出 逻 辑 宏 单 元 0 L M C ( Output Logic Macro Cell) , 输 出 组 态 灵 活 , 具 有 很 强 的 通 用 性

(3) GAL 具 有 加 密 功 能

- OLMC的工作模式:

专 用 输 入 模 式

专 用 组 合 输 出 模 式

带 反 馈 的 组 合 输 出 模 式

时 序 逻 辑 的 组 合 输 出 模 式

寄 存 器 输 出 模 式

十、数模和模数转换

- AD、DA的含义:

(1) A/D 转 换

把 模 拟 信 号 转 换 为 数 字 信 号 的 过 程 称 为 模 一 数 转 换 , 简 称 为 A/D 转 换

把 实 现 A/D 转 换 的 电 路 称 为 A/D 转 换 器 , 简 称 为 ADC

(2)D/A 转 换

把 数 字 信 号 转 换 为 模 拟 信 号 的 过 程 称 为 数 一 模 转 换 , 简 称 为 D / A 转 换

把 实 现 D / A 转 换 的 电 路 称 为 D / A 转 换 器 , 简 称 为 DAC

- ADC和DAC的性能指标:

(1)转换速度

(2)转换精度

- AD转换的基本步骤:取样、保持、量化、编码。

- 取样:香农取样定理:

为 了 保 证 采 样 信 号Vs 、 能 正 确 地 表 示 模 拟 输 入 信 号 Vi, 必 须 满 足 :fs≥fimax

其中,fs表示采 样 频 率 ,即 每 秒 钟 采 样 的 次 数 ;fimax表示输入信 号 的 最 高 频率分量的频率。

- 量 化 : 把 采 样 电 压 表 示 为 最 小 量 化 单 位 ( △ ) 的 整 数 倍 的 过 程 即 : [Vs/ △], 余 数 即 为 量 化 误 差

- 编码:把 量 化 的 结 果 ( △ 的 整 数 倍 ) 用 二 进 制 代 码 表 示 , 这 些 代 码 就 是 A / D 转 换 的 结 果 。

- 下列A/D转换器中,转换速度最快的是___A______

A.并联比较型

B.计数器型

C.逐次逼近型

D.双积分型

- 下列4种A/D转换器类型中,抗干扰能力最强的是 (D) 。

A.并联比较型ADC

B.计数型ADC

C.逐次渐近型ADC

D.双积分型ADC