cadence 17.2 入门学习2 allegro

下面是我整理的笔记,基本上原创很少,我写的极可能是胡说八道,凑合着看

自己去找个案例做,我这个图片不一定是我的

目录

-

- 打开PCB Editor界面

-

- Product Choices

- 下面的小工具

- Allegro的symbol类型:

- 创建自定义焊盘及封装

-

- 找不到 layout > PIN

- 创建焊盘图形文件的类型选择

- 焊盘保存失败的原因

- 找不到自己做的焊盘怎么办

- 生成板框

- 区域的类型:

- 绘制Route Keepin

- 导人网表

打开PCB Editor界面

Product Choices

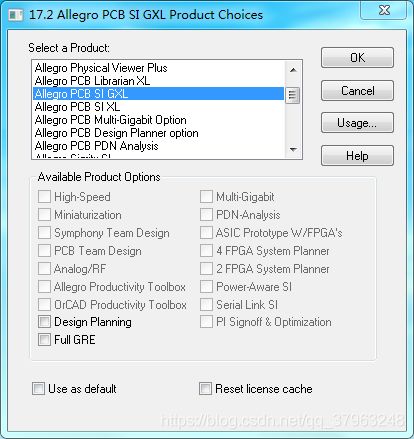

Allegro PCB SI GXL:功能最全,默认有 Design Planning、Full GRE 功能,可以选择Team Design、Analog/RF 等功能,一般选择这个。

Allegro PCB SI: 可以选择 Team Design、Analog/RF、Design Planning、Full GRE等功能„

Allegro PCB Design XL:不具备 Team Design、Analog/RF、Design Planning、Full

GRE 功能,不备高速约束规则设置功能。

Allegro可供产品包含L、XL和GXL三个级别。

Allegro L产品系列为PCB设计提供瞄向解决主流设计问题的产品。

Allegro XL产品系列通过集成的约束驱动自动控制和基于分布式的团队设计生产能力,提供应对更复杂和高端的设计挑战的高级PCB设计产品。

Allegro GXL产品系列提供差异化的PCB设计产品,可应对诸如高级封装协同设计及数千兆赫兹级信号完整性(SI)分析的前沿设计挑战。

下面的小工具

Team Design:协同设计,可将整个PCB分为多个部分分给多个设计人员同时设计,各部分完成后再合并为完整的PCB,这样大大地提高了 工作效率。

Analog/RF: RF设计工具。

Allegro的symbol类型:

Board symbol:板

Board(wizard):板向导

Module:模块符号

Package symbol:一般封装符号

一般元件的封装符号,后缀名为*.psm。

PCB中所有元件像电阻、电容、电感、IC等的封装类型即为Package Symbol。

Package symbol(wizard):一般封装符号向导

Mechanical symbol:机械符号

由板外框及螺丝孔所组成的机械构图符号,后缀名为*.bsm。

有时我们设计PCB的外框及螺丝孔位置都是一样的,比如显卡,电脑主板, 每次设计PCB时要画一次板外框及确定螺丝孔位置,显得较麻烦。

这时我们可以将PCB的外框及螺丝孔建成一个Mechanical Symbol,在设计PCB时,将此Mechanical Symbol调出即可。

Shape symbol:形状符号

供建立特殊形状的焊盘用,后缀为*.ssm。

像显卡上金手指封装的焊盘即为一个不规则形状的焊盘,在建立此焊盘时要先将不规则形状焊盘的形状建成一个Shape Symbol,然后在建立焊盘中调用此Shape Symbol。

Flash symbol:导通符号

焊盘连接铜皮导通符号,后缀名为*.fsm。

在PCB设计中,焊盘与其周围的铜皮相连,可以全包含,也可以采用梅花辨的形式连接,我们可以将此梅花辨建成一个Flash Symbol、在建立焊盘时调用此Flash Symbol。

创建自定义焊盘及封装

具体方法点右边链接:这个写的挺详细了

下面的是我学的时候遇到的问题

找不到 layout > PIN

因为你用错了Product,我用了下面这个,(GXL好像比较适合仿真)

(20190830现在我用第一个,不是图中的第一个,是软件上拉第一个)

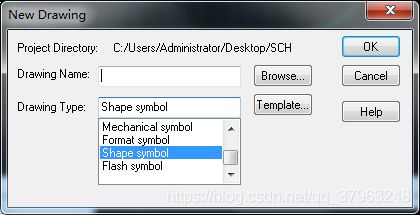

创建焊盘图形文件的类型选择

:

别瞎选,不然后面就白做了

下面方框里的看清楚了,制作图形前还能改(做形状的选Shape,做封装的选Package)

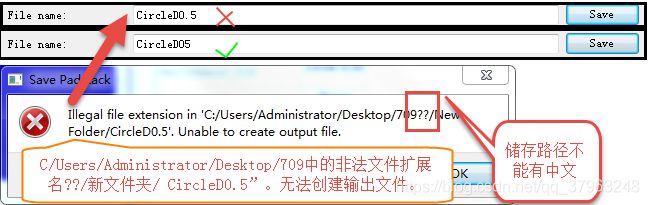

焊盘保存失败的原因

找不到自己做的焊盘怎么办

调用自制焊盘的库文件:

打开PCB designer–>点击Setup–>User Preferences–>分别搜索padpath和psmpath–>选择添加工作路径–>分别点击OK

生成板框

以板框尺寸30mmx50mm为例。

(1)在新建的PCB界面中执行菜单命令Setup>Design Parameters,在弹出的Design Parameter Editor窗口中打开Design选项卡;

(2)在Size栏中Use units中选择Milimeters 为单位,精度Accuracy选择4位;

(3)在Extents 栏中设置工作区大小,Left X、Lower Y文本框中分别输入20,Width和Height文本框中的数值至少要大于LeftX.LowerY加上板框的尺寸,如输入100;

(4)执行菜单命令Add-Line,在Options面板中选择Board Geometry和Outline;

(5)建议用输入命令的方式绘制,在命令栏连续输入x 0 0回车、x 30回车、y 50回车、x 0回车、y 0回车,最后在工作区域单击右键,选择Done,完成绘制;

(6)为了后续设计方便,建议将线组成的Outline生成Shape形态的;

(7)执行菜单命令Shape-Compose Shape,Options面板中的Active class下拉列表框中选择Board Geometry,Add shape to subclass下拉列表框中选择Outline.Find面板中只勾选Lines;

(8)用鼠标右键的Temp Group功能选择设计区城所有的板框线,然后用Complete命令结束选择,命令栏提示A total of I shapes were created,表示创建成功;

(9)通常还需要将原点设置到板框左下角,或者将左下角板框延长线交接点处。执行菜单命令Setup-Change Drawing Origin,然后在左下角单击右键,选择Snap pick to-Arc/Circle Center,软件自动将原点设置到该点;

区域的类型:

Package Keepin:表示在该区域内可以放置元器件,在PCB板框确定后,可设置比板框内缩一定宽度的Package Keepin区域,使元器件布局时不会靠板边太近,提高可制造性,通常内缩120mil。

Package Keepout:表示在该区域内禁止放置超高器件,默认为不允许放置任何元器件,可设置允许放置的元器件高度,需要与元器件封装配合。

Route Keepin:表示该区域内允许布线,在PCB板框确定后,会设置板框内缩一定宽度的Route Keepin区,通常内缩40mil.

Route Keepout:表示在该区域内禁止布线、敷铜、打孔,在设计过程中有很多元器件底下不允许铜存在,如变压器、晶振等,可通过设置Route Keepout来避免内部走线

Via Keepout:表示在该区域内禁止打孔

Shape Keepout:表示在该区域内禁止敷铜。

绘制Route Keepin

(1)执行菜单命令Edit-Z-copy,在Options面板中选择ROUTE KEEPIN和ALL,在Size处选中Contract单选按钮,Ofset后的文本框中的输入40,表示区域内缩40,Find面板中仅勾选Shapes复选框。

(如果出现这个错误Shape collapsed as a result of expansion,可能是內缩太大了.,你画的框没那么大)

(2)在设计区域单击板框图形,即可创建Route Keepin.。

导人网表

设置封装库路径

网表中定义了元器件所用到的PCB封装,因此在导入网表之前必须先设置好PCB封装库路径,以便网表能正确导入,设置步骤如下。

(1)执行菜单命令Setup-User Preferences",在下图界面中单击padpath右侧的浏览按钮。(焊盘)

(2)根据实际封装库路径选择对应的目录,有多个目录时,优先顺序是从上往下,

(3)psmpath的目录设置方法类似。(封装)

(4)在设置时,可以采用相对路径的描述方式,如用“."表示当前目录;另外,还可以通过编辑env文件修改文件中的padpath,psmpath所指向的目录来定义封装目录。

导入网表

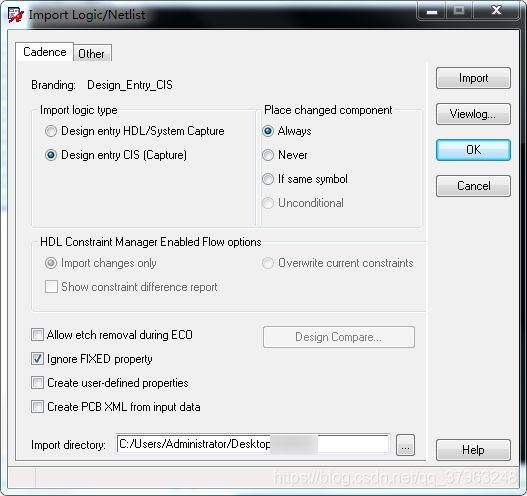

(1)在Allegro中执行菜单命令File-Import-Logic,弹出Import Logic对话框,打开Cadence选项卡

(2)Import logic type:导入网表的类型,包括以下两种。

Design entry hdl:Allegro design authoring类型网表。

Design entry cis:OrCad Capture类型网表,这里使用此类型网表。

(3)place changed component选项组中,各选项功能如下。

Always:表示全部元件无论在原理图中是否被修改过,均放置在网表导入前原位置,建议选择此项。

Never:表示如果元件在原理图中修改过,allegro会将其放置在后台,等待重新放置。

If same symbol:表示只变更原理图中有改变的元件的封装。

(4)Allow etch removal during ECO:表示导入网表时允许删除现有相关的走线。

(5)Ignore FIXED property:表示忽略固定属性的元器件,建议勾选。

(6)Create user-defined properties:表示将原理图自定义的属性导入PCB.

(7)Create PCB XML from input data:表示创建xml格式的文件。

(8)Impot directory:表示导入原理图网表的路径,单击右侧的浏览按钮,指定网表所在目录

(9)设置所有参数后,单击Import Cadence按钮导入网表,如果调入网表出错,可查看自动打开的报告文件,或者用文本编辑软件在当前目录下打开netrevilst,查阅其中的ERROR和WARNING项,并对应解决。