ADC精度的分析

ADC广泛用于各种应用中,尤其是需要处理模 拟传感器信号的测量系统,比如测量压力、流量、速度和温度的 数据采集系统(仅举数例)。在任何设计中,理解这些类型应用的总系统精度始终都是非常重 要的,尤其是那些需要对波形中极小的灵敏度和变化进行量化的系统。理想情况下,施加于信号链输入端的每一个伏特都由ADC 以数字表示一个伏特的输出。但是,事实并非如此。所有转换器 和信号链都存在与此相关的有限数量误差。

今天为大家分享的文章描述了与模数转换器本身相关的误差,还揭示了转换器内部的不精确性累积到何种程度即会导致这些误差。

1 ADC的不精确性

无论何种信号链,转换器都是系统的基本要素。为设计选择的任 何ADC都会决定系统的总精度。换言之,系统精度不可能高于转换器的最低有效位(LSB)大小。为了表明这一点,让我们来看一个 简短的ADC不精确性指南。

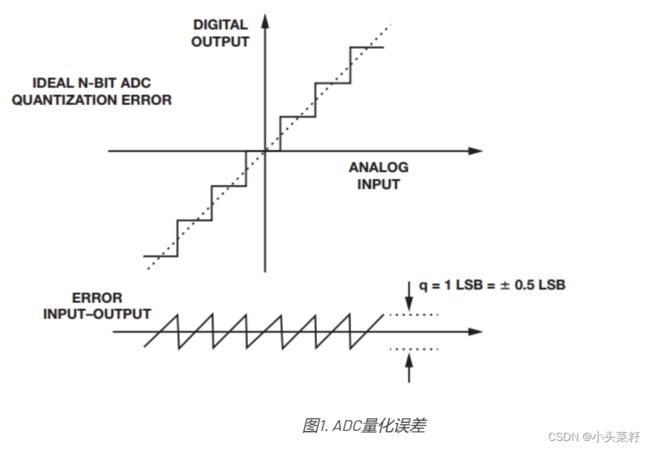

1.1 LSB

首先,注意到由于ADC不是理想的,并且分辨率有限,因此它们 在输出端只能显示有限数量的信息表示。表示的信息数量由转换 器满量程输入除以2N 表示,N为转换器的理想位数。

例如,假设选择一个12 bit ADC,则它可在输出端以4096个数字表示施加于转换器输入端的任何信号。这些表示信息确实存在有限量的误差。因此,如果12位ADC的输入满量程(VFS)为10 V p-p,那么其理想情况下的LSB大小为2.44 mV p-p,精度为±1.22 mV。

1.2 KT噪声

而实际上,ADC是非理想的。在转换器内部存在一定噪声, KT/C

甚至直流中也有噪声。记住,1 kΩ电阻等效于4 nV∙Hz (1 Hz带 宽,25°C)。注意,查看12位ADC数据手册时,SNR通常为大 约70 dB到72 dB。但是,根据下列公式,一个12位ADC理想情 况下应当具有74 dB:

SNR (dB) = 6.02 × N + 1.76 (公式2 )

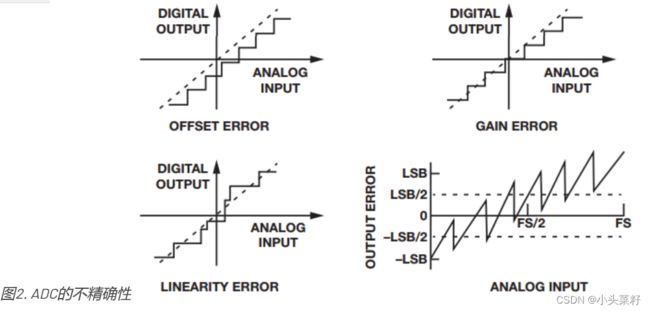

因此,实际上12位分辨率是无法达到的,因为转换器本身存在一 定的不精确性,如图2所示。

这些不精确性或误差决定了转换器表示信号的效率,并最终为信号链所接收。失调误差定义为传递函数无法通过零点的模拟值。 增益误差是失调误差为零时理想与实际传递函数之间的满量程数 值之差。通常意义上的线性度误差或非线性度是指零电平与满量 程之间的直线偏差,如图1所示。

2 有关ADC不精确性的更多信息

对最基本的模数转换器误差进行定义并有所了解后,再说明这些误差的区别会有些帮助。大部分ADC的失调和增益都存在这种小误差,通常可以忽略或通过外部模拟电路调节(消除),或者采用数字技术校正。然而,诸如线性度、量化和温度系数等其他误差无法轻易调节或消除。

模数转换器线性度只与转换器自身有关,即取决于架构和工艺变化。有很多方法可以校正,但都很昂贵。设计人员有两种选择: 购买更好、成本更高的转换器,或采用数字手段校正线性度。数字校正的成本也十分高昂。这意味着可能需要更多资源来指定 DSP或FPGA,因为线性度会随温度和工艺的变化而改变。根据采样速率、IF和分辨率,数字校正可能需要广泛的特性表述和查找表,以便即时校正或调节ADC的性能。

2.1 DNL和INL

线性度有两种类型的误差:它们是差分非线性和积分非线性, 通常分别称为DNL和INL。DNL定义为偏离理想值的一切误差或偏 差。换言之,它表示两个相邻代码的模拟差与理想代码值VFS/2^N 之间的偏差。可将其看作与ADC的SNR性能相关的因素。随着代码的偏差越来越大,转换数也随之下降。该误差在温度范围内的界限为±0.5 LSB,可保证无失码。

INL定义为零电平和满量程之间的理想直线近似曲率偏差。多数情况下,INL决定了ADC的SFDR性能。INL总偏差形状可以决定最主要的谐波性能。比如,INL曲线呈弓形会相应产生更差的偶次谐 波,而INL曲线呈S弓形则通常产生奇次谐波。该误差本质上与频 率有关,并与这类误差分析无关。

哪怕可以消除静态失调和增益误差,与失调和增益误差有关的温度系数将会依然存在。

例如,一个12位ADC具有10 ppm增益误差,或FSR/°C = 0.001%/°C。 12位系统中的1 LSB为¼096,或者近似等于0.024%。

因此,若125°C ∆ (–40°C至+85°C),则产生±2.5 LSB增益温度系数误差,或0.001% × 125 = 0.125%。

其中,0.125/0.024 = 5.1或±2.55 LSB。

对于失调温度系数,5 ppm失调误差或FSR/°C = 0.0005%/°C。

这将产生±1.3 LSB失调温度系数误差,或 0.0005% × 125 = 0.0625。其中,0.0625/0.024 = 2.6或±1.3 LSB。

2.2 其他误差

ADC误差分析影响转换器性能的其它误差来源有:CMRR、时钟抖动、固有电 路板噪声、耦合等等。所有这些误差最终都决定了ADC如何有效 地表示信号;通常在频率域内ADC能更高效地表示自身。 从时域角度来看,分析转换器的总精度需要了解下面五个误差:

- 相对精度DNL,定义为±0.5 LSB

- 相对精度温度系数和DNL温度系数,通常包含在数据手册的相 对精度规格中。

- 增益温度系数误差,为±2.5 LSB (数据来源于上文示例)

- 失调温度系数误差,为±1.3 LSB (数据来源于上文示例)

- 电源灵敏度,通常以第一奈奎斯特区内的低频PSRR (电源抑制 比)表示。对于12位ADC而言,它一般可表示为60 dB或±2 LSB。

只需进行方和根(RSS)运算,所有这些误差源构成±3.5 LSB总转换器 误差。这个结果可能过于悲观了。然而,统计容差结果可能过于 乐观了,或者总误差之和除以误差数,即(0.5 + 2.5 + 1.3 + 2)/4 = ±1.58 LSB。ADC实际容差应当介于这两种思路或方法之间。 因此,当在转换器中加入精度误差的时候,或者进行任何系统 精度分析的时候,设计人员应当使用加权误差源法,然后对这 些误差源进行RSS计算。这是确定ADC总误差的最佳方法。因 此,±0.5 LSB的相对精度应当保持在100%。然而,±2.5 LSB增益 温度系数误差应当是总误差的66%,或2.5/(0.5 + 1.3 + 2) × 100。 ±1.3 LSB的失调温度系数误差将为总误差的26%,或 1.3/(0.5 + 2.5 + 2) × 100。±2 LSB的电源灵敏度误差将为总误差的47%,或2/(0.5 + 1.3 + 2.5) × 100。将这些加权误差以RSS方式相加,或者进行平方根计算:

则总误差为±2.0 LSB,这是一个更接近实际的结果,介于上文乐观方法和悲观方法得出的结果之间。

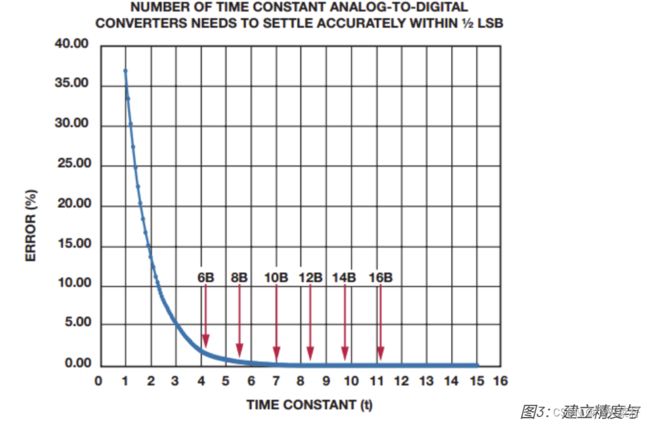

3 带宽精度和建立时间精度

ADC带宽精度 ADC还有建立时间精度。转换器的内部前端需要具有足够的带宽(BW),才能精确地对信号进行采样。否则,累积误差将大 于上文讨论的结果。 一般而言,一个ADC的内部前端需要在半个周期或采样时钟周期内建立(0.5/Fs),这样才能提供对内模拟信号捕捉的精确表达。因 此,对于一个12位ADC(采样速率为2.5 GSPS,满量程输入范围为 1.3 V p-p)来说,全功率带宽(FPBW)可通过下列瞬态公式推导: 1 LSB = VFS × e^(-t/τ) 求解t: t = −τ × ln(1 LSB/VFS) 代入τ = 1/(2 × π × FPBW),一个时间常数,求解FPBW: FPBW = −(1/(2 × π × t)) × ln(1 LSB/VFS) 现在,令t = 0.5/Fs,则样本建立所需的时间如下(样本周期为1/Fs): FPBW = −(Fs/π × ln(1 LSB/VFS) = –(2.5G/π) × ln(317 mV p-p/1.3)) = 6.62 GHz. 这样会使ADC内部前端所需的带宽或FPBW最小。这是转换器内部 前端建立至1 LSB以内并正确采样模拟信号所需的带宽。为了满 足这类ADC的1 LSB精度要求,这将会需要花费数个时间常数。 一个时间常数为24 ps或τ = 1/(2 × π × FPBW)。要了解ADC满量程 范围内达到LSB尺寸要求所需的时间常数数量,就需要找出满量 程误差或%FS。或者1 LSB = FS/(2N),其中N = 位数,或1.3 V p-p/ (212) = 317 mV p-p,且%FS = (LSB/FS) × 100 = 0.0244。 通过描绘欧拉数或eτ ,可以绘出一条曲线,以便每次通过常数都 能方便地看出相对误差。如图3可见,12位ADC样本建立至大约 1 LSB以内需时8.4个时间常数。

设计人员便能估算用于转换器的最大模拟输入频率或采样 带宽,并依旧建立至1 LSB误差以内。超出这个范围,则ADC无法 精确表示信号。这可以简单定义为:FMAX = 1/(τ × 时间常数数量)或 1/(24 ps × 8.4) = 4.96 GHz。 记住,这里表示的是最佳情形,并假定采用单极点ADC前端。并 非所有现实中的转换器都以这种方式工作,但这是一个很好的开 端。例如,上文描述的模型最高可适用至12位,但针对14/16位 以及更高位则需要根据这些细微影响采用二阶模型,以使建立时 间扩展至预测的一阶模型以外。 关于ADC带宽的简要说明 记住,ADC全功率带宽不同于上文定义的转换器可用带宽或采 样带宽。它可以当成是模拟信号输入运算放大器的全功率带 宽(FPBW),信号更像是三角波信号,并且输出端存在大量失 真。FPBW是ADC精确捕捉信号并使内部前端正确建立所需的带 宽(前文示例中为6.62 GHz)。选择一个IF并在该范围内使用转换器 不是一个好主意,因为系统的性能结果会大幅改变;在大约 5 GHz处,如上文示例所示,根据转换器数据手册中的额定分辨率 和性能指标,满量程带宽远高于转换器自身的最大采样带宽。设 计是围绕采样带宽而展开的。所有设计都应当避免使用额定全功 率带宽的某一或全部最高频率部分,否则动态性能(SNR/SFDR)会 下降并大幅改变。为了确定高速ADC的采样带宽,应当使用上文 中的示例,因为这些数据并非总能从数据手册中获取。通常,数 据手册会规定甚至列出转换器采样带宽内经过生产测试、能够保 证额定性能的频率。然而,在较老的ADC产品中这些测试频率在 数据手册中并不总是以FMAX来定义。今后还需要对行业中的这些 带宽术语做出更好的说明、定义和测试。 结论 本文给出了有关如何查看一般静态ADC的不精确性误差和涉及带 宽的ADC不精确性误差的指导说明。还提供了针对ADC误差以及 这些误差如何影响信号链的更深入解释。请记住,并非所有的元 件都采用相同的方式构建,这对于有源和无源器件来说都是正确 的。创建囊括所有这些误差的电子表是插入不同信号链元件的简 便方法,可更快进行评估并决定元件的权衡取舍。这在元件之间 进行成本、尺寸和功耗的权衡取舍以及衡量信号链性能差异方面 尤为如此。