自动垃圾分类管理系统 (项目论文,硬件,FPGA)

本文旨在为FPGA相关的同学和朋友提供参考,请勿传播,欢迎交流,关注我 之后分享更多项目和资源!

目录

1、设计概述

1.1 设计目的

1.2 具体功能描述

1.3 设计思路

2、系统模块功能描述

2.1 系统硬件组成简介

2.2 FPGA 端

2.2.1 主板部分

2.2.2 摄像头

2.3 STM32 控制端

2.3.1 供电设计

2.3.2 STM32 系统以及接口

2.3.3 传感器等外设

2.4 结构设计及功能

3、系统实现

3.1 FPGA 端功能实现

3.1.1 通讯模块

3.1.2 图片及数据处理

3.1.3 PipeCNN

3.2 STM32 端功能实现

3.2.1 通讯模块

3.2.2 红外传感器模块

3.2.3 舵机以及补光灯控制

4、设计完成情况以及参数

4.1 实物演示

4.2 性能参数

5、设计创新点

5.1 迁移学习

5.3 结构稳定简单

6、总结

1、设计概述

1.1 设计目的

随着社会的发展和城市化进程的加快,产生的垃圾逐年增加,因此带来的环 境污染日趋严重。垃圾分类可以有效改善环境质量,实现资源再利用,促进绿色 发展。垃圾分类已成为当务之急。垃圾分类是对垃圾回收处置传统方式的改革, 是目前最有效的科学管理方式之一。但是,由于垃圾的种类很多,垃圾分类政策 的实施时间短,覆盖范围小,所以很多人不能很好地区分垃圾的类型也很少去主 动做分类。针对这一现象,我们设计并实现了一种自动垃圾分类装置,该装置可 以自动识别投放垃圾的类型,并将其放入相应的垃圾桶中。

1.2 具体功能描述

该自动垃圾分类装置,主要功能为自动对垃圾进行识别和分类投放。共设置 有四类垃圾,分别为可回收垃圾、厨余垃圾、有害垃圾和其它垃圾。当装置通过 红外发生器检测到有垃圾投入时,且内部投放口处于关闭状态,摄像头会采集垃 圾图片并将图片信息送入卷积神经网络进行识别和分类,确定垃圾的种类后,装 置会自动将对应类型的垃圾桶旋转至投放口下方,然后打开投放口,垃圾落入对 应类别的垃圾桶。

1.3 设计思路

本系统基于 DE10-standard 开发板,使用 VGG16 的卷积神经网络对垃圾图片 进行识别分类,使用 DE10-standard 开发板与 STM32 把整个系统分成两个部分, 由 STM32 来实现对垃圾桶硬件的控制如垃圾桶舵机的运转,由 DE10-standard 开发板专职完成数据的提取以及计算,两个部分通过四个 GPIO 完成通信,最终 2 实现垃圾分类的目的。 首先如果直接使用 Verilog 完成对整个 VGG16 的 RTL 设计比较困难,其次 如果使用 FPGA 上的操作系统单独完成此部分运行会比较缓慢,所以此处我们依 靠 FPGA 开发板的优势,使用 OpenCl 对整个 VGG16 的运算过程进行加速,软 硬件协同完成整个图像识别的模块。

2、系统模块功能描述

2.1 系统硬件组成简介

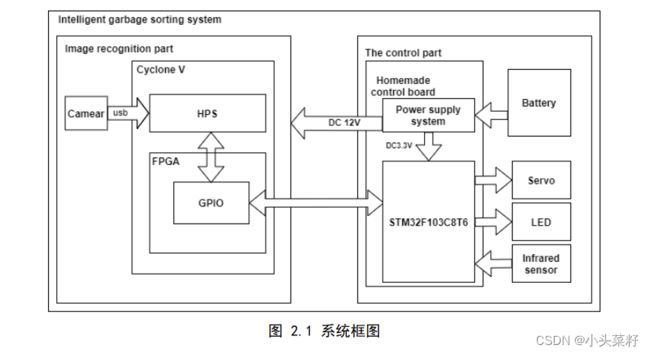

我们的垃圾分类系统主要有两大部分,FPGA 端的主机部分主要用于图像识 别识别的计算和处理与控制端的通讯,STM32 控制端主要用于控制外设工作。 一下是系统的设计框图。

2.2 FPGA 端

FPGA 端硬件上主要有两个部分:DE10-Stander 主板、摄像头。

2.2.1 主板部分

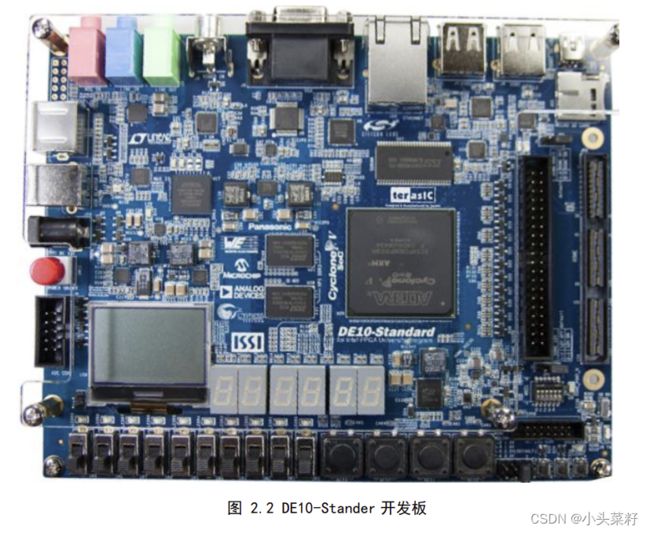

主板我们使用友晶 DE10-Stander 开发板,主板主要用于图像采集、运行主机端 程序、加速 pipeCNN 的计算以及与 STM32 控制板的通讯。DE10-Stander 采用 Cyclone V SX SoC—5CSXFC6D6F31C6N 作为主控芯片,资源有 110,000 个 LE、41,509 个 ALM,5761Kbits 的嵌入式内存 6 个 FPGA PLL、3 个 HPS PLL、两个硬件存储控制 器以及一个基于ARM-A9的HPS部分的硬核处理器。且具有多种标准接口USB2.0、 USB 转 UART、10/100/1000M 网口。采用 12V DC 供电。

2.2.2 摄像头

摄像头我们使用 Logi c270,对于采集图像的摄像头需要有 Linux 的驱动。该 摄像头采集的图片为 720p 画质。摄像头主要用于在识别时对投放的垃圾进行图 像采集。当每次采集完成后,摄像头会关闭。

2.3 STM32 控制端

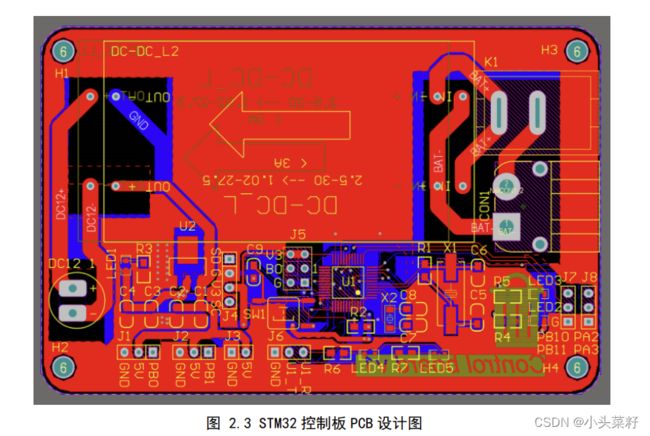

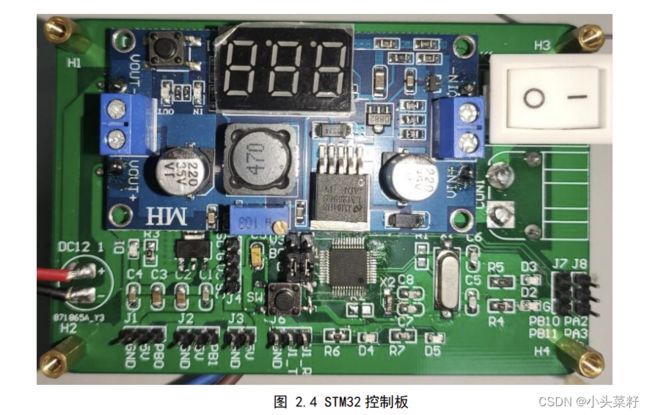

STM32 控制板主要用于驱动外设工作,该部分主要有三大部分:供电设计、 stm32 系统以及接口、传感器等外设。

2.3.1 供电设计

系统的整体供电电源使用 5300mAh 的 4S 航模锂电池,可以为舵机、FPGA 板工作时的大功率需求提供足够的电流,保证系统供电稳定。在供电设计上我们 使用了两块 LM2596 DC-DC 稳压模块分别为 STM32 控制板和 FPGA 开发版供电。

2.3.2 STM32 系统以及接口

STM32 控制部分使用 stm32f103c8t6 作为主控芯片,设计有 SW 下载接口, UART、两路舵机接口、三路红外传感器接口、一路补光灯接口以及板上两个用 于调试的 LED。这些外设接口都是用 STM32 来进行驱动和控制的。同时还有 4 个 GPIO 用于与 FPGA 端进行通讯,主要是来握手以及接收指令。

2.3.3 传感器等外设

STM32 控制板的外设主要是红外传感器、舵机及补光灯。舵机使用 MG90 20kg 舵机可控角度为 270°。红外传感器使用红外对管障碍检测传感器,检测距 离 0.5-30cm 可调。补光板使用两颗大功率 LED 焊接而成。

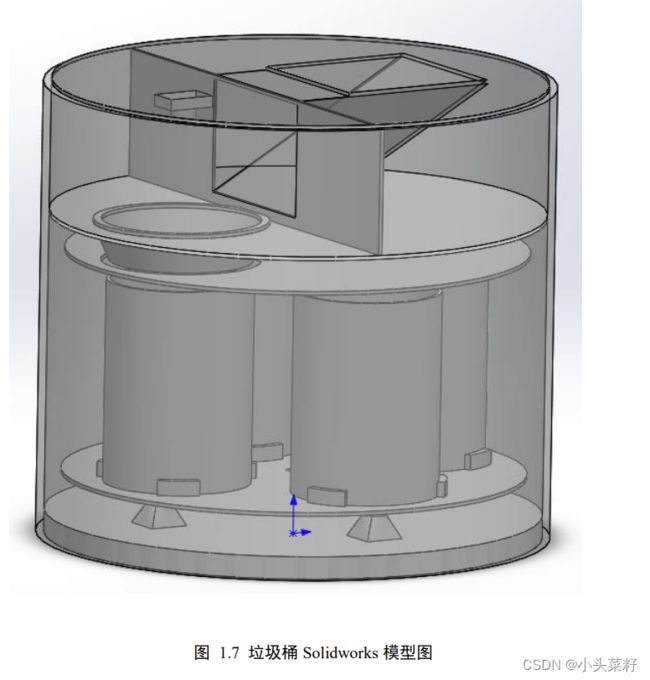

2.4 结构设计及功能

在结构设计上我们采用了筒状双层结构,上层为投放口以及识别区域同时也 固定两块控制板以及电源。下层放置四个分类垃圾桶。在投放垃圾并且识别后下 层对应的垃圾桶会转到投放孔下方,这时挡板会打开垃圾掉入对应垃圾桶,然后 挡板会关闭,等待下一次投放。下图为垃圾桶的机构设计图。

3、系统实现

3.1 FPGA 端功能实现

3.1.1 通讯模块

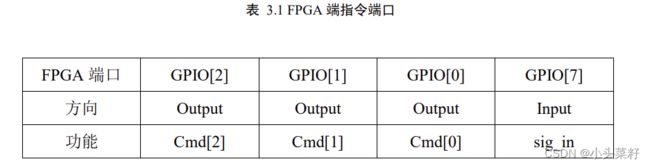

FPGA 与 STM32 通讯的部分我们在自制的 BSP 中添加了一些 GPIO 口用于 握手以及发送指令。

3.1.2 图片及数据处理

在程序运行时主要需要两种数据,一种是 tensorflow 所训练出的 VGG16 的 模型参数,另一个就是图片的像素参数,并且为了以便于后续的计算本系统所有 的参数使用的都是八位有符号定点数。 本系统主要通过摄像头来拍取所需识别的垃圾图片,在 FPGA 的程序中通过 OpenCv 完成此部分功能。但在本系统后续的所有计算中所有的数据都是由八位 有符号定点数完成的,故通过 OpenCv 控制摄像头完成一帧 224*224 的 RGB 图 片的读入,然后将所得像素值与预先准备的 mend_data 相减,将 0~255 的数据转 入到-127~127,使其可以由有符号八位二进制表示,便于后续的计算。 在上述 tensorflow 中所有训练的参数都是 32 位浮点数,并且是由 tensorflow 的格式来存储的。首先需要把所有参数从 tensorflow 中提取并存储,通过 Matlab 的 fit()函数将其转化成八位有符号定点数并储存位二进制文件。在程序运行时可 以直接读取二进制文件得到整个 VGG16 的模型参数。

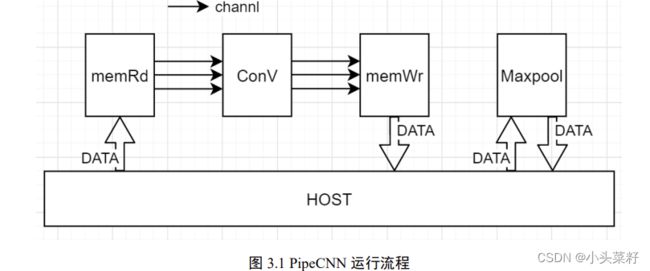

3.1.3 PipeCNN

此模块使用 OpenCl 完成,主要用于实现整个 VGG16 的计算,分为主机端与 设备端两个部分,通过主机端的控制以及设备端使用 OpenCl 加速计算得到最后 的计算结果。 PipeCNN 设备端主要由四个函数完成:memRd、Conv、memWr、Maxpool。 其工作流程可以由下图表示。

memRd 主要接收从主机端传输的数据以及配置信息。通过对配置信息的解 析完成对数据的分组,使用 OpenCl 中的 Channl 将所需运算的数据直接传送给后 续的 ConV 函数。 ConV 可以从 memRd 接收到 DATA、weight、bias 三组数据之后,然后可以 完成 DATA*weight+bias 的计算,通过移位近似等操作,将所得的 int 类型的数据 转成八位有符号二进制数,通过 Channl 写入到 memWr 中。 memWr 主要从 Channl 中接收 ConV 传输的数据将其按照特定格式排列,以 便于下一循环使用。 Maxpool 主要完成卷积神经网络的池化操作,然后按照特定排列方式写入到 主机端,为下一次卷积使用。 主机端主要完成 OpenCL 设备的初始化以及在循环中完成对不同设备端函数 的调用,最后完成整个 VGG16 的计算。

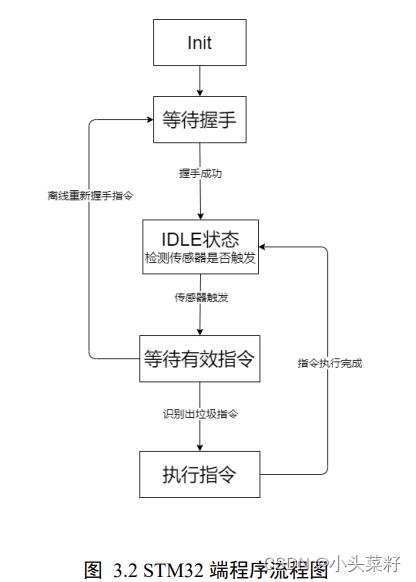

3.2 STM32 端功能实现

STM32 端的功能在软件上的实现比较简单,程序的主循环为四个状态的状态 机,等待与 FPGA 端握手的状态、IDLE 状态检测传感器状态、等待有效指令状 态、执行指令状态。STM3 端主要协助 FPGA 端对硬件进行控制,包括采集传感 器状态、控制舵机和补光灯。下图为 STM32 端的程序流程图。

3.2.1 通讯模块

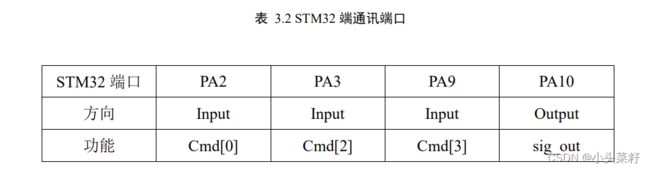

STM32 端的通讯有三个输入口和一个输出口,主要用于初始化完成后主机端 和从机端的握手以及正常工作时接收指令以及响应。

3.2.2 红外传感器模块

红外传感器模块的在工作时,当无障碍物时传感器的输出口为高电平,当有 障碍物在检测范围内出现时,输出口会跳变为低电平,我们在软件上检测传感器 输出口的下降沿即可以获取投掷垃圾的触发信息,并将触发信号传递给 FPGA 端。

3.2.3 舵机以及补光灯控制

我们使用的舵机为 270°的数字舵机,只需要输入一个高电平为 0.5-2ms 周期 20ms 的 PWM 信号即可实现对垃圾桶的挡板和分类垃圾桶的位置控制。

4、设计完成情况以及参数

4.1 实物演示

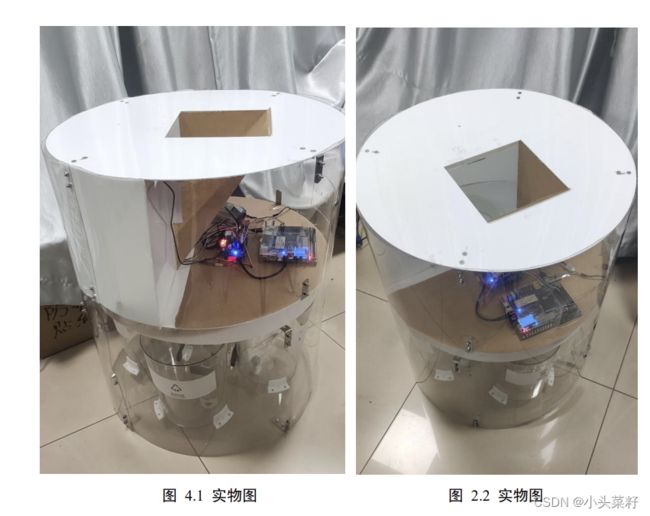

实物演示视频我们已经上传至优酷: https://v.youku.com/v_show/id_XNTg1NzkwODkzMg==.html 每次再开机之后需要连接显示器,使用键鼠打开整个工程运行,然后初始化 完成之后命令行会出现“waiting for start signal from stm32” 然后从投放口投放 垃圾,之后 STM32 会打开补光灯同时向 FPGA 开发板发送启动信号,FPGA 开 发板会控制摄像头拍取垃圾图片并开始计算,当计算完成之后显示屏会显示图片 并将其预测结果放在图片左上角。然后返回给 STM32 对应垃圾的信号。STM32 会根据接受的信号首先打开下方舵机把对应垃圾桶旋转至投放口下方,随后打开 上方舵机的挡板使垃圾调入垃圾桶,完成此次循环。 下图为实物图:

4.2 性能参数

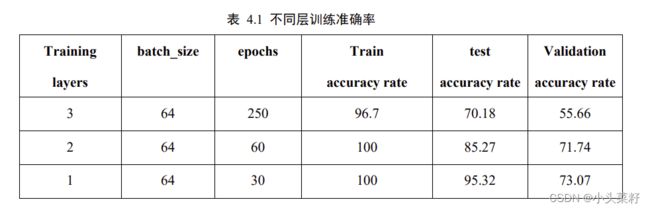

训练的模型我们采用基于 ImageNet 的经典模型 VGG16,此前我们尝试过自 行搭建简单网络,但是不仅识别效果较差,而且使用 Opencl 所占用资源也非常 多。经过探究之后选用了此模型。由于 VGG16 模型较为复杂,参数量巨大,我 们选择冻结其全连接层之前的参数,针对我们需求的种类更改之后只对全连接层 进行训练。由于一共有三层全连接层,我们分别测试了训练 3 层、2 层和 1 层全 连接层的效果。结果如表中所示,可以看出,仅训练一层时效果最好。最终的准 确率高达 72.2%。

5、设计创新点

5.1 迁移学习

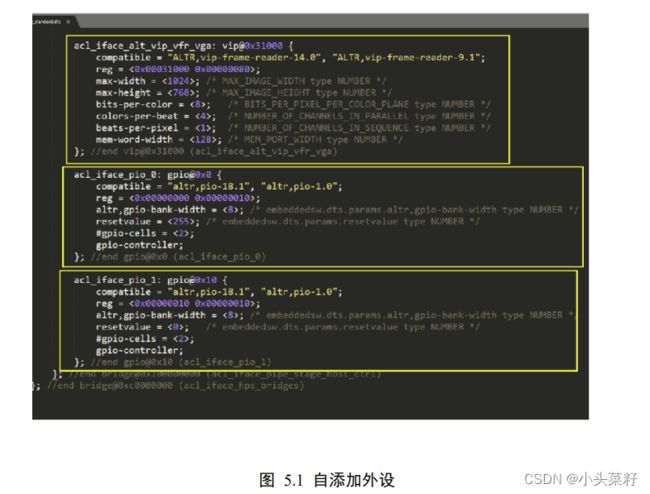

使用迁移学习是因为 VGG16 网络非常复杂,训练起来参数量很大,对于硬 件需求较高,因此我们采用迁移学习来对其进行微调。减少训练的参数量同时加 快训练速度。 5.2 自制 BSP 我们在操作系统上重新编译了内核和设备树文件,使 DE10-standard 支持 USB 摄像头以及对 FPGA GPIO 外设的直接控制。硬件上我们在官方提供的 BSP 基础上,重新制作了一套 BSP, 增加了我们需要的外设。以下是外设 BSP 增加 的部分。

5.3 结构稳定简单

最后是结构上我们采用了双层旋转式投放方式,可以有效存放识别前的垃圾 和快速投放识别后的垃圾。同时这一设计使它体型小巧,外形美观符合当下流行 趋势

6、总结

针对本系统所分的垃圾种类,对基于 ImageNet 的 VGG-16 模型的进行重训 练,本系统的识别正确率达到了 90%; 把 VGG-16 所训练出的浮点参数转换成对应的定点参数,在 FPGA 中运行时, 只会产生 2%的误差,极大的提高了其运算速度并减少了运行时所占用的 FPGA 硬件资源。 本系统使用有限的 FPGA 硬件资源,基于 PipeCNN 完成了 VGG-16 模型的 参数计算,在有限的资源下不仅保证了 4s 计算一次的速度外,在完成本系统的 职能即垃圾投放的正确率上也达到了 95%