IC低功耗设计

目录

一.功耗源

(1)浪涌

(2)静态功耗

(3)动态功耗

二.低功耗实现方法(按层次划分)

(1)系统级

(2)体系结构级

(3)寄存器传输级

(4)寄存器级

三.补充

四.参考文献

一.功耗源

(1)浪涌

浪涌电流指器件上电时产生的最大瞬时输入电流(启动电流),浪涌电流与设备有关(不同设备的浪涌电流是不同的),例如基于SRAM的FPGA有很突出的浪涌电流,因为上电时这些器件没有配置,所以需要从外部存储器中下载数据来配置其编程资源(如布线连接和查找表)。

(2)静态功耗

关断主电源或系统进入待机模式下产生的电流,由此电流产生的功耗称为待机功耗,同样与电气特征密切相关;而静态功耗也包含电路中由晶体管的漏电流所导致的功耗;在不同温度环境中,静态功耗也会随着温度的升高而增大。

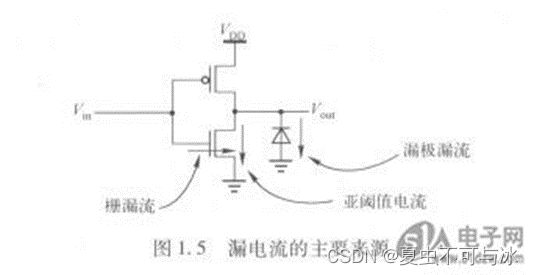

静态功耗主要是由漏电流引起的,漏电流的主要来源如图,包括以下几种。

- 亚阈值漏流(Sub-threshold Leakage,/SUB):当晶体管处于弱反型时,从漏极到源极的电流。

- 栅漏流(Gate Leakage,/CATE):由于栅氧隧道效应和热载流子注入,直接从栅电极经过栅氧化物到达衬底的电流。

- 栅致漏极漏流(Gate Induced Drain Leakage,/GIDL):由于高K介质。在MOSFET的漏极形成高的场效应,而导致的从晶体管漏极到衬底的电流。

- 反偏结漏流(Reverse Bias Junction Leakage,/REV):耗尽层中由于少子的漂移以及电子/空穴对的产生而引起的电流。

(VDD的降低将导致低的晶体管开电流或者驱动电流VDS,从而降低电路的速度。)

(3)动态功耗

门电路输出切换时,由逻辑转换所引起的功耗,主要由电容充放电引起。动态功耗又包括翻转功耗和短路功耗。

翻转功耗是指数字电路完成功能计算所必须消耗的功耗,是有效功耗。短路功耗是指cmos在翻转过程中pmos、nmos同时导通消耗的功耗,是无效功耗。

动态功耗=翻转次数*门寄生电容*供电电压的平方*时钟频率

而ASIC的总功耗为 静态功耗+动态功耗

频率只影响动态功耗,不影响漏电。温度越高,漏电越大;电压越高,漏电越大;工艺的话情况比较复杂,从阈值角度出发,阈值越高,漏电越低。

二.低功耗实现方法(按层次划分)

在FPGA设计中,降低功耗直接提高了整个系统的性能和质量,降低了成本,可以延长器件的使用寿命,对系统的开发有积极作用。

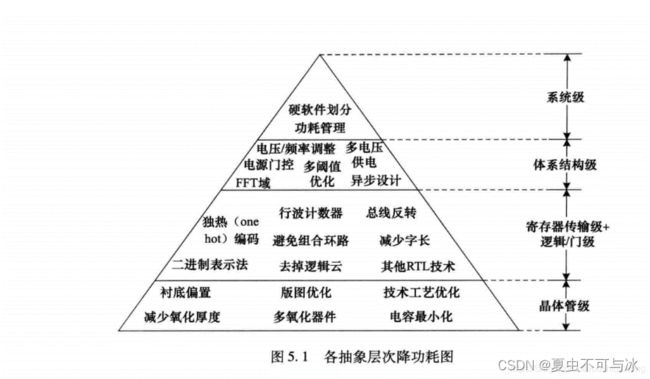

(系统级、逻辑级、物理级)层次越高对功耗的减低就可能越有效。

(1)系统级

- 片上系统方法:由于I/O使用比芯片内核逻辑更高的电压供电,因此芯片间的连线将消耗大量的功耗,片上系统方法学主要关注降低功耗,缩减面积以及降低成本的手段。

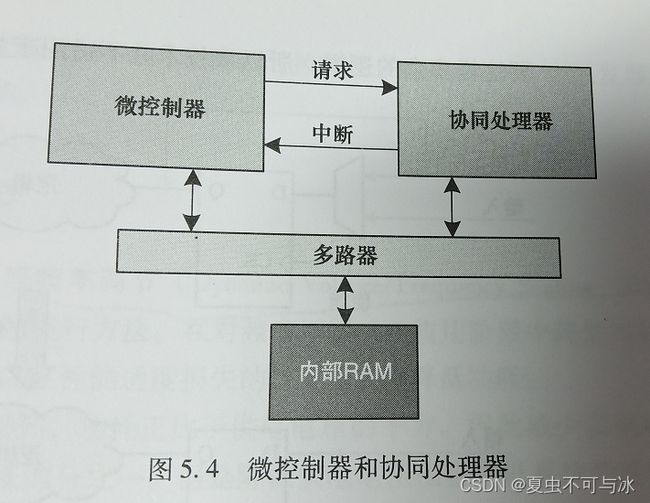

- 硬件/软件划分:如果这些资源密集型模块用硬件标识和实现,就能节约大量功耗。协同设计的常规技术是在设计的早期将系统划分为硬件和软件部分并反复优化以得到最佳方案。一种比常规更有效的HW/SW划分方法是使用基于模型的方式,可以使用SystemC建立模型。

- 低功耗软件:通过修改应用软件可以大量降低功耗。合并循环也可以降低功耗。

- 选择处理器:处理器的选择会对整体功耗产生明显影响。最好的系统体系结构是使用特定的机器(协处理器)来执行这个任务,以使任务在最小且能效最高的机器中完成。

(2)体系结构级

1.高级门控时钟(降低动态功耗):通常情况下,时钟树由大量的缓冲器和反相器组成,时钟信号为设计中翻转率最高的信号,时钟树的功耗可能高达整个设计功耗30%。加入门控时钟电路后,由于减少了时钟树的开关行为,节省了开关功耗,同时,由于减少了时钟引脚的开关行为,寄存器的内部功耗也减少了。使用门控时钟不符合同步设计的思想,ASIC中使用较多,FPGA中不推荐使用。(门控时钟和可变频率时钟:门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证;)

2.动态电压频率调节(Dynamic Voltage/Frequency Scaling,DVFS)(动态低功耗技术)(可以通过降低时钟速率和供电电压节省大量能量)动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,但是仅仅降低工作电压会导致传播延迟加大,执行时间变长;将不同模块的工作电压和工作频率尽量调低到刚好满足SOC系统的最低要求来实现降低系统的功耗,这种方法最为复杂;

3.并行结构与流水线技术:并行结构的原理是通过牺牲面积来降低功耗,流水线技术本质上也是一种并行,由此可见,流水线技术能显著降低系统功耗。通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。

4.基于缓存的系统体系结构:在系统存储器或RAM和处理器之间增加缓存(Cache的低功耗设计:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。)

5.对数FFT体系结构:对于要大规模运算的应用,使用对数系统(LNS)比使用线性系统更好。LNS在降低平均位元活跃性的同时用加法和减法实现乘除运算,使其效率比线性系统更高。

6.异步(无时钟)设计:异步电路本质上进行自我控制,因此也成为自定时电路。异步电路基于依赖延迟不敏感代码的信号交换接口,其中最流行的是双轨道编码。

7.8.电源门控(电源切断技术):电源门控方法也称为多电源方法,其思想是芯片上的一些模块可以根据需求采用不同的电源网络供电,这样当一个模块不需要工作时,这个模块可以断开电源,如手机处于待机状态时的多媒体处理单元,从而做到零功耗;设计者可使用两类电源门控:细粒度电源门控和粗粒度电源门控。静态低功耗技术

9.多阈值电压(静态低功耗技术):低阈值的标准逻辑单元具有速度快、漏电流大的特点,高阈值的标准逻辑单元具有速度慢、漏电流小的特点;

![]()

在关键路径上可以使用低阈值的逻辑单元来优化时序,在非关键路径上可以使用高阈值的逻辑单元来降低漏电流;使用多阈值工艺设计的另一个优点是没有任何面积开销,工艺库设计时将两种阈值的逻辑单元面积设计成一样,这样可以方便替换。

10.多电压供电(动态低功耗技术):对于SOC系统,可以让不同的模块使用不同的电压并以不同的频率运行,对于多电压域设计,需要在不同的电压域之间使用一些电平转换单元,将输入电压转换成输出所需的电压范围。

11.存储器电源门控:在典型的SOC中,SRAM消耗了总功率的1/3,所以对于好的电源管理策略,存储器架构是个关键因素。

(3)寄存器传输级

- 状态机编码和解码(格雷码):通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。

- 二进制数表示法:在大多数应用中,用补码来表示二进制数往往比有符号数更常使用,然而,对于某些特殊应用,在切换过程中有符号数更有优势(翻转少)。

- 门控时钟基础

- 独热码多路器

- 除掉多余的转换

- 资源共享:对于涉及较多算数运算的设计,如果有同样的操作在多处使用,必须避免运算逻辑在多个位置重复出现。

- 使用行波计数器、总线反转、高活跃度网络、禁用和启用逻辑云。

(4)寄存器级

- 更先进的硅处理技术

- 版图优化

- 衬底偏压:由于漏电流是阈值电压的函数,因此能减少漏电功耗。在PMOS中,指将晶体管衬底偏置到高于Vdd的水平。在NMOS中,指将衬底电压偏置到高于VSS的水平。

- 减少氧化层厚度

- 多氧化层器件

- 利用定制设计减小电容

三.补充

统一功耗格式(UPF,uniform power format)是被业界广泛采用的低功耗设计和验证的描述文件格式;UPF是为了在相对高的层次上描述功耗设计示意图,例如采用多电压域技术就需要定义:两个不同的电压域之间如何转换?

![]()

在RTL代码中插入UPF指令,通常要做的是定义电压域、定义电源状态、定义对特殊信号的隔离及保持寄存器等。在RTL+UPF仿真的这一步中就可以验证电压域、隔离单元、保持寄存器等逻辑的正确性;

四.参考文献

[1]Mohit Arora.硬件架构的艺术(数字电路的设计方法与技术)[M].北京:机械工业出版社,2014:90.