浅谈FPGA基础入门相关知识,一文让你了解清楚

FPGA作为一种高新技术,结构有着特殊性,越来越受到电子爱好者的青睐,其应用已经逐渐普及到了各行各业。

很多人想要进入FPGA的大门了解这门技术,IC修真院为大家整理了FPGA基础入门相关知识,下面我们就一起来了解一下吧。

FPGA简介

FPGA普遍用于实现数字电路模块,用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的需求。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。可以毫不夸张的讲,FPGA能完成任何数字器件的功能,下至简单的74电路,上至高性能CPU,都可以用FPGA来实现。FPGA如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。

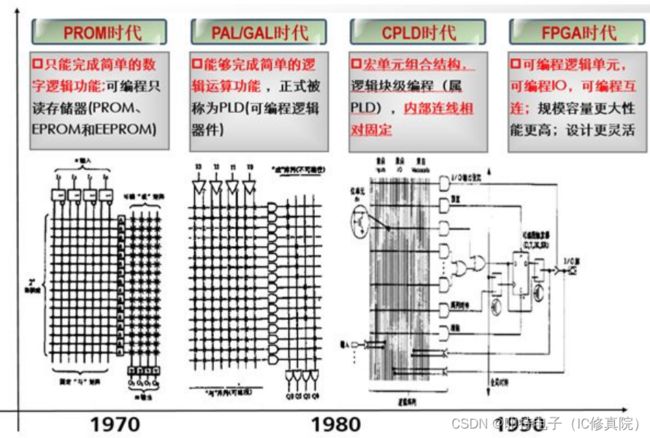

FPGA发展史

FPGA的发展历史如下图所示。相对于PROM、PAL/GAL、CPLD而言,FPGA规模更大性能更高。

FPGA芯片主流生产厂家包括Xilinx、Altera、Lattice、Microsemi,其中前两家的市场份额合计达到88%。目前FPGA主流厂商全部为美国厂商。国产FPGA由于研发起步较美国晚至少20年,目前还处于成长期,仅限于低端,在通信市场还没有成熟应用。

2015年12月,Intel公司斥资167亿美元收购了Altera公司。Altera被收购后不久即制定了英特尔处理器与FPGA集成的产品路线图。这两种产品集成的好处是可以提供创新的异构多核架构,适应例如人工智能等新市场的需求,同时能大幅缩减功耗。

FPGA在电信领域的应用历史

FPGA在航天、军工、电信领域有非常成熟和广泛的应用。以电信领域为例,在电信设备一体机阶段,FPGA由于其编程的灵活性以及高性能被应用网络协议解析以及接口转换。

在NFV(NetworkFunction Virtualization阶段,FPGA基于通用服务器和Hypervisor实现网元数据面5倍的性能提升,同时能够被通用Openstack框架管理编排。

在云时代,FPGA已经被作为基本IaaS资源在公有云提供开发服务和加速服务,AWS、华为、BAT均有类似通用服务提供。

截至目前,Intel的Stratix 10器件已被成功应用于微软实时人工智能云平台Brainwave项目。

FPGA的缺点

FPGA的缺点是成本高,为什么这么说呢?专用的电路一定是把所有的电路都用上了,来实现我们所需要的功能。FPGA要同时满足A、B、C的功能。但满足A的某些功能在B或C上肯定是用不上的,所以它的利用率比较低,也可以理解为它的成本高。

所以FPGA只能做一些高端的少批量的运用。当发现市场前景非常好,想要降成本的时候,可以把FPGA的代码变成集成电路去生产。

FPGA的基本结构

FPGA不像专用的ASIC那样通过固定的逻辑门电路来完成,而只能采用一种可重复配置的结构来实现,查找表(LUT)可以很好的满足这一要求。

查找表(Look-Up-Table)是什么?其本质上是一个RAM存储器。

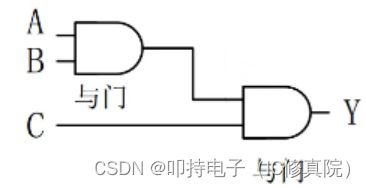

举例说明,以数字逻辑Y=A&B&C为例。在专用ASIC中,为实现该逻辑,逻辑门都已经事先确定好,如下图所示:

Y=A&B&C的实现结构

在FPGA中就不一样。A、B、C通过编程可以是任意关系。设计过程如下:

先用代码写出Y=A&B&C,然后用EDA工具(QUARTUS或其他开发工具)分析这一行代码,得出A、B、C在不同输入组合下(共8种),Y的值分别是多少,其真值表如下图所示:

然后,软件工具将所有结果写到查找表(LUT)上,从而实现该代码的功能。

FPGA应用场景

FPGA功能强大,试验难度大,一般用在通信接口的设计以及数字信号处理等比较高端(数据量大、数据传输快、精度要求高)的场合。日常应用中,要求不是特别高的场合广泛使用单片机来实现。

FPGA还有一个特殊的应用场合,即ASIC的原型验证。

怎么理解?集成电路开发流程长,风险高,当做一个集成电路开发的时候,从代码编写到仿真验证,到PCB的布局布线,再到最后的生产都需要经过很长的时间周期。

为了保证成功率,希望一次通过,在生产之前可以在FPGA上跑一跑,验证一下功能是否正常。

FPGA的非标场合(用量少的场合,常用于军工领域。)

例如,USB等接口标准是固定的。但有一些特殊场合,它的市场需求本身不大,它本身也是某种特殊定义的接口,这种接口在市场上很难找到对应的芯片去实现这种接口,这时FPGA就可以派上用场,可以自己设计内部结构电路跟这种接口进行对接。

FPGA学习重点

1. 看代码,建模型

只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的时候应该想到是什么样的功能电路。

2. 用数学思维来简化设计逻辑

学习FPGA不仅逻辑思维很重要,好的数学思维也能让你的设计化繁为简,所以啊,那些看见高数就头疼的童鞋需要重视一下这门课哦。举个简单的例子,比如有两个32bit的数据X[31:0]与Y[31:0]相乘。

当然,无论Altera还是Xilinx都有现成的乘法器IP核可以调用,这也是最简单的方法,但是两个32bit的乘法器将耗费大量的资源。那么有没有节省资源,又不太复杂的方式来实现呢?我们可以稍做修改:

将X[31:0]拆成两部分X1[15:0]和X2[15:0],令X1[15:0]=X[31:16],X2[15:0]=X[15:0],则X1左移16位后与X2相加可以得到X;同样将Y[31:0]拆成两部分Y1[15:0]和Y2[15:0],令 Y1[15:0]=Y[31:16],Y2[15:0]=Y[15:0],则Y1左移16位后与Y2相加可以得到Y,则X与Y的相乘可以转化为X1和X2 分别与Y1和Y2相乘,这样一个32bit32bit的乘法运算转换成了四个16bit16bit的乘法运算和三个32bit的加法运算。转换后的占用资源将会减少很多,有兴趣的童鞋,不妨综合一下看看,看看两者差多少。

3. 时钟与触发器的关系

“时钟是时序电路的控制者”这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。

但是时序电路就不同了,它的所有动作都是在时钟一拍一拍的节奏下转变触发,可以说时钟就是整个电路的控制者,控制不好,电路功能就会混乱。

打个比方,时钟就相当于人体的心脏,它每一次的跳动就是触发一个 CLK,向身体的各个器官供血,维持着机体的正常运作,每一个器官体统正常工作少不了组织细胞的构成,那么触发器就可以比作基本单元组织细胞。

时序逻辑电路的时钟是控制时序逻辑电路状态转换的“发动机”,没有它时序逻辑电路就不能正常工作。

因为时序逻辑电路主要是利用触发器存储电路的状态,而触发器状态变换需要时钟的上升或下降沿,由此可见时钟在时序电路中的核心作用。

最后简单说一下体会吧,归结起来就是多实践、多思考、多问。实践出真知,看100遍别人的方案不如自己去实践一下。实践的动力一方面来自兴趣,一方面来自压力。有需求会容易形成压力,也就是说最好能在实际的项目开发中锻炼,而不是为了学习而学习。

FPGA入门简单精通难。要想入门,买一块开发板跟着例程走一遍,其实打好了坚实的基础后面才能一马平川。想了解更多关于FPGA知识,可以关注IC修真院哦!