山东大学软件学院计组课设2021整机实验(补码加法+溢出跳转+原码一位乘)

本文目录

-

- 前言

-

-

- 致读者

- 写作目的

-

- 一、实验要求

-

-

- 1.1 基本要求

- 1.2 扩展要求(一)

- 1.3 扩展要求(二)

- 1.4 其它扩展

-

- 二、概念剖析

-

-

- 2.1

-

- 三、思路设计

- 四、电路图

- 五、问题与解决

-

-

- 5.1 总线输出接灯,程序运行中,灯没有亮

- 5.2 JP不能跳转回00H

- 5.3 QJP微操作执行后,总是会顺序多走一步微操作,再进行跳转

-

- 六、收获感悟

- 七、项目资源

- 后话

前言

致读者

学子苦课设久矣——笔者在写下这句话时,叹息连连。

因为基础差,加上之前实验划水,初逢整机实验时那真是一脸懵逼,一筹莫展:做了3次实验,电路图都连不上一根线。概念、原理、要求都没有弄清的情况下冥思苦想,让我走了许多弯路…

幸好在弯路上,CSDN上校友的博客,同学的指导给了我启发,实验也渐渐有了进展。

现在,我正把路上的见闻整理成文字图表,希望能够给你哪怕一点点帮助,就像我当初从别人那里获得帮助一样。

疑义相与析,欢迎留言或私信探讨,Any problem will be OK!(๑•̀ㅂ•́)و✧

写作目的

- 以写作输出厘清思路,查缺补漏

- 记录自己的成果与收获

- 帮助苦于课设的你早日征服它

(陆续填坑ing…)

一、实验要求

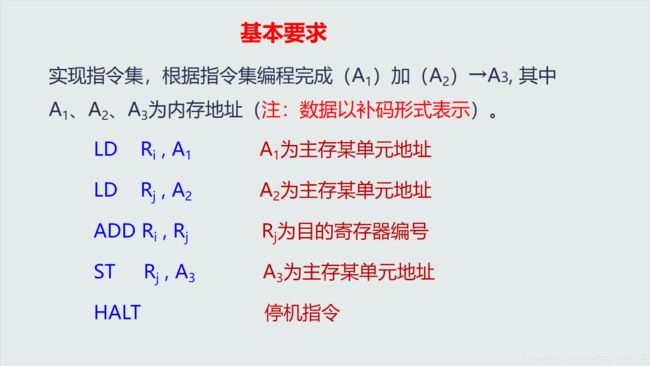

1.1 基本要求

- LOAD取数指令采用双字长、直接寻址

- STORE指令采用双字长、寄存器间接寻址方式

- 取指微程序入口固定为控存的00H

- MDR:一端接内存数据线,另一端接内部数据线,实现MDR与内存数据的隔离

- 在保存运算结果的同时,也要保存结果的状态(C、V、N、Z)

C:进位, V:溢出, N:结果为负, Z:结果为零

今年,我们老师建议使用典型总线结构(与之相反的是非典型总线结构,即以ALU为中心)

| 典型总线结构 |

|---|

| 非典型总线结构 |

|---|

同时还要求通用寄存器需要封装成一个寄存器组,统一管理。

这一部分建议大家尽早明确各自老师要求,以实际为准!!!

1.2 扩展要求(一)

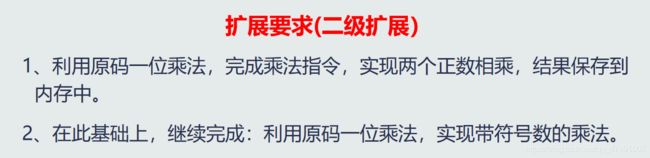

1.3 扩展要求(二)

1.4 其它扩展

二、概念剖析

2.1

三、思路设计

四、电路图

五、问题与解决

5.1 总线输出接灯,程序运行中,灯没有亮

总线上的灯不亮,说明数据没有到总线。

造成这个问题有很多很多的原因,比如RAM压根没有读出数据、数据没有进入寄存器、寄存器的三态门没有打开、某元件本来就有问题…(太多了,根本例举不完)

Debug方法:

一定要多接指示灯!一定要多接指示灯!!一定要多接指示灯!!!

怀疑某个地方有问题,就在那里的输入端/输出端/两端都接上指示灯,观察运行时对应灯泡的变化。

怀疑某个元件本身就无法完成自身功能,就应该单独把它拿出来,输出接灯,手动给它输入和脉冲,观察是否正常。

Example:

我的项目中,取LOAD指令的取指周期中,执行MDR->BUS->IR时,总线灯不亮(我的LOAD指令二进制是0001 0001)

分析:

正常情况下,现在总线上的数据就是LOAD指令,总线灯应该就是0001 0001,但总线灯是0000 0000

于是我首先怀疑是MDR的问题,具体包括以下可能:

- MDR没有存入数据,所以无输出

- MDR有数据,但是与BUS间的三态门没有打开

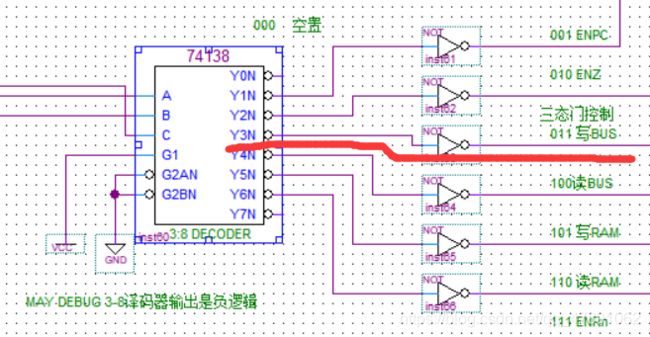

所以我在MDR与三态门之间8条线都接上一个指示灯(如下图)

再次测试MDR->BUS->IR指令,

结果灯为0001 0001!

这说明 MDR有数据,但是与BUS间的三态门没有打开。

于是我沿着线找到了控制这个三态门的3-8译码器的Y3N输出端。

此时,我认为我对3-8译码器的控制逻辑是没有错误的,肯定是3-8译码器元件自身有问题,所以就把它取出来单独测试:

所有输入端绑定开关,所有输出端绑定灯泡

结果都是正常的(比如输入001,结果为0000 0001),证明3-8译码器自身没有问题。

到这里,就不得不怀疑是我对3-8的控制逻辑有问题。

经过检查,发现3-8译码器的输入端弄反了:本来应该是ABC从低到高接,但是我按从高到低接了(笑哭)

最后,我把A和C所接的输入端交换了一下,问题终于解决

5.2 JP不能跳转回00H

我的电路图中,让μPC之前通过二选一选择器来选择QJP与JP跳转方式。

当选择BY为1时,将B0~B7传入μPC,而 B7 ~ B0依次接的是μIR23~μIR16。

经过检查,发现我设计的JP微指令中μIR23~μIR16并不为全零,自然无法跳转回00H

5.3 QJP微操作执行后,总是会顺序多走一步微操作,再进行跳转

时序问题