Verilog语言快速入门(二) -组合、时序

组合逻辑电路FPGA实现

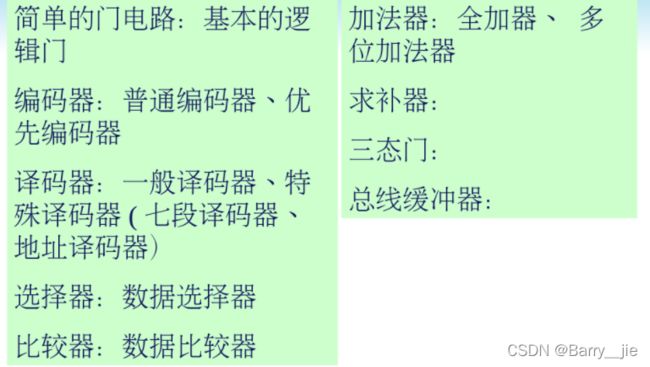

一、简单门电路可实现

1)2输入逻辑门

设计

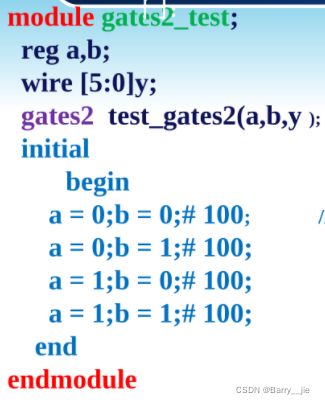

测试

引脚约束

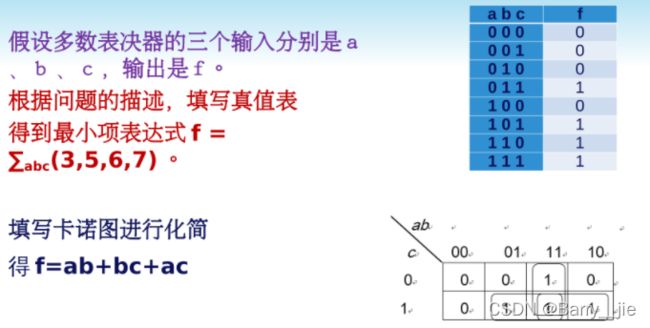

2)三人表决器

题目:假设有三个举重裁判,举重选手完成比赛后,当有多数裁判认定成功,则成功;否则失败。请设计此举重裁决电路。

这个举重裁决电路实际上就是一个三输入的多数表决器。

设计

module v_dsbjq

(

input a,

input b,

input c,

output f

);

assign f=a&b|a&c|b&c; // f=ab+ac+bc

endmodule

测试

添加约束

## Switches

set_property PACKAGE_PIN R1 [get_ports a]

set_property IOSTANDARD LVCMOS33 [get_ports a]

set_property PACKAGE_PIN N4 [get_ports b]

set_property IOSTANDARD LVCMos33 [get_ports b]

set_property PACKAGE_PIN M4 [get_ports c]

set_property 1OSTANDARD LVCMos33 [get_ports c]

##led

set_property PACKAGE_PIN k2 [get_ports f]

set_property IOSTANDARD LVCMOS33 [get_ports f]

3)四选一数据选择器

分别用assign语句和always语句设计四选一数据选择器,并编写test bench程序,基于VIVADO完成四选一数据选择器实验。

待续。。。

二、选择器、编码器、译码器

1)2选1多路选择器(1位)

设计

assing语句

module mux21b(

input wire a,

input wire b,

input wire s,

output reg y

);

assign y =s ? b : a;

endmodule

always语句

module mux21c (

input wire a,

input wire b,

input wire s,

output reg y

);

always @ (a,b,s) //或者always @(*)

if (s == 0)

y= a;

else

y = b;

endmodule

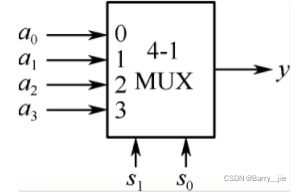

2)4选1多路选择器(1位)

module mux41b (

input wire [3:0] a,

input wire [1:0] s,

output reg y

);

always @(*)

case (s)

0:y = a[0];

1:y = a[1];

2:y = a[2]l;

3: y = a[3];

default: y = a[0];

endcase

endmodule

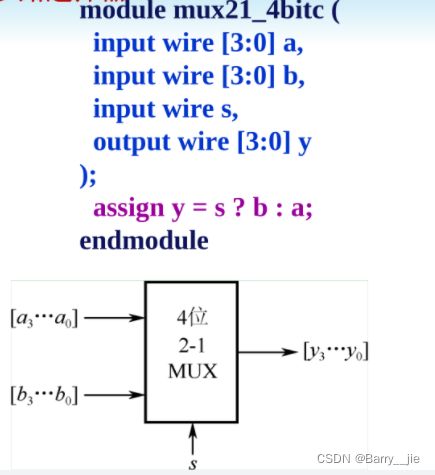

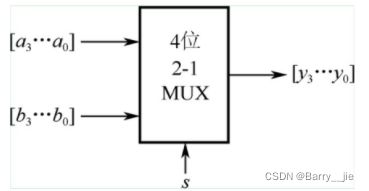

3)2选1多路选择器(4位)

使用 if 语句完成,改一下数据位宽就行

使用条件运算符 写法上换了一下而已

4)2选1多路选择器(任意位)

使用参数(Parameter)实现通用的任意位数的2选1多路选择器

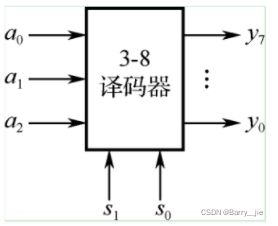

5)3-8译码器

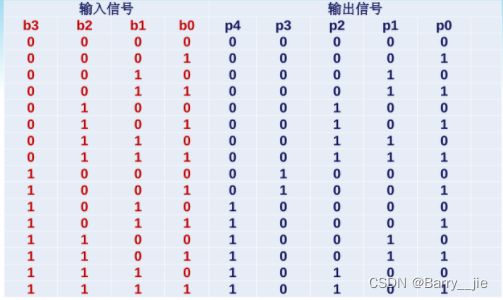

6)4位二进制-BCD码转换器

module binbcd4 (

input wire [3:0] b,

output wire [4:0] p

);

assign p[4] = b[3]&b[2] | b[3]&b[1];

assign p[3] = b[3]&~b[2]&~b[1];

assign p[2] =~b[3]&b[2] | b[2]&b[1];

assign p[1] = b[3]&b[2]&~b[1] | ~b[3]&b[1];

assign p[0] = b[0l;

endmodule

也可以用case语句,抄一遍真值表而已

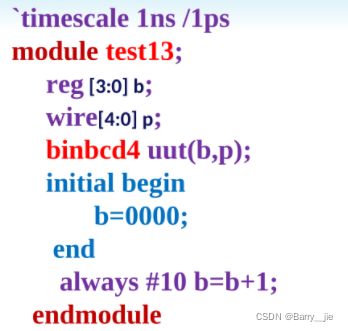

测试

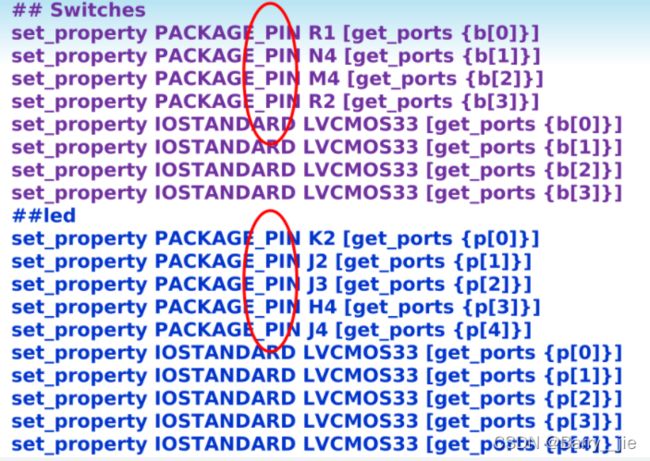

约束文件

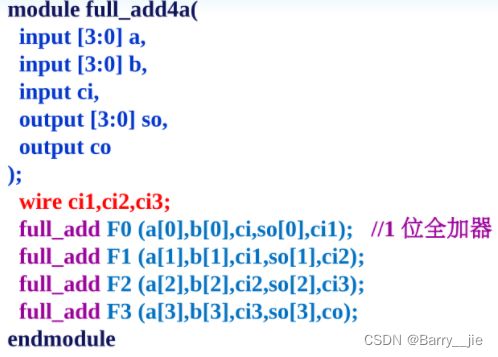

7)加法器

1位

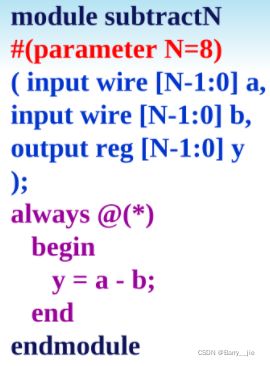

8)N位减法器

9)编码器

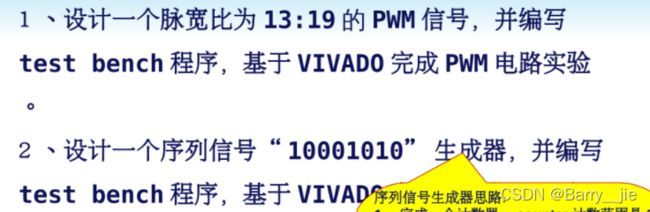

设计四人智力抢答器,并编写test bench程序,基于VIVADO完成四人智力抢答器实验。

待续。。。

时序电路FPGA实现

触发器、寄存器、计数器、分频器

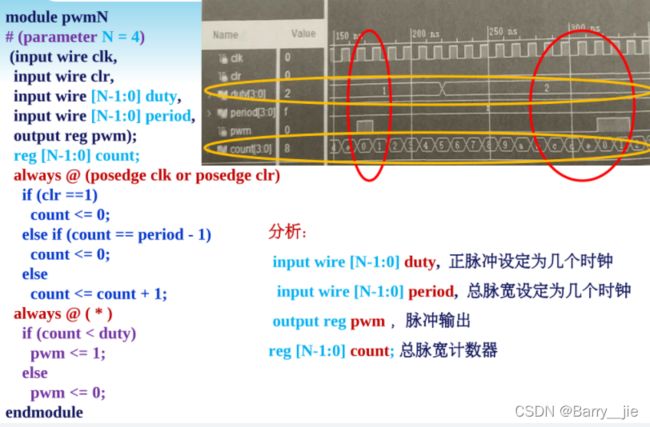

PWM信号发生器

时钟沿在Verilog中的描述方法

边沿敏感:

- 信号上升沿到来 (posedge信号名)

- 信号下降沿到来 (negedge信号名)

复位控制描述:

复位信号可以分为同步复位和异步复位两种。

- 同步复位:就是当复位信号有效且在给定的时钟边沿到来时,系统才被复位;

- 异步复位:是当复位信号有效时,系统就被复位,不用等待时钟边沿信号。

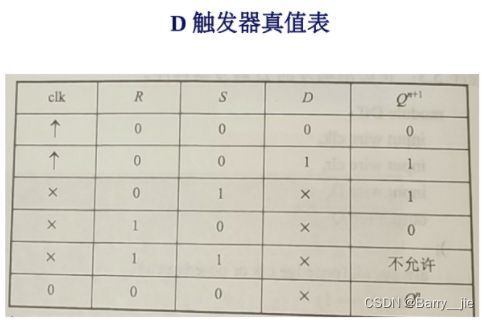

1)触发器

触发器根据触发边沿﹑复位﹑和预置的方式以及输出端多少的不同也可以有多种不同形式的触发器。

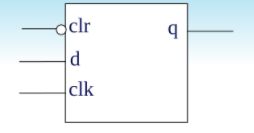

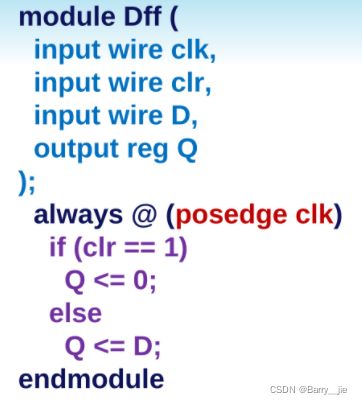

正边沿触发的D触发器---异步复位

module Dff(

input wire clk,

input wire clr,

input wire D,

output reg Q

);

always @(posedge clk or posedge clr)

if (clr == 1)

Q<= 0;

else

Q<= D;

endmodule

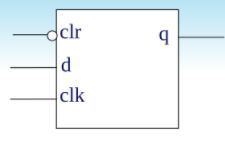

带异步复位和置位端的D触发器

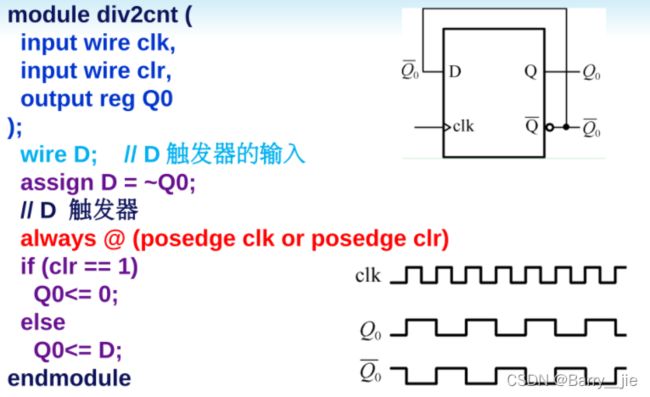

2)分频电路

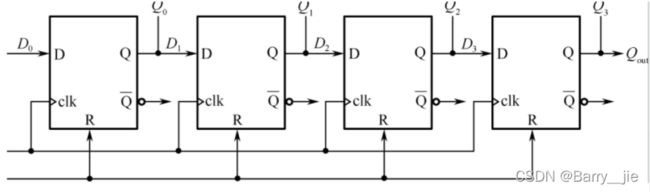

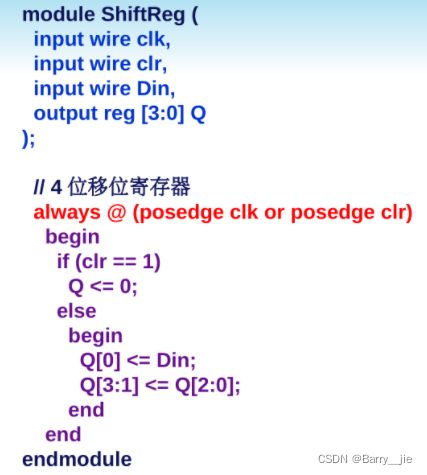

3)4位右移寄存器

4)计数器

计数器分同步计数器和异步计数器两种,如果按工作原理和使用情况来分就更多了。

- 同步计数器,就是在时钟脉冲(计数脉冲)的控制下构成计数器的各触发状态同时发生变化的计数器。

- 异步计数器,又称行波计数器,它的下一位计数器的输出作为上一位计数器的时钟信号,这一级一级串行连接趄来就构成了一个异步计数器。

计数器是一个典型的时序电路,分析计数器就能更好地了解时序电路的特性。

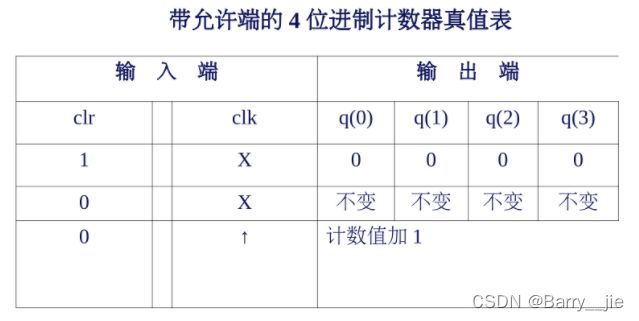

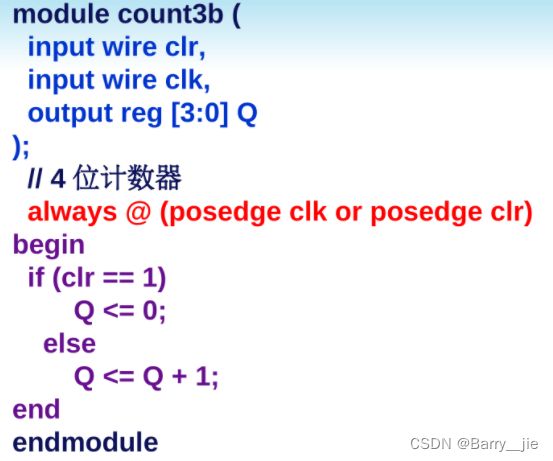

4位二进制加法计数器

该计数器有4个触发器构成, clr输入端用于清零, clk 为时钟脉冲(计数脉冲)输入端, q为计数器的4位二进制数值输出端。

行为描述即可

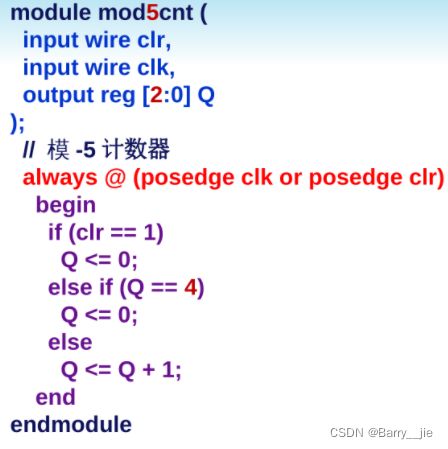

5进制计数器

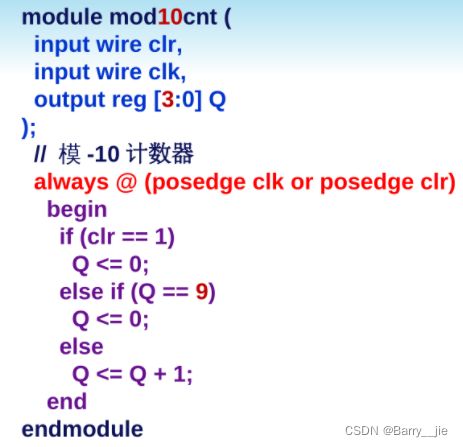

10进制计数器

60进制计数器

待续。。。

计数器的应用

在一些数字系统中使用的最多的时序电路就是计数器。

计数器不仅能用于对时钟脉冲计数,还可以用于分频﹑定时﹑产生节拍脉冲和脉冲序列等。

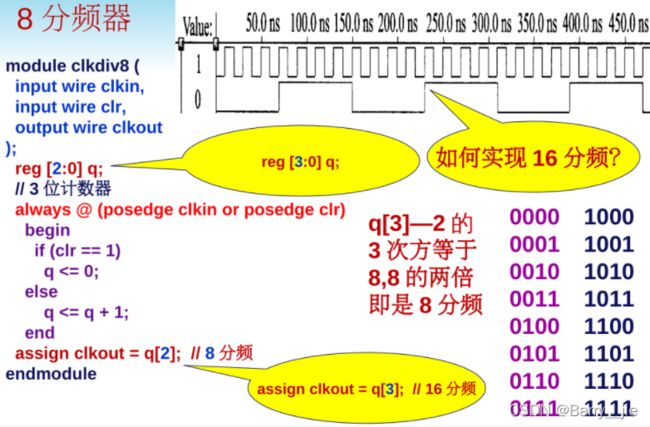

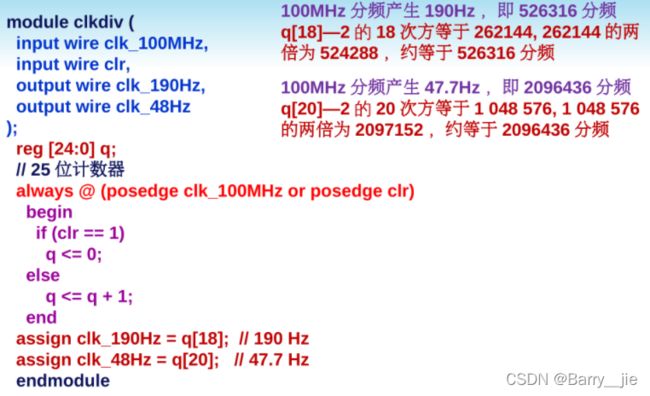

5)分频器

8分频 16分频

产生一个频率为2kHz的 PWM信号

待续。。