《Verilog HDL与FPGA数字系统设计》书籍试读体验

文章目录

-

-

- 前言

- 第一部分:数字系统基础

- 第二部分:数字系统设计实践

- 第三部分:可编程片上系统

- 总结

-

前言

最近参加一个面包板社区的图书试读活动:《Verilog HDL与FPGA数字系统设计》书籍试读,有幸从众多申请者中得到这次试用机会,非常感谢面包板社区和机械工业出版社的支持。

收到这本书的过程,中间还有一些小插曲。

这本书是由面包板社区官方通过京东快递从深圳发出,为到付方式。6月10日,在手机上看到有一个京东快递正在派送,那天正好周末,在家收到了一个京东快递,是一个文件袋,很薄,感觉不像是图书,像是几张纸,打开一看果然不是,是几张发往西安的发票。

我赶紧联系了面包板社区的小编,幸好之前加过小编的微信,很快就联系上了,了解到原来是深圳那边的京东小哥搞错了,将这两个快递单贴错了,导致我的图书发往了西安。之后深圳的快递小哥联系了我,让我把这个寄错的发票发到西安的客户那边,快递费由他来出,而我的图书也会在周一从西安发出,一切都进行的很顺利,终于在6月15日收到了这本书!

我们一般在选择技术图书时,会关注图书的作者是否有一定的影响力,比如行业内资深的工程师,或者是知名大学的老师,这样的书籍才有一定的含金量。

本次申请到的这本书:《Verilog HDL与FPGA数字系统设计》,是由华中科技大学的罗杰教授主编,罗杰老师不仅是华中科技大学电子信息与通信工程学院的教授,还是全国大学生电子设计竞赛湖北赛区的专家组成员。

从书中的前言部分得知,这本书自2015年出版以来,得到了广大读者的支持,已经重印了9次,本次拿到的是第2版本,相比与第1版本,更新了如下内容:

- 新增了SoPC的软硬件开发

- 改写了示例代码,所有代码均经过DE1/DE2开发平台下载验证。

- 软件版本升级到Quartus Prime 18.1和Modelsim 10.5b。

这本书收到有一段时间了,最近几天利用下班后的时间,粗略看了文章内容。这本书主要是介绍数字电路和可编程器件基础、Verilog语法、以及基于Intel FPGA的实战项目。、

说起Intel,几年前还是叫Altera,在大学期间EDA课程用过几次他家的FPGA芯片,当时学习的是VHDL,使用的还是Quartus II 9.0版本,那时对FPGA完全没有概念,只记得实验室有个很大的实验箱,资源很丰富,只可惜在学校时没有好好利用起来。

现在大学毕业也有几年了,因为工作需要自学了FPGA,工作涉及逻辑和片上处理器编程,常用的是Xilinx的Spartan-6和Artix-7平台。

早就听说Altera也有自己的软核处理器NiosII,正好这本书有相关介绍,所以这次试读的重点是Altera NiosII软核处理器的使用。

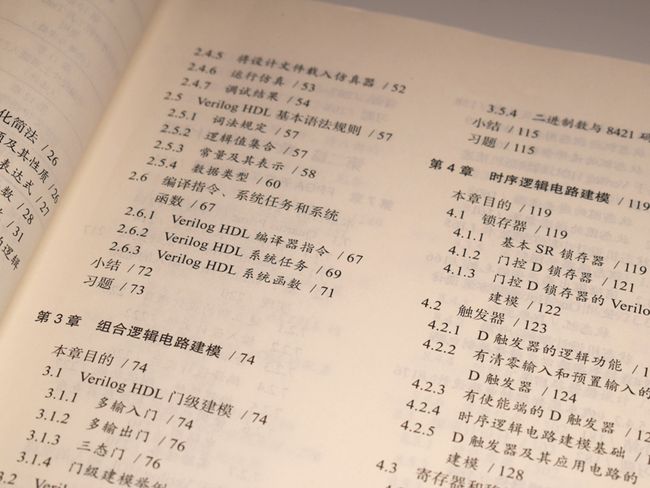

这本书共分为三大部分:数字系统基础、数字系统设计实践和可编程片上系统,三部分的内容占比大概是3:2:1,也可以认为是理论知识、实践项目和软核处理器应用的比例。

图书背面的赠阅尊享标记,表示这是一本非商业售卖的书籍。

第一部分:数字系统基础

这部分主要介绍数字电路的基础知识,不同进制的概念以及不同进制相互转换的方法,最常用的三种进制表示方法:**二进制、十进制、和十六进制。**以及常用的几种编码方式:8421码、余3码、格雷码、奇偶校验码、ASCII字符编码。

其他还有数字电路简介,重点介绍了芯片或电路的常用技术参数,比如Vcc/Vdd的含义,DC参数VOH,VOL,VIH,VIL,IOH,IOL,VNH,VNL等等,这些都是非常重要的概念,有些工作了几年的工程师可能都不了解这些参数的定义,在阅读一些FPGA芯片或其他外围芯片的Datasheet时,这些参数都会明确标注,在设计电路或者是遇到问题查找原因时非常重要。

理论的数字电平0=GND,1=VCC,但是实际电路中可能是高于80%的VCC认为是高电平,低于20%的VCC认为是低电平。还有一些时序相关的参数,比如信号的上升和下降时间Tr/Tf,实际电路中电平的变化需要一定的时间,这个时间就可以大致认为是这颗芯片的最大工作频率,其他还有信号的建立保持时间Tsu/Thd,也是设计芯片的驱动时序逻辑时要重点关注的参数。

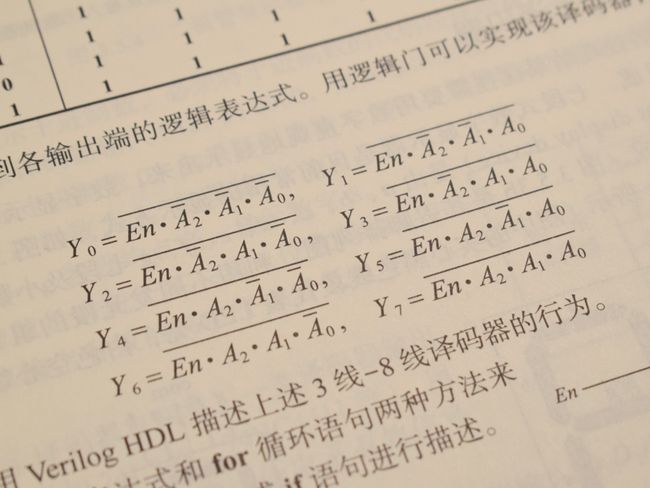

后续还有逻辑代数的计算,有的书籍会称为布尔代数,都是一个概念,逻辑代数的化简方法,摩根定理,卡诺图等等。

现有的一些FPGA集成开发环境中都已经具备了逻辑代数自动化简的功能,比如如果我们写了一个非常复杂的组合逻辑表达式,综合出来的电路就是已经化简之后的,所以这部分介绍的化简方法在实际项目中用的不是很多。

之后就是大多数书籍中都有的Verilog语法规则介绍,包括HDL的起源和发展,Verilog模块的基本结构,Verilog的设计、仿真流程,可综合的语句以及不可综合的系统任务、系统函数,以及实用的ModelSim软件的使用方法。

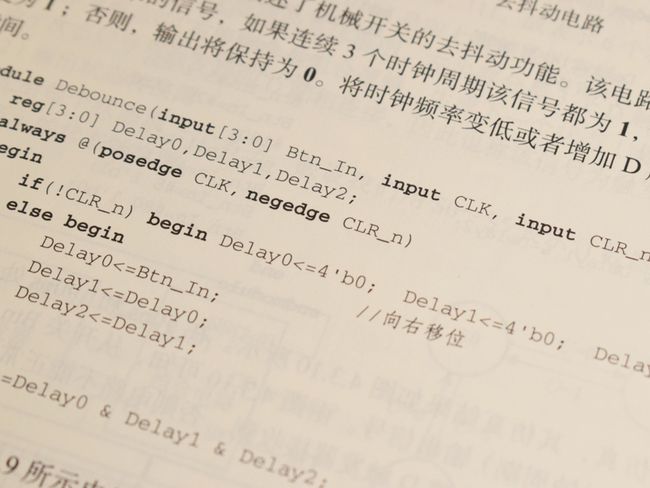

然后就是分层次的设计方法:组合逻辑和时序逻辑的建模思路,如何基于一个现有需求,设计出符合要求的电路,中间还穿插了Verilog的常用语句,如for、repeat、while、forever、generate,模块的例化方式,function和task的使用,这些语句非常有利于我们的编码实现和仿真,可以精简代码,模块化设计,增强可读性。

时序逻辑部分介绍了常用模块的设计,比如寄存器、不同模式的计数器、移位寄存器等,可以说所有的复杂逻辑,都是基于这几种简单逻辑实现的。

本部分还介绍了一种设计模式:有限状态机。无论是FPGA开发,还是其他控制器,如MCU等,这种设计模式都很常用而且实用。

状态机可分为4大要素:现态、条件、动作和次态,毫不夸张的说,所有的时序问题都可以基于有限状态机的设计模式来实现。

这一章节介绍了状态机的两种类型:Mealy型和Moore型。状态机的Verilog描述方法:三段式、两段式和一段式,以及状态机中对状态的三种编码方式:自然二进制、格雷码(Gray)和独热码(One-Hot),并分析了三种编码方式的特点,后续又跟了状态机的两个实战项目:十字路口交通灯和汽车信号灯控制逻辑的设计。

!(https://wcc-blog.oss-cn-beijing.aliyuncs.com/img/220711/2实战2.JPG)

本部分的最后介绍了FPGA的发展历史,从PLD、PLA到PAL、GAL,再到现在常用的CPLD和FPGA,这部分也很重要,因为有很多初学者学完FPGA之后,对于FPGA是什么、它有什么特点都不知道。

不过按照FPGA的学习路线,这部分内容应该放在本书的开头几章,不知道为何放在了后面的章节。

最后还介绍了Intel FPGA产品线高端(Agilex和Stratix10)、中端(Arriva)和低端(Cyclone)三大系列产品的特点,以及对本书中所使用的FPGA开发板:友晶科技的DE2-115和DE1-SOC两款板子进行了简单介绍,让读者对所配套开发板有个基本了解。

近几年来国产FPGA也有一定的进步,文中提到了几家国产FPGA厂商:复旦微、高云、紫光同创、安路等,这一点值得点赞!

第二部分:数字系统设计实践

第二部分是FPGA的实战项目,按照FPGA的学习路线,学习完Verilog基本语法之后就可以进行FPGA实战练习了,就是基于实际的FPGA开发板,使用所学的Verilog语言,设计一些简单项目。

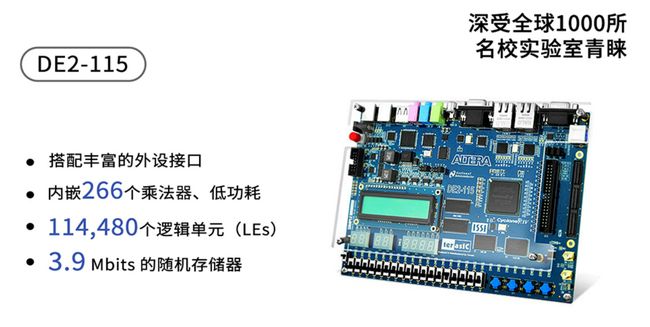

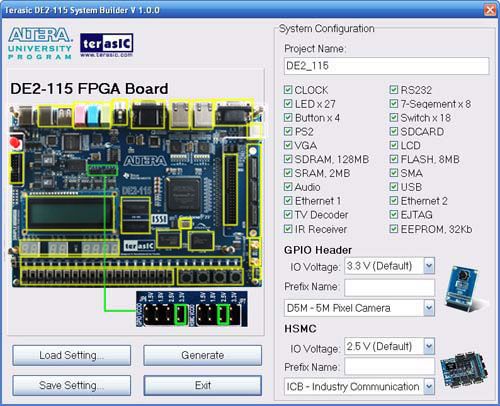

本部分以Intel FPGA平台为例,使用Quartus Prime开发环境,配套的开发板是友晶科技的DE2-115开发板,这也是一款全球高校实验室广泛使用的开发板。

当然价格也是非常的美丽:6860RMB,学术价格:3690RMB。

找了一些关于这款开发板的资料:基于EP4CE115芯片,板载USB-Blaster下载器,128MB SDRAM,2MB SRAM,8MB Flash,32Kb EEPROM,音频编解码器,2路千兆网口,USB芯片,VGA接口,DB9串口,PS/2鼠标键盘接口,红外接收模块等等。

板载资源非常丰富,用于练习FPGA开发设计足够用了,如果不够的话,还可以通过GPIO连接扩展模块,如LCD、摄像头等。

我还注意到友晶科技还为这块板子开发了测试工具Control Panel,和Quartus工程自动生成工具System Builder,非常不错,值得开发板厂商学习借鉴。

Control Panel,可以通过上位机控制板载外设,测试硬件功能。

System Builder,可以根据选择外设的,自动生成Quartus工程。

一提到板子就收不住了,介绍的有点多了。

我们回到书本内容,本书选择的FPGA开发工具是Altera 2018年推出的Quartus Prime 18.1精简版,详细介绍了Quartus Prime软件的安装、设计的输入、管脚分配、布局布线、下载调试等全流程,以及片上逻辑分析仪SignalTap的使用。

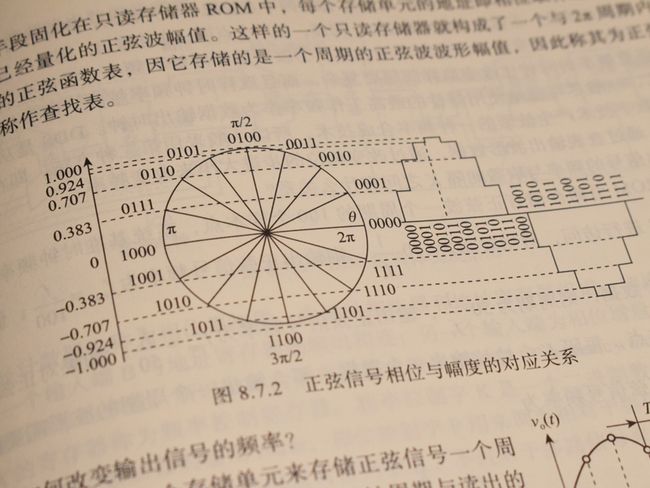

首先介绍了3个比较常用的Altera FPGA IP核的使用:计数器LPM_COUNTER、锁相环ALTPLL和存储器LPM_ROM。

之后就是一些小项目的应用,如分频器、数字时钟、频率计、1602显示、DDS信号发生器、VGA接口等,都是入门FPGA必学的项目,非常锻炼Verilog编码能力和设计、调试能力。

这一部分还单独使用一个章节介绍了Quartus的时序分析工具TimeQuest的使用。静态时序分析是实际项目开发中非常重要的基本功。

设计输入完成后,会先进行功能仿真,功能仿真基于理想环境,所有的寄存器都可以在时钟边沿进行锁存,组合逻辑运算的时间为0,建立和保持时间都默认满足需求,但是实际芯片内部运行的电路却不是理想环境,寄存器与寄存器之间存在连线,所有的时钟信号虽然都连接在一起,但是由于传输延时,并不是同时到达每个寄存器,组合逻辑的计算也需要一定的时间,复杂的组合逻辑运算和简单的组合逻辑运算所用的时间不同的。

目前的FPGA开发工具,在综合、布局布线完成之后,都会基本当前的FPGA芯片和片上资源、用户的应用逻辑和所指定的时序要求,生成一份时序分析报告,来告诉用户哪些路径存在时序违规,哪些寄存器的输入信号不满足建立保持时间要求,哪些组合逻辑耗时过长,可能会输出不理想的结果,当需要进行时序优化时,就需要进行静态时序分析了。当然,一般在设计编码阶段就已经开始考虑静态时序了。

本章小结:介绍了Intel FPGA开发工具Quartus Prime安装、使用方法,以实际项目为例,介绍从项目创建、设计输入、管脚分配、综合布局布线到程序下载调试全流程,并介绍了片上逻辑分析仪SingalTap、时序分析工具TimeQuest的使用。

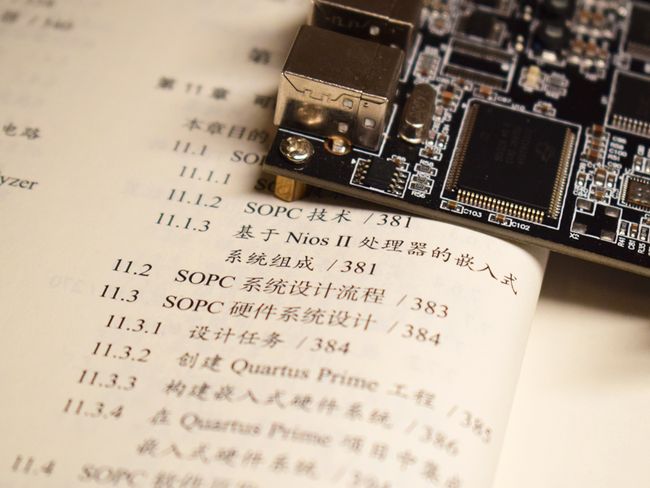

第三部分:可编程片上系统

第三部分是本书第2版本新增的内容,介绍了Altera FPGA软核处理器NiosII的使用,这部分也是我比较感兴趣的,因为我曾经使用过Xilinx(现AMD)FPGA的Microblaze软核和Microsemi(现Microchip)FPGA的ARM Cortex-M3硬核,还没了解过Altera的Nios II处理器。

这一部分以友晶科技的DE1-SoC开发板(也可以用DE2-115)为例,基于5CSEMA5F31C6芯片,这颗芯片有点意思,片上已经集成了ARM Cortex-A9双核处理器,属于硬核处理器,而本书这部分介绍的使用在这颗芯片上运行软核处理器NiosII。

对比Xilinx的软核开发工具:FPGA开发工具ISE、软核搭建工具XPS和软核应用开发工具SDK,Altera也有对应的三大套件:Quartus、Platform Designer(或称Qsys)和Nios II SBT。

和Xilinx的Microblaze一样,NiosII处理器也是32位 RISC处理器,不同于Xilinx的AXI总线,NiosII处理器和外设通过Avalon-MM总线进行通讯。

软核处理器的开发流程和Xilinx基本一致,首先在Quartus Prime建立FPGA工程,然后在Platform Designer中构建嵌入式系统硬件,最后在SBT工具中开发应用程序。

本部分小结:本部分对软核处理器开发介绍的很详细,工具安装使用都有相应的截图说明,应用程序也有完整的代码,文中介绍了几个常用外设的使用:GPIO、外部中断、RTC DS1302驱动等。最后介绍了如何自定义Avalon总线IP组件,详细介绍了Avalon总线规范和7种类型接口。

关于软核和硬核的区别,可以看我之前写的一些文章:

- FPGA硬核和软核处理器的区别

- 带片上处理器的国产FPGA选型

- 手把手教你在FPGA上搭建一个ARM Cortex-M3软核

- 除了ZYNQ还有哪些内嵌ARM硬核的FPGA?

总结

从本书的定位来看,这是一本是面向高等院校电气信息类本、专科生的教材或教学参考书,从课时安排上来看,是理论和实践相结合的。

文章中对于数字电路基础、Verilog语法都很详细,还有几个实战项目用于练习,后面还涉及到静态时序分析这一非常重要的知识点,对于学生入门FPGA是足够用的。

但是也有一些不足之处,比如文章中Verilog代码的风格有2005和2001两种标准,没有进行统一,对于初学者可能会疑惑哪种写法是正确的;对于数字电路基础知识的介绍,缺少原码、反码和补码的概念,而在实际开发中如果涉及到有符号数的使用,需要了解有符号数的存储方式;数据的编码方式实际应用介绍较少,比如格雷码用于状态机状态编码,奇偶校验用于串口通讯的数据校验,ASCII编码用于字符串存储等,如果再增加一些编码方式会扩展读者的知识面,比如归零码、曼彻斯特编码,4B/5B和8B/10B这些;实战项目部分可以增加一些通讯协议的实战应用,比如UART、SPI、I2C等等,这三大协议是电子行业中最常用的三种串行总线,也是很多公司对应届生经常出的面试题目;软核处理器中外设的使用,可能是由于文章篇幅的限制,没有介绍TIMER、UART等这些常用外设的使用。

总的来说,基于本书的定位,作为高校的教材或设计竞赛的参考用书,是一本非常不错的图书,但是用于FPGA从业者用于进阶学习,内容就有些偏基础了。

最后,再次感谢面包板社区和机械工业出版社能提供本次图书试读机会。