10g gtx 光纤通信测试_S03-CH05_UDP 万兆光通信

软件版本:VIVADO2017.4

操作系统:WIN10

硬件平台:MK7160FA

5.1概述

MK7160FA 开发板的4路SFP+光口均与xc7k160T芯片的GTX 串行收发器连接。使用 FFG676 封装的xc7k160t可以支持高达 12.5Gb/s 的传输速率。因此,在MK7160FA 开发板上可以实现万兆光纤以太网传输。

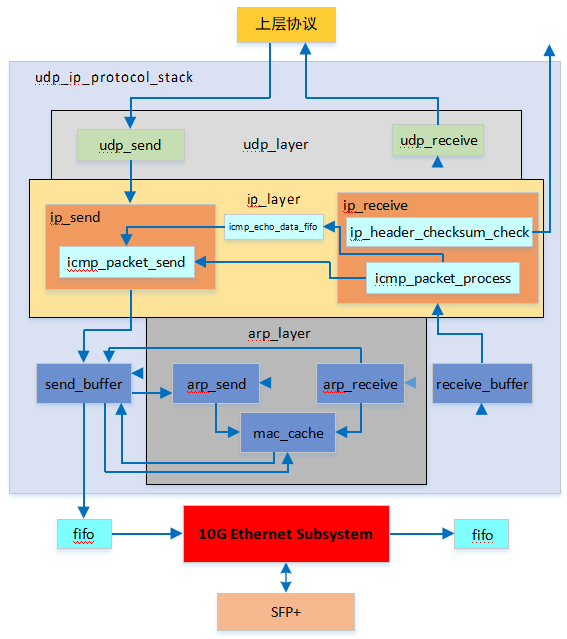

在 MK7160FA 开发板中实现万兆网 UDP 传输的基本逻辑框架如下图所示。FPGA 程序基于米联的新版 UDP IP 协

议栈以及Xilinx 的 IP 核 10G Ethernet Subsystem 而实现。

本文档对应 2 个例程,分别为 udp_ip_10g 和 udp_ip_10g_4ch,分别实现单路和 双路万兆 UDP 光纤传输。

5.2 SFP+接口

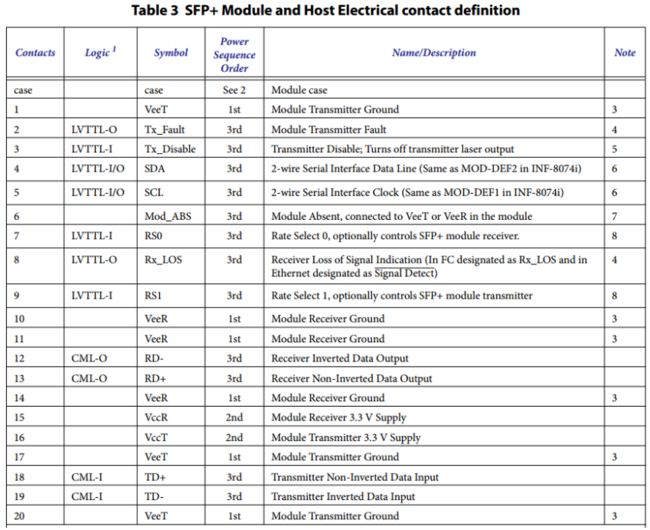

MK7160FA 上有4 个SFP+屏蔽笼。MK7160FA 上有4 个SFP+屏蔽笼。SFP+屏蔽笼可以插入千兆或万兆光模块。SFP+信号定义与SFP 一致,如下图所示。

5.3 IP 设置

将 IP 核 AXI-Stream 的用户数据接口位宽设为 64bit,此时对应用户接口时钟频率为 156.25MHz。如下图所示。

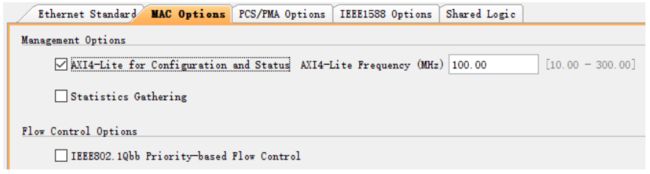

将 AXI-Lite 配置接口时钟频率设置为 100MHz,当然用户也可以自由选择其他的频率。不使用参数统计和优先级流量控制功能。如下图所示。

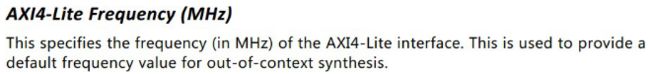

时钟频率的设置仅对 IP 核单独综合有效。如下图。

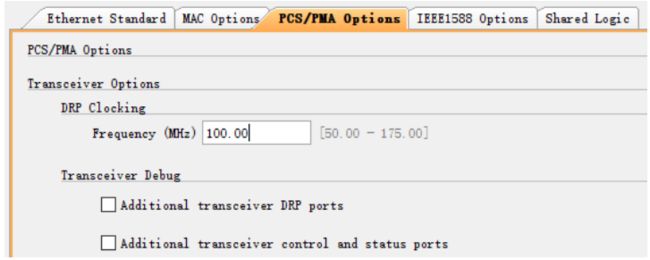

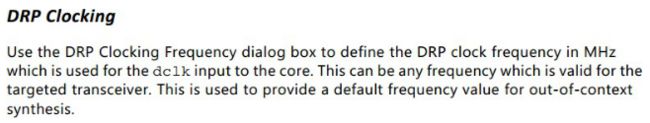

将 GTX 动态重配置端口DRP 的时钟设为 100MHz, Debug 功能不作使用,如下图。

该时钟频率设置也仅对单独综合有效。如下图。

1588 同步功能一般针对某些需要进行网络时间同步的场合,如音视频传输。仅用作数据传输时无需使用。因此

这里不启用 1588 功能。如下图。

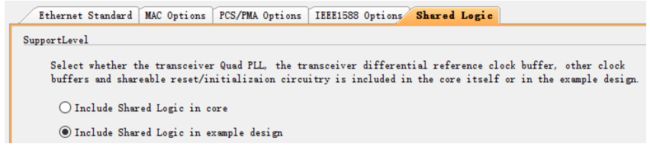

当设计中只包含 1 个此 IP 核时,应当将可共享的逻辑资源和硬件模块包含在 IP 核内部,这样会减少所生成的模块数量,简化设计。如下图所示。

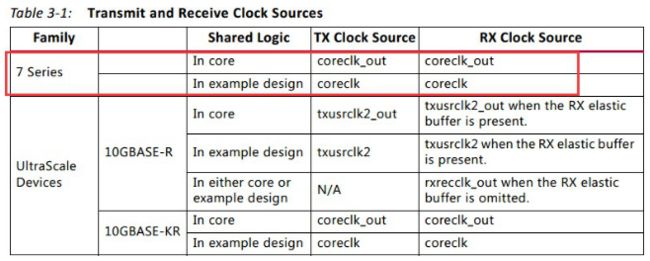

当设计中需要同时使用若干个此 IP 核,且所使用的GTX 均位于同一个GTX BANK 中。此时,只需其中 1 个IP 核内部的共享资源(MMCM、QUADPLL、GTX 参考时钟等)便可以满足所有 IP 核的需求,即选择将共享资源包含在 IP 核内部。其余 IP 核将这些共享资源从其内部剔除即可,即选择将共享资源包含在 example 中。如下图所示。

5.7.4IP 核结构

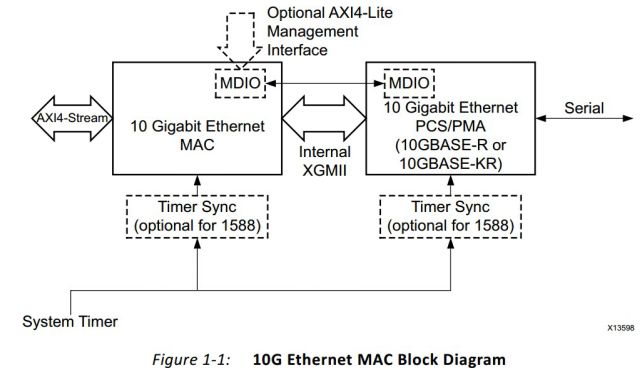

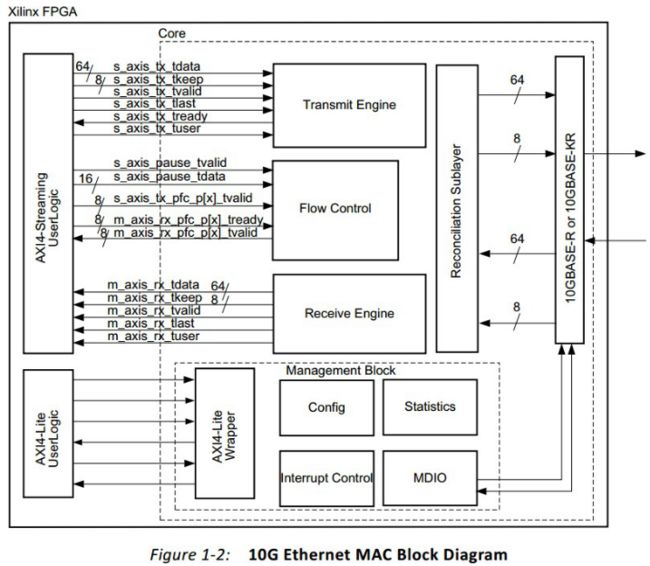

IP 核的结构如下图所示。用户的接收和发送接口均采用了 AXI-Stream 标准。

10 Gigabit Ethernet Subsystem IP 核内部由 10 Gigabit Ethernet MAC 和 10 Gigabit Ethernet PCS/PMA 两个 IP 核所组成,两个 IP 之间通过XGMII 和 MDIO 接口连接。如下图所示。

10 Gigabit Ethernet Subsystem IP 核内部由 10 Gigabit Ethernet MAC 和 10 Gigabit Ethernet PCS/PMA 两个 IP 核所组成,两个 IP 之间通过XGMII 和 MDIO 接口连接。如下图所示。

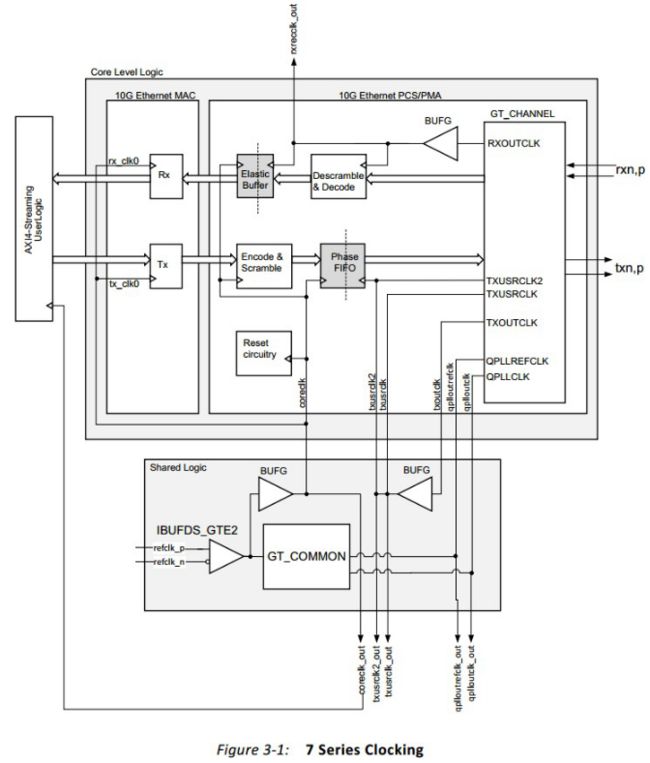

5.7.4.1时钟网络

IP 核内部时钟网络结构如下图所示。

5.4.2接收和发送接口时钟6.4.2

从上图中可以看到,GTX 的参考时钟输入后经过BUFG 后直接作为AXI-Stream 接收和发送接口时钟输出,如下图所示。当 AXI-Stream 接口为 64bit 数据位宽时,GTX 参考时钟频率为 156.25M,当 AXI-Stream 接口为 32bit 数据位宽时,GTX 参考时钟频率为 312.5M。

参考时钟采用 156.25M 时,数据率为:156.25M×8byte×8bit=10000Mbps,由于 PCS 采用了 64b/66b 编码方式。因此,此时 GTX 的传输速率为:10000Mbps×66/64 =10.3125Gbps。

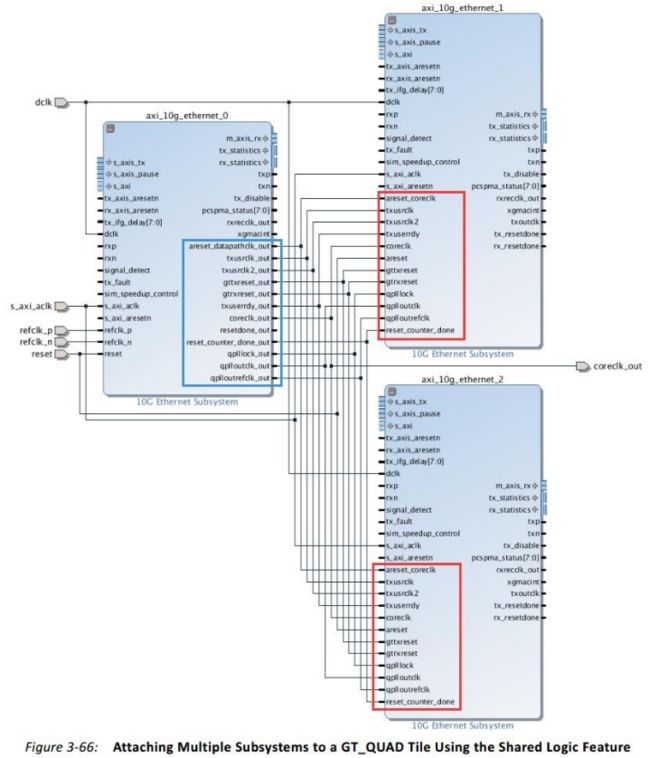

5.4.3多IP 资源共享

例如,在设计中同时使用 3 个 IP 核时,3 个 IP 核之间的共享资源信号连接如下图所示。

5.4.4用户接口

5.4.4.1AXI-Stream接口

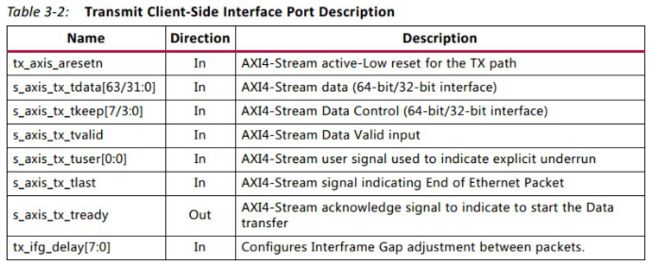

AXI-Stream 发送接口

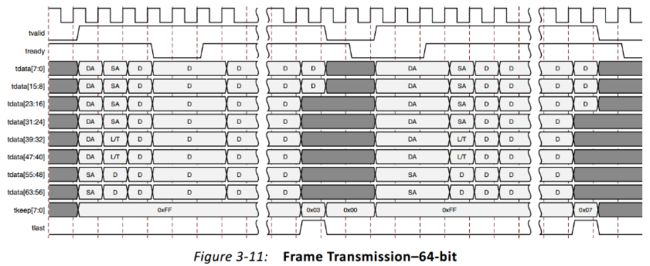

AXI-Stream 发送接口信号如下图所示。用户通过该接口,向 IP 核传输所需要发送的以太网数据包。其中,

tx_ifg_delay 用于设置发送间隔,一般都默认采用最小间隔,将 tx_ifg_delay 置为 0 即可。

AXI-Stream 发送接口时序如下图所示。

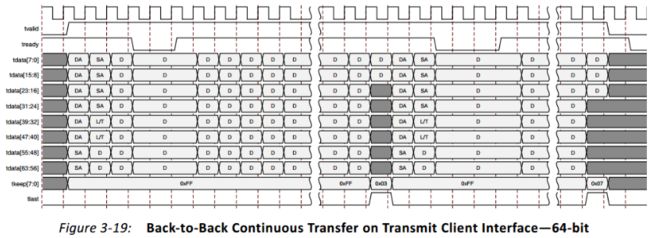

背靠背连续发送

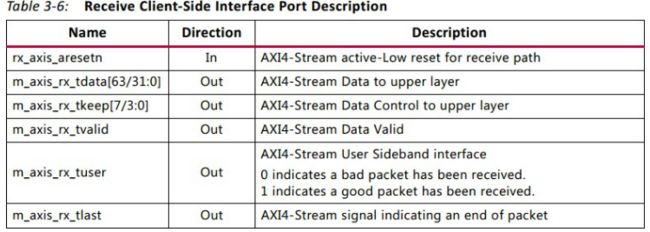

AXI-Stream 接收接口

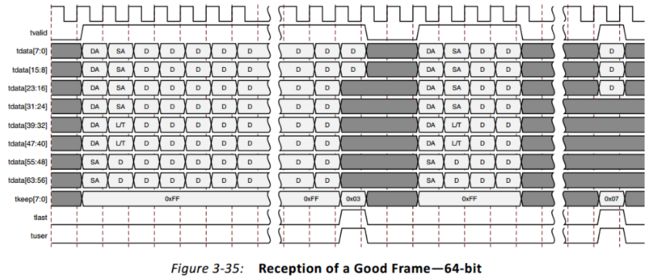

AXI-Stream 接收接口信号如下图所示。用户通过该接口接收从 IP 核输出的以太网数据包。需要注意的是,接收接口没有使用 AXI-Stream 标准中的 tready 信号。这代表接收端需要具备持续接收数据的能力,防止出现数据来不及接收而产生溢出。

AXI-Stream 接收接口时序如下图所示。

5.4.4.2pcspma_status

pcspma_status 端口用户反应 IP 核内部 PCS PMA 部分的运行状态。由于 GTX 只支持 10GBASE-R,因此pcspma_status 只有 bit0 有效。如下图所示。

5.4.4.3sim_speed_up

sim_speed_up 引脚只有在仿真时才需要用到这个信号,用于加快仿真速度。编译时将其置为 0 或 1 即可。

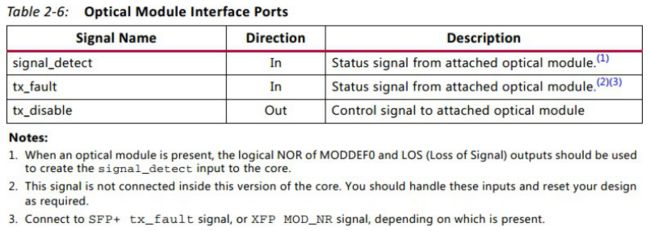

5.4.4.3光模块相关信号

IP 与光模块之间的连接信号及接法如下图所示。

5.4.4.4流量控制信号

非高带宽、大负荷传输情况下,一般不需要使用流量控制功能。因此,不需要发送暂停帧,将以下两个信号均置为 0 即

可。

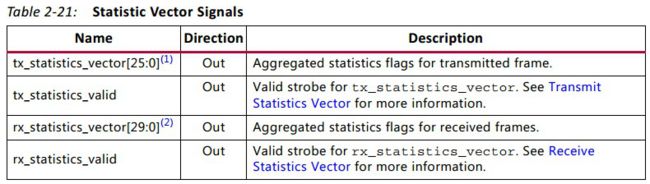

5.4.4.5计信号

下图中的信号,用于统计并输出当前发送完毕或者接收完毕的帧对应的各种类型的信息。除了调试用之外,一般无需使用。

信号时序如下图所示。

5.4.4.6e接口

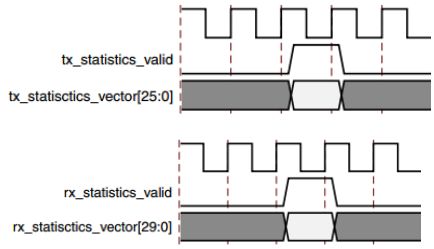

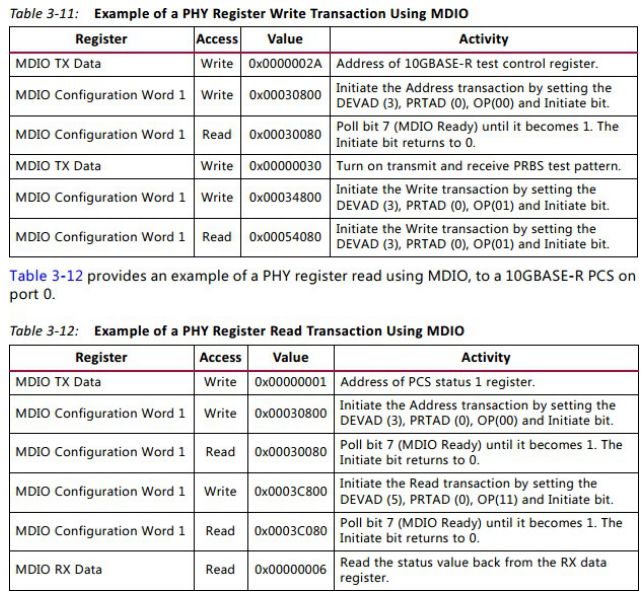

AXI-Lite 接口主要用于配置和读取 IP 核内部的寄存器。AXI-Lite 接口不仅可以配置 IP 核 MAC 部分的寄存器, 还可以直接通过 MAC 部分的 MDIO 接口配置PCS/PMA 部分的寄存器,如下图所示。

通过AXI-Lite 接口实现 MDIO 接口读写PCS/PMA 部分的寄存器的例子如下所示。

5.4.5用注意点

5.4.5.1数据发送长度

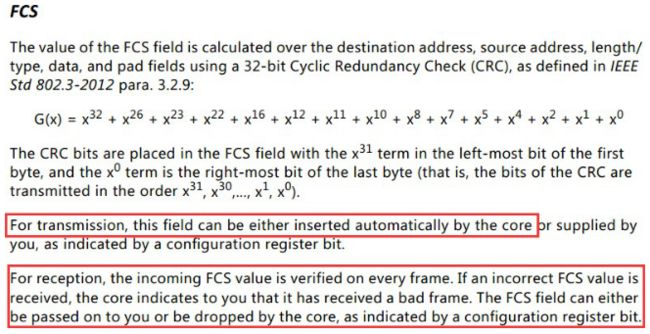

IP 核在默认情况下,发送帧长度小于 64 字节时,IP 核会在帧末尾自动补 0,补足至 64 字节,并且再帧末尾自动插入 4 字节 CRC。接收时,IP 核自动去除末尾 4 字节CRC,但对于长度小于 64 字节的帧末尾补的 0 不会被去掉, 仍会通过接收接口输出。因此,可以发送的数据长度在 14~1514(含 14 字节 MAC 帧头)字节之间。

IP 使用文档中对此有如下描述。

5.4.5.2用FIFO与IP核AXI-Stream接口连接

在设计中,可以使用 AXI-Stream DATA FIFO 与 IP 核的 AXI-Stream 接口,作为数据的缓冲。使用 FIFO 时有以下几个注意点。对此,IP 核使用文档中有如下描述:

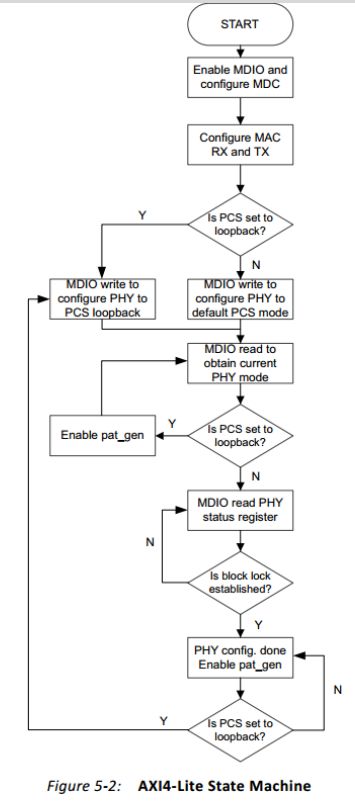

5.4.5.3XI-Lite接口配置策略

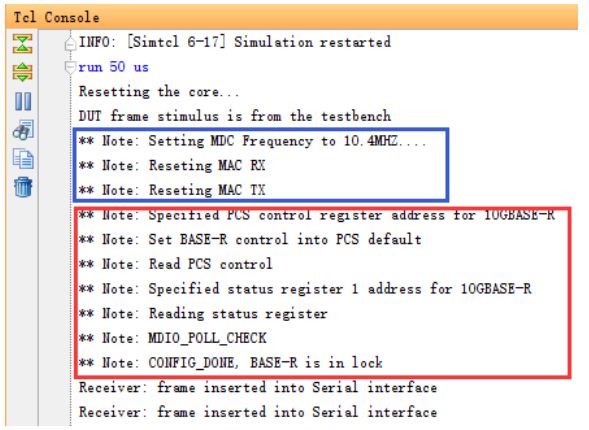

仿真 ip 核自带的 example,可以观察到 example 中通过AXI-Lite 配置 IP 核MAC 部分的过程,如图蓝色方框内所示。以及通过 AXI-Lite 经过 MAC 部分的内部MDIO 接口配置访问PCS PMA 部分的寄存器,如图红色方框所示。具体寄存器定义参考PG157。

Example 通过AXI-Lite 配置 IP 核的流程如下图所示。在例程中,直接采用这部分的代码。

5.5例程设计

例程的原理如下图所示。实现了一个 UDP 收发环路,即电脑通过网络调试助手向开发板发送 udp 包,开发板接收到 udp 包经过 fifo 缓存后重新发回电脑,由此验证数据收发的正确性。

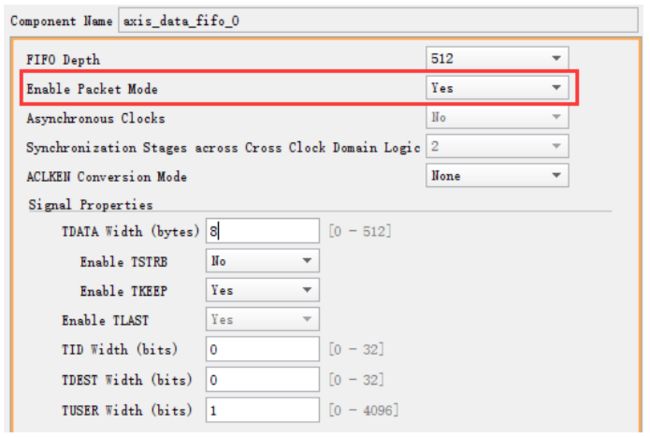

UDP IP 协议栈与万兆 IP 核之间通过 2 个 AXI-Stream DATA FIFO 进行连接。两个 FIFO 的设置如下图所示,均使能Packet mode 功能。

Packet mode 是指 FIFO 持续缓存 AXI-Stream 接口输入的数据直至输入端 tlast 信号拉高,即存满一个完整的数据包时,才开始在 AXI-Stream 输出端口向外输出数据。需要注意的是,启用 Packet mode 时,FIFO 必须工作于同步模式。

对于发送路径,这样做是为了防止 FIFO 被 IP 核读空。对于接收路径,是由于米联的UDP IP 协议栈要求 1 个数据包的 tvalid 信号在数据包持续期间必须恒为 1。

由于在 Verilog 中定义变量,对 tdata 和 tkeep 进行大小端的字节序转换。

5.6例程测试

万兆网的测试需要使用万兆网卡,用户可以购买万兆网卡配合台式电脑进行测试。

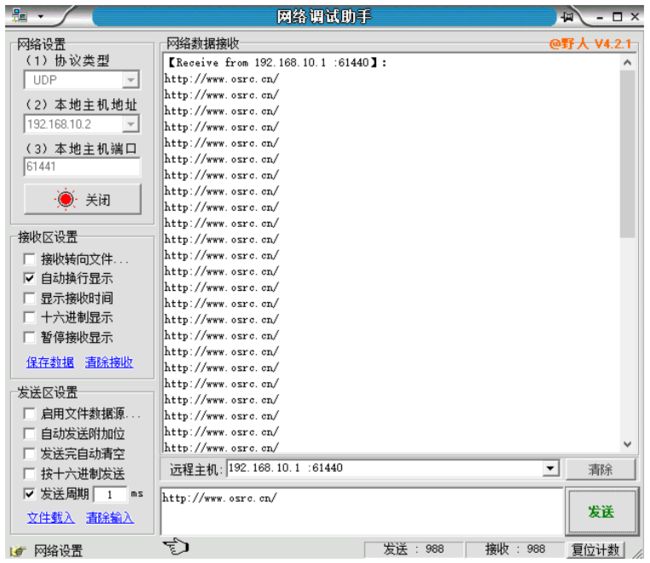

udp_ip_10g_sfp 实现了单路 UDP 网络传输功能,udp_ip_10g_sfp_4ch (MK7160FA中为udp_ip_10g_sfp_4ch)中同时例化了 4 个 UDP IP 协议栈, 实现了 4路 UDP 网络传输功能。在例程中,电脑的 IP 地址为 192.168.10.2,UDP 端口号为 61441,MK7160FA 开发板中的 4 个 SFP 接口的 IP 地址均为 192.168.10.1,UDP 端口号均为 61440。

对于udp_ip_10g_sfp例程,将万兆SFP+模块及连接线插入SFP-A 对应的屏蔽笼内。对于udp_ip_10g_sfp_4ch

例程可将万兆 SFP+模块及连接线与 SFP-A、SFP-B、SFP-C、SFP-D 中任意一个 SFP 屏蔽笼连接。

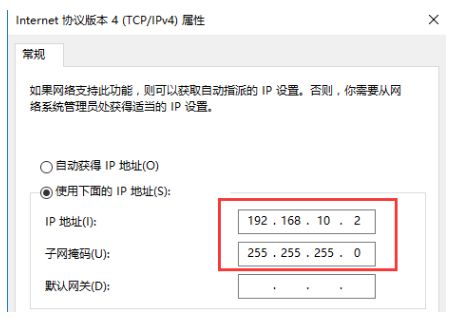

测试前,需要将所使用电脑网卡的 IP 地址设置为 192.168.10.2,子网掩码设为 255.255.255.0,如下图所示。

下载 bit 文件后,确认网络连接状态是否为 10Gbps,如下图所示。

5..6.1路测试

打开网络调试助手,分别设置好电脑和开发板的IP地址位和UDP端口号, 通过网络调试助手以udp包的形式向开发板发送文字数据,并以1ms的间隔不断循环发送,如下图所示。

测试结果上图所示。从图中可以看出,网络调试助手所发出的udp包和开发板返回的udp包一致,接收和发送的数据包数量一致。

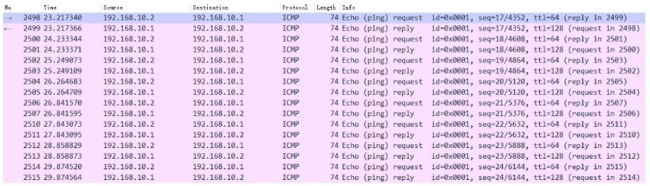

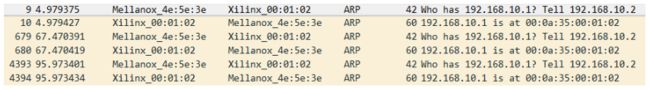

通过 wireshark 软件可捕获电脑和开发板之间的通信数据包,如下图所示。

通过 wireshark 软件可捕获电脑和开发板之间的通信数据包,如下图所示。

5.6.2 ARP 测试

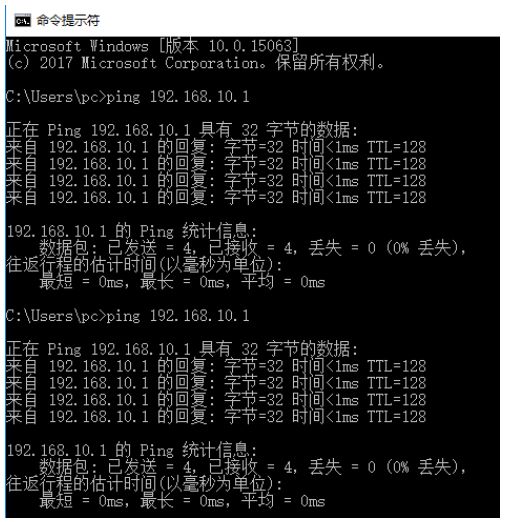

在网络调试助手向开发板发 UDP 包的同时,通过 cmd 命令窗不断向开发板发起 ping 命令,观察 ping 命令的返回,如下图所示。从图中可以看到开发板能够快速响应电脑发起的 ping 命令,UDP 数据包收发与 ping 应答互不干扰。

通过 wireshark 软件对 ping 过程的数据进行抓包验证,如下图所示。

在整个测试过程中,电脑会以一定频率持续向开发板发送 ARP 请求,开发板均能及时响应,wireshark 软件抓取的电脑与开发板的 ARP 通信过程如下图所示。

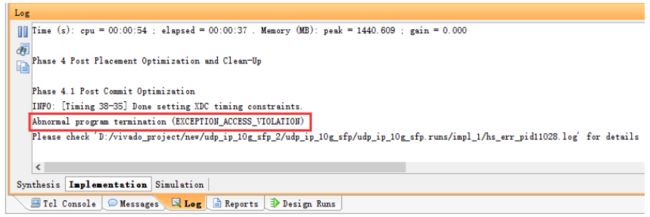

5.7解决方法

对于在 vivado 2016.4 中使用 10 Gigabit Ethernet Subsystem IP 核在 place design 过程中处于卡死状态,软件运行出现异常终止的 bug,如下图所示。

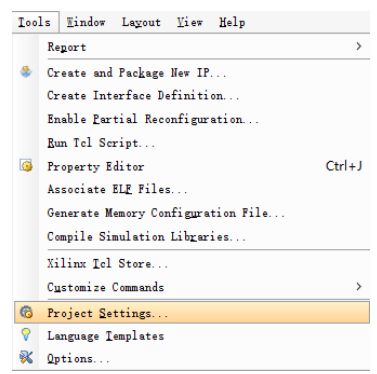

解决方法如下:

上述的 2 个步骤可以通过在place design 过程进行之前和之后插入 tcl 脚本的方法来进行。具体方法如下:选择

project setting

在 implementation 中找到Place Design,设置 2 个 tcl 文件的路径,如下图所示。

其中,在 pre.tcl 中写入:

set_property is_loc_fixed false [get_ports -filter { IS_LOC_FIXED == "TRUE" } ]

在 post.tcl 中需要指定 xdc 文件的绝对路径,例如:

read_xdc D:/vivado_project/MK7160FA/udp_ip_10g_sfp/udp_ip_10g_sfp.srcs/constrs_1/new/udp_ip_10g.xdc

设置完成后,在编译过程中就不会再出现报错。