Vivado如何生成BIN或MCS文件并烧写到FLASH中

一. 参考资料

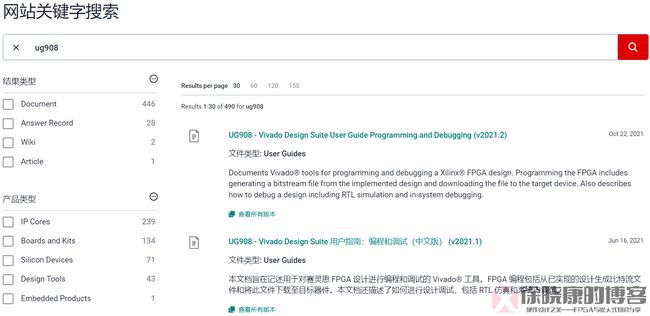

参考资料:UG908 - Vivado Design Suite 用户指南:编程和调试(中文版) (v2021.1)

传送门:Xilinx官网——网站关键字搜索——ug908

目前(2021年11月29日)最新版是v2021.2,中文版可能要过几个月才出,而次新版v2021.1有中文版,参考此中文版更方便。

二. Vivado生成BIN或MCS文件

Xilinx的配置文件有好几种,想了解它们之间的区别以及如何使用它们可参考我的另一篇博客。

传送门:Xilinx配置文件——BIT、RBT、BIN、MCS以及HEX的区别与使用

2.1 生成BIN文件

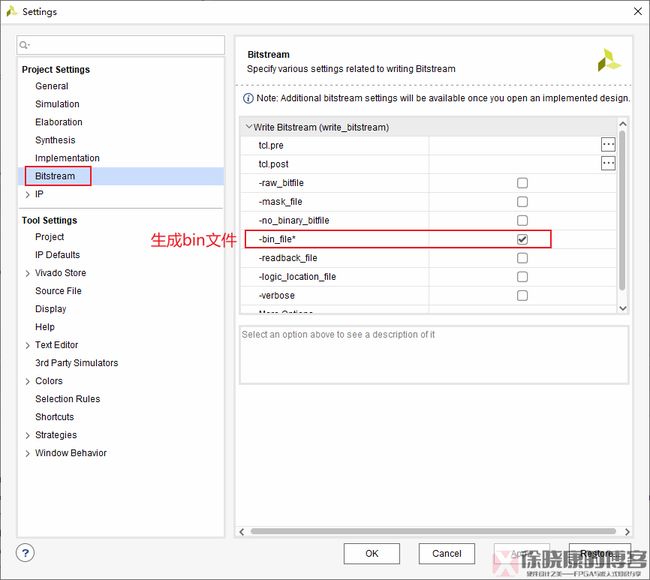

默认情况下,Generate Bitstream并不会生成BIN文件,只会生成bit,如果想在生成bit文件的同时也生成BIN文件,则需要进行如下操作:

Tools -> Settings -> Bitsream -> 勾选-bin_file* -> OK

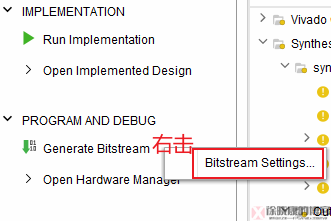

或者 左侧流程导航栏 -> PROGRAM AND DEBUG -> 右击Generate Bitstream -> Bitsream Settings…,也可进入Bistream设置界面

生成完成后,重新生成bit流文件,就会在生成bit文件的同时,也生成一个bin文件。生成路径是project目录下 -> *.runs -> impl文件夹。

2.2 生成MCS文件

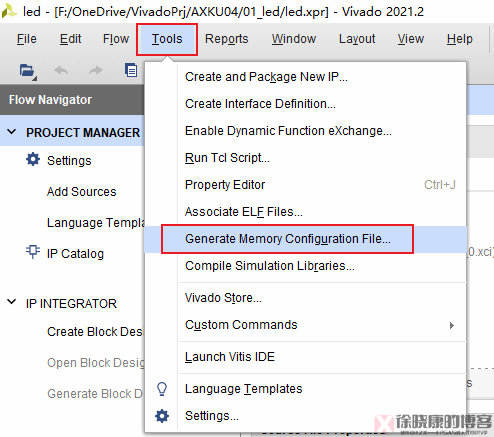

2.2.1 打开创建存储配置文件窗口

Tools -> Generate Memory Configuration File…

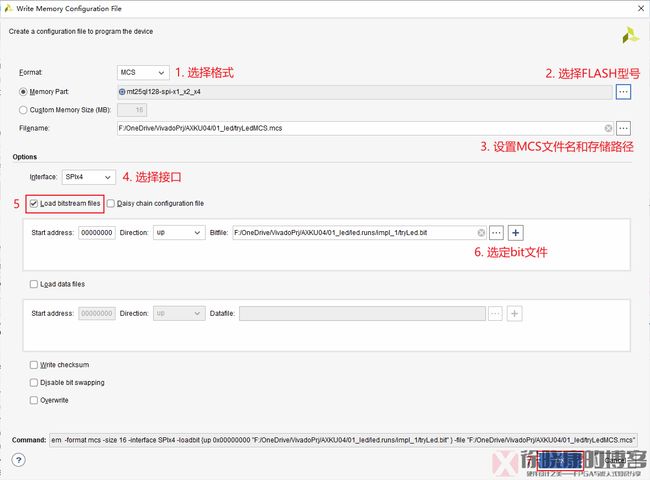

2.2.2 生成MCS总流程,第一步选择格式为MCS

有三种格式可选,MCS,BIN 和 HEX。

2.2.3 选定要烧写的FLASH型号

2.2.4 设置MCS文件名和存储路径

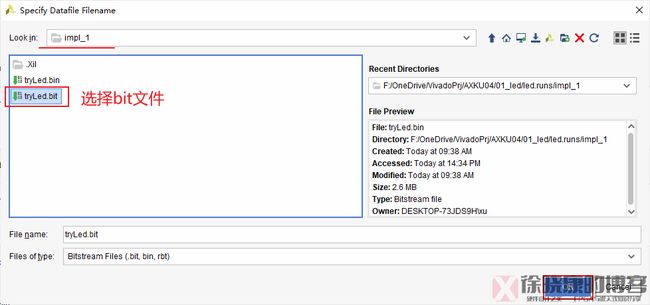

2.2.5 选择bit文件

其实此窗口就是运行一个TCL命令来生成MCS。

三. Vivado将BIN/MCS下载到FLASH中

3.1 Open Hardware Manager -> Open Target -> Auto Connect,连接上JTAG下载器

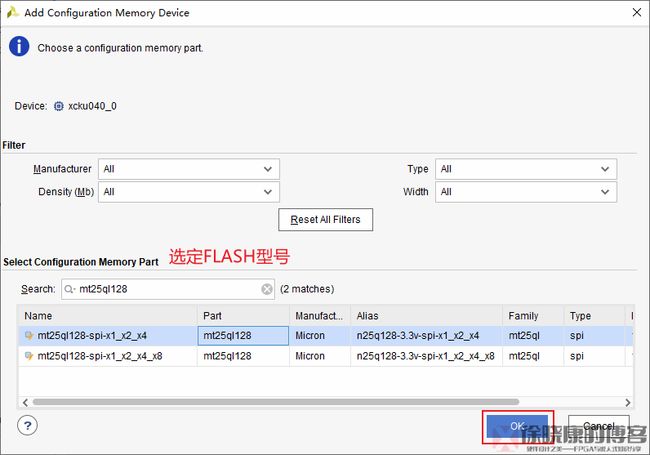

3.2 在自动检测出的芯片上右击,选择Add Configuration Memory Device…

3.3 选定FLASH型号,OK

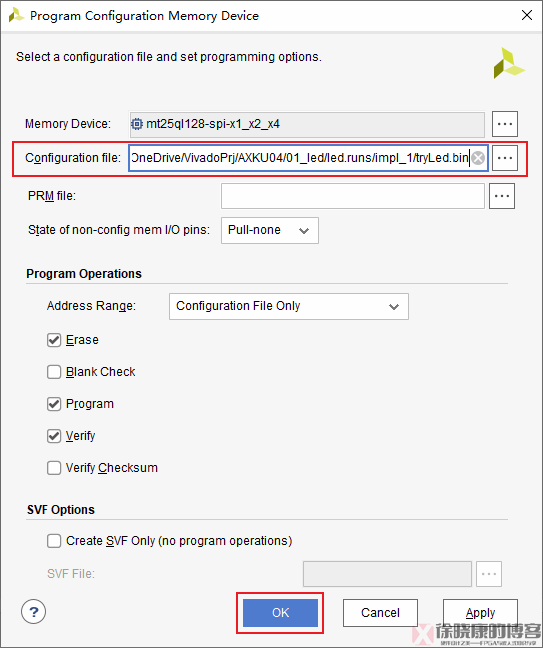

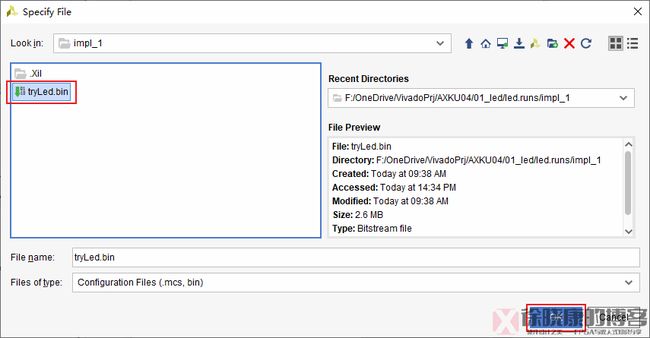

3.4 选择要下载到FLASH中的BIN文件或MCS文件,OK

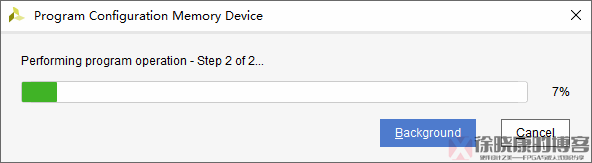

3.5 等待烧写完成

到此,FLASH烧写已经完成了。断电重启板卡,验证一下程序是否能正常加载。

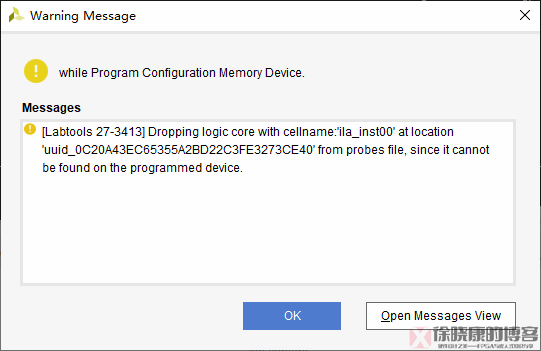

3.6 使用ILA可能出现的警告

如果工程中使用了ILA,则在FLASH烧写完成时可能提示如下警告,意思是没有检测到ILA,这是因为FLASH中的程序需要断电后才能运行,现在板上还没有运行刚烧写的程序。所以我们不用理会此警告,断电重启板卡,会发现程序以及ILA都已经烧写到FLASH中了。

[Labtools 27-3413] Dropping logic core with cellname:‘ila_inst00’ at location ‘uuid_0C20A43EC65355A2BD22C3FE3273CE40’ from probes file, since it cannot be found on the programmed device.

四. 如何加快FPGA加载FLASH中程序的速度

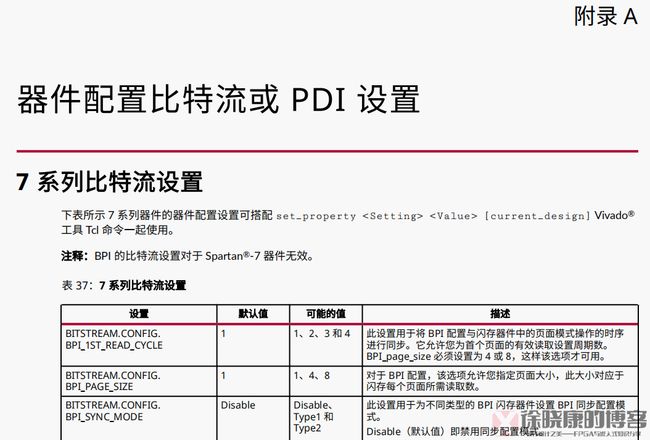

可以通过增加约束的办法来提高FLASH中程序的加载速度,主要用到以下几个配置约束语句:

1)以下命令表示压缩生成的bit文件,而BIN和MCS是根据bit生成的,所以,此语句也能使BIN和MCS文件更小,文件更小,加载完成自然更快。我测试了一下,一个简单的点亮LED的程序,不使用COMPRESS,bit文件大小是15632KB,使用之后是2147KB,可见此命令还是很有效果的。

需要说明的是:此命令并不能保证一定能减小文件体积,它通常起作用但不总是起作用,你可以在所有设计中加入这一条约束,好像并没有什么坏处?

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

2)以下命令表示设置SPI总线的宽度,这要跟硬件对应,不能乱写,一般FLASH有两种配置方式:SPI和BPI,其中SPI的总线宽度有1, 2, 4, 8四种。

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

3)设置配置模式,同样需要和硬件对应,但经过试验,此约束加与不加没有影响。

set_property CONFIG_MODE SPIx4 [current_design]

4)设置配置时钟频率,50表示50MHz,此约束对加载速度的影响是最大的,使用时注意约束频率不能高于FLASH芯片最高支持的频率。

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

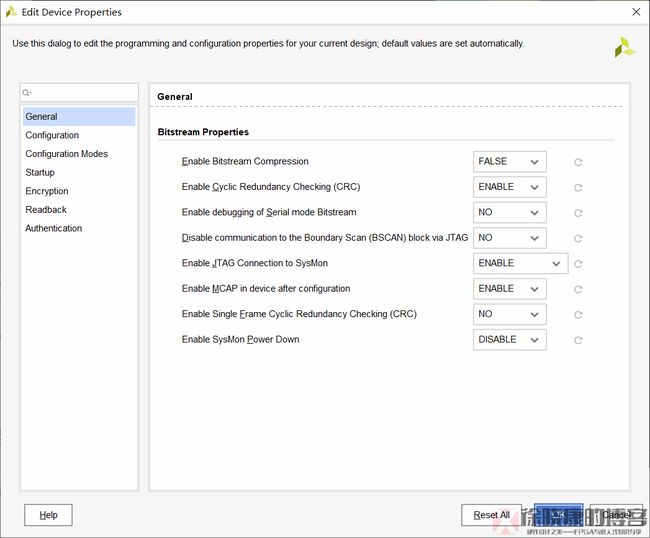

其实控制程序配置的约束命令还有很多,Xilinx将这些命令全部集成到了Vivado的图形界面中,其实是不需要记忆,也不需要手输的,打开程序配置界面的方法如下:

在综合完成后,Open Implemented Design -> Tools -> Edit Device Propeties…

关于每个选项的含义可参考UG908的附录。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。