高性能国产化信号处理平台国产DSP+FPGA+AI NPU安路紫光方案

一、有了NPU,还要DSP吗?

· 其实都是针对某种算法进行加速的处理器,不过NPU针对的是那些神经元算法,DSP针对的是信号处理算法,二者各有侧重

NPU采用普林斯顿结构。

DSP采用哈弗结构。

各自有自己的指令系统。

DSP是专注数字信号处理的,即使DSP处理器其实也是分了很多针对不同类型的信号的不同型号类型,比如有音频信号的、图像的等待

NPU是专注于神经网络处理的,处理不同的数据。

用通用架构的CPU处理AI和用NPU处理AI,速度是不同,但为什么还是离不开CPU呢,因为NPU只能处理AI计算,其它的也是不行的。

· DSP(digital signal processor)是专业做数字信号处理的。DSP是一种独特的微处理器(采用哈佛结构,内部结构已经固定),有完整指令系统,通过指令和数据工作(这个也是CPU和ARM等的工作方式),开发遵循嵌入式软件的设计原则,更注重于算法的实现。

NPU是嵌入式神经网络处理器(NPU),采用“数据驱动并行计算”的架构,特别擅长处理视频、图像类的海量多媒体数据

在NPU中集成那些可支持必要服务操作的功能及服务。DSP可定制以便集成及增加通道的密度与速度,但不是设计用来增加DSL服务能力,如更好的网络弹性、更精细的网络流量管理、更完善服务保证以及用于处理新服务机会的更多灵活性等。NPU在这些功能上更具有优势。

至于算力的衡量

国外知名媒体Anandtech选择了使用麒麟960的华为Mate 9、使用麒麟970的华为Mate 10 Pro、使用骁龙835的谷歌Pixel 2 XL和LG V30四款手机,分别测试了ARM CPU、Hexagon DSP和NPU的AI性能,测试结果以性能(fps)和效能(mJ/inference)双重指标来衡量。

NPU和CPU在处理AI运算时的性能有着几十倍的巨大差异。这些算法在CPU上执行的速度最高不过2fps,同时还会消耗掉大量的电能。无论是骁龙835还是麒麟960的CPU平均功耗都已经超过可持续工作的上限。

作为对比,骁龙835的Hexagon DSP相比CPU约有8~10倍的性能提升,而麒麟970的NPU性能又可达到Hexagon DSP的1.5倍~4倍。不过在能耗比方面,虽然华为NPU相比CPU有着巨大到已经不在一个次元的优势,但骁龙835的Hexagon DSP的综合效率落后麒麟970的NPU仅6%左右。

传统芯片厂商(如CPU、GPU和DSP)对于深度学习市场非常重视,因此利用他们巨大体量和市场推广、销售能力,大力推广用这些传统芯片来进行深度学习处理,其本质上也是对现有的技术进行微调,用传统SIMD架构来适配神经网络。

然而,由于传统CPU、GPU和DSP本质上并非以硬件神经元和突触为基本处理单元,相对于NPU在深度学习方面天生会有一定劣势,在芯片集成度和制造工艺水平相当的情况下,其表现必然逊色于NPU。

二、DSP+FPGA+AI NPU方案

信迈科技高性能国产化信号处理平台采用多通道双向10Gbps光纤数据传输+国产V7 FPGA+多片国产多核DSP的硬件架构,可以完成一体化电子系统、有源相控阵雷达、电子侦察、MIMO通信、声呐等领域的高速实时信号处理。

信迈科技信号处理平台的组成框图如图1所示,由四组4通道双向光纤接口、FPGA 及其扩展电路(2组独立读写的 DDR3 存储器、FPGA扩展的4个串口、实时控制信号输入/输出等),两片FT-M6678 DSP及其扩展电路、DSP时钟电路、100M/1000M以太网、主DSP的RS232扩展、DSP间互连接口、DSP与 FPGA间的EMIF、SRIO接口,供电电源等部分组成。

硬件资源

1 接口

光纤数据传输接口:四组 4 通道双向光纤,传输速率 10Gbps

以太网:主、从DSP各扩展1个100M/1000M以太网,主DSP以太网口与终端连接,从DSP以太网口备份

串行口:主DSP提供1个串口,FPGA为主DSP扩展4个串口,从DSP不扩展串口

实时控制信号接口:1个与信号采集单元的定时控制信号接口(含RS422通信口)

双天线北斗接口:北斗定位定向模块可直接安装在信号处理平台上

倾斜仪接口:电源输入及控制接口1个

8 位测试信号输出口1个

120MHz时钟输入口1个

FPGA、DSP 调试口。

2 国产FPGA

国产V7 FPGA(复旦微电子或国微)

3 FPGA拓展存储器

2组独立读写DDR3存储器,每组容量为256M×64bit,读写时钟频率最高支持1600MHz。

4 国产DSP

2 片国产多核DSP

5 DSP拓展存储器

256M×64bit DDR3 存储器,读写时钟频率最高支持 1600MHz;

4Gbit NAND Flash 存储器;

64Mbyte SPI NORFlash;

1Mbit I2C EEPROM;

FPGA内部EMIF接口双口RAM。

6 FPGA与DSP间接口

两组 SRIO×4 ,速率 3.125GBaud;

EMIF×16 接口;

GPIO 接口。

7 DSP间的互联接口

PCIe×4 ,每 Lane 5GBaud;

扩展在 FPGA 内部的 EMIF 双口 RAM。

8 外部输入时钟

频 率 :≤400MHz;

功率:8dBm ±2dBm ;

输出阻抗:50Ω;

信号形式:正弦波。

9 板载时钟

板载时钟:200MHz 差分时钟

10温度检测

提供3个温度传感器,检测 FPGA、DSP 附近温度

11风扇及控制

提供风扇供电及开关控制

12LED 指示

FPGA 扩展 4 个 LED 指示灯

13供电及功耗

供电电源:+12V±1V ;功耗:≤70W

外形、尺寸及重量

外形如图 2 所示,尺寸为:280mm×150mm×10mm(长×宽×高,不含扇热板),重量≤400g(不含散热板)

设计开发资源

★ 多通道光纤数据传输协议

★ 以太网分包数据传输协议

★ 多核DSP资源分配

★ 信号处理平台硬件资源说明

★ 信号处理平台器件手册

★ FPGA及扩展资源测试程序

★ DSP及扩展资源测试程序

★ 四通道光纤数据发送、接收FPGA软件

★ 多波束DBF、时域脉压、频域脉压、DDR3存取、FFT、SRIO接口、EMIF接口、扩展串口等FPGA软件

★ 国产多核 DSP 正样手册及交付物 V2.5.zip

0. 支持包安装程序

1. Document(详规手册)

2. Emulation

3. Hardware

4. Project

5. 评测文档

6. DSP 用户常见问题-v1.1.pdf

★ 国产多核 DSP 正样手册及交付物 V2.6.zip

0. 持包安装程序

1. Document(详规手册)

2. Emulation

3. Hardware

4. Project

5. 评测文档

6. DSP 用户常见问题-v1.1.pdf

★ 国产多核 DSP 仿真器光盘文件 V1.2.zip

EMU560 仿真器

SEED-XDS510PLUS仿真器

★ 国产多核 DSP 仿真器光盘文件 V1.3.zip

EMU560 仿真器

SEED-XDS510PLUS 仿真器

★ TI-6678 例程包K1_STK_v1.1(example code)

内含TI-6678 的 EMIF、GE、GPIO、Hyperlink、I2C、内存(DDR3、L2 等)、多核导航器、PCIE、Robust、SPI、SRIO、Timer、UART 和 DMA 等测试例程。

★ CCS 环境搭建安装包

内含 CCSv7.2.0 和 CCSv5.5.0 安装包及其环境相应配置过程。

★DSP 串口、FPGA 扩展串口通信软件

★ 以太网通信软件

★ 两维相扫数字多波束雷达 DSP 信号处理软件例程

★ 两维相扫圆柱阵雷达 DSP 信号处理软件例程

★ 一维相扫雷达 DSP 信号处理软件例程

★ Matlab 程序

应用领域

★ 一体化电子系统实时信号处理

★ 有源相控阵雷达实时信号处理

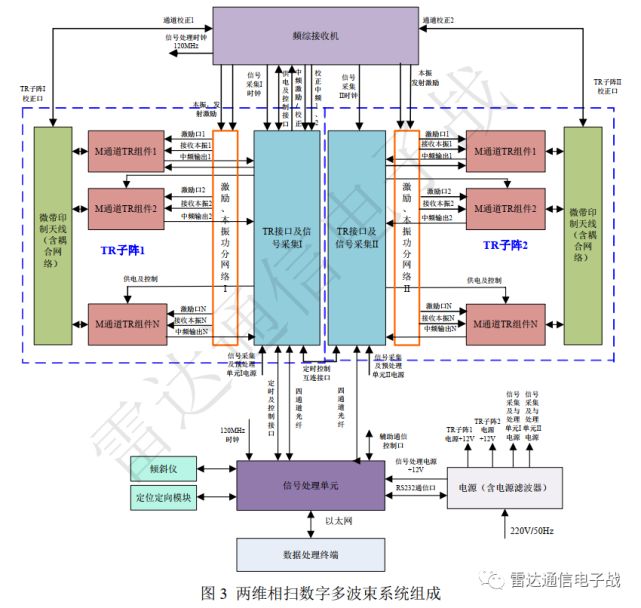

国产高性能信号处理平台已应用于图3所示的两维相扫数字多波束系统中,实现了6波束 DBF、脉压、MTD、目标检测、目标识别等实时信号处理,可实时处理每波束8000以上距离单元。

★ 电子侦察实时信号处理

★ MIMO通信系统实时信号处理

★ 声呐阵列信号处理

★ 实时信号处理算法性能评估