学术贴 | FPGA 加速图数据库查询执行

导读

本篇博客主要讲解发布于 Microprocessors and Microsystems 的文章《Semi-static Operator Graphs for Accelerated Query Execution on FPGAs》,介绍它所提出的算法与试验结果,并结合实际情况给出一些思考。

一、背景介绍

在当今的数据化场景越来越丰富的大环境下,涌现出的非结构化数据存储分析被应用于多数领域。为了使机器能够自动分析数据,语义网络的概念被创建,元数据被用来描述和链接任何类型的数据和资源。

面对存储和处理大规模的数据,除了不断被优化的数据结构外,硬件也是需要被极大优化的。海量数据的持续存储在当今硬件环境下是没有问题的,但是要实现在一个可以被接受的、被允许的时间范围内进行处理和分析则变得愈发艰难。

因此,许多数据库系统逐渐倾向于异构,由专门的计算内核来有效地执行特定的任务。

那么不得不提的,便是高性能计算常用到的 GPU (图形处理器)。GPU 最突出的优点是高性能,即高密度运算和高效并行性,非常适合处理计算密集型的任务;同时,其易于连接到处理器端的属性也是它可以被广泛应用的原因。然而,其缺点也是显而易见的,就是高功耗。

在 GPU 之外,还存在为特定任务设计的专有硬件加速器,其对于指定的任务拥有较高的性能,但是其使用非常的不灵活,只能处理特定的任务,重新扩展的性能几乎为零。

最后,则是最近被广泛使用的 FPGA,它具有动态部分重配置的能力,可以缩小 CPU 的灵活性和专用硬件加速器的性能之间的差距,并且还拥有低功耗、高并发的优势。

FPGA 卡的核心部分示意图

如上图所示,一块 FPGA 芯片由可配置逻辑模块(CLB)构成,每个 CLB 都包含特定的结构,如:查找表(LUT)、多路复用器、进位链、触发器等。除此之外,一块 FPGA 卡上还有 BRAM(Block RAM),可以将其想象成 CPU 中 cache 的角色,以及 DSP (数字信号处理器)和一些通信接口(PCIe 等)。

这篇文章通过引入半静态操作符图,设计了一个 FPGA-CPU 异构的图数据库系统,加速了在大规模语义数据集上的查询性能。

二、相关工作

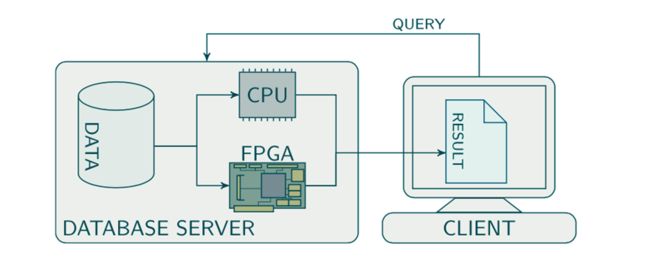

上图为一个 FPGA-CPU 混合处理运算的基本架构,客户端应用程序向混合数据库服务器发送查询,该服务器使用基于 FPGA 的硬件加速器透明地确定结果。

文中主要引用的内容为:

Dennl 等人提出了关系型数据库 MySQL 中 SQL 查询的实时硬件加速的概念,但他们主要关注限制和聚合操作符,因此无法在 FPGA 上执行完整的查询。

Becher 等人添加了更复杂的运算符(例如:归并连接、小数据集上的排序)。对于一个包含一个 Join 的简单的查询,它们的性能与标准的基于 x86 的系统相当,不过能源效率更高一些。

Woods 等人提出了 Ibex,一种用于关系数据库 MySQL 的智能存储引擎,可以支持使用 FPGA 卸载复杂的查询操作符。

Wang 等人使用 OpenCL high level synthesis (HLS) 将数据库操作符实现为 FPGA 的 Kernel。但是查询只用到了范围检查和一个 Join,相对简单。

Heinrich 等人提出了一种混合索引结构,它在 FPGA 上存储包括根节点在内的高层 B+ 树,在主机上存储包括叶子节点在内的低层。

而本文是第一个针对语义 Web 数据库完全集成的基于 FPGA 的查询引擎。

在介绍本文的混合数据库系统之前,先介绍一下本文用到的图数据库基础。论文的工作是基于一个开源的图数据库系统 LUPOSDATE,它支持完整的 SPARQL 1.0 和 SPARQL 1.1 标准查询语言。论文通过引入基于 FPGA 的查询引擎,与 LUPOSDATE 系统结合在一起。

LUPOSDATE 使用 RDF 三元组作为基本数据格式来描述 Web 资源,RDF 三元组表示为

相应的,LUPOSDATE 存储的 B+ 树索引结构有六种:SPO、SOP、PSO、POS、OSP、OPS,可以在检索时方便的得到有序的三元组。除此之外,LUPOSDATE 还维护一个 ISTree 和一个 SITree,用于 RDF 字符串和整数 id 之间的映射,这有利于 FPGA 模块的设计,因为 FPGA 无法处理不定长度的字符串。

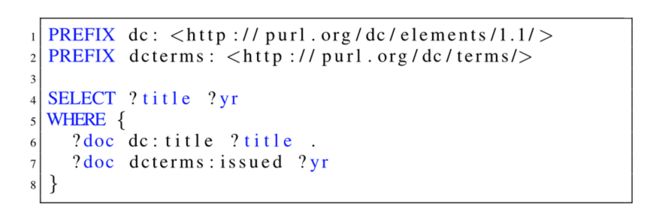

如下图所示,对于给定的一个 SPARQL 查询:

LUPOSDATE 语法分析器会产生相应的变量数组和操作符图:

三、论文解决的问题

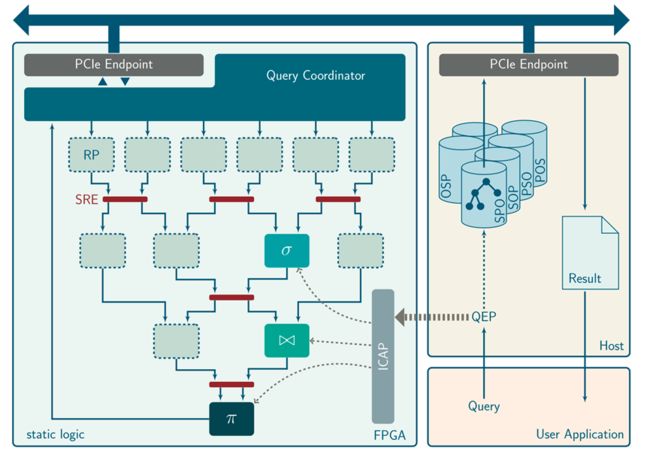

本文实现的混合数据库系统是一个 LUPOSDATE 的扩展,由 CPU 主机和 FPGA 异构而成,如上图所示。主机提供更高层级的功能,如用户界面、查询优化、评估指标维护等,而 FPGA 被用作查询执行时的自适应加速器。主机和 FPGA 之间的通信是基于外设原件 PCIe 的。

FPGA 区域被划分为静态逻辑和许多个小 RP,每个 RP 可以配置任意类型的运算符,每个运算符作为一个可配置模块是提前生成的。静态逻辑包含与实际查询结构独立的模块,包括 PCIe 接口、一个管理模块和查询协调器(QC)。

QC 的主要任务是将传入的三元组交给最上层的 RP 进行相应索引结构的导入,以及检索和序列化变量数组用以生成最终结果。此外,每个 RP 之间的互联也位于静态逻辑中。每个实现的查询操作符都使用了如下图所示的一个公共模板:

每个操作符至多有两个前向操作符和一个后向操作符,如果一个操作符只需要一个前向操作符,那么只有左边的输入被启用。每一个输入或输出都有如下参数:一个 data 向量对应输入输出的数组,一个 valid 信号表示数据的有效性,一个 finished 参数指定数据的结尾,一个反向 read 信号通知前向操作符数据已经被读取,并且在新数据到来之前不会进行操作。最后,数据的宽度也必须作为一个参数传入,因为 FPGA 无法支持变长的数据类型。

下面介绍一下论文实现的操作符:

-

RDF3XIndexScan:RDF3XIndexScan 是 QC 和内部操作符之间的联系。这个操作符的主要目标是从 QC 中接收三元组,并将它们所需的组件映射到变量数组的某个位置。它维护三个 one-hot 编码的向量,每个向量的第 i 位代表第 i 个变量,如果某一个元素是常量,那么就将其所有位置为 1。

-

Join:Join 操作符是自然连接,本文使用的是 MergeJoin 的方式。它维护一个 one-hot 编码的向量,向量的第 i 位代表第 i 个变量,指代要 Join 的变量。

-

Filter:Filter 操作符是用于执行条件查询。复杂的 Filter 表达式将被分解为多个简单的 VALUE COND VALUE 的 Filter 操作符。其中,VALUE 可以是一个值、一个变量或一个式子,COND 是比较条件。但由于 FPGA 无法处理字符串的问题,所以通过将字符串映射为整数 id 之后,系统只能支持相等和不相等的比较。

-

Projection:Projection 操作符是用于将需要的变量结果从变量数组中投影出来。

-

Union:Union 操作符就是简单的将两个前向操作符得到的结果做一个并集操作。

-

Limit 和 offset:Limit 操作符会转发特定数量的结果给变量数组。而 offset 操作符会跳过特定数量的结果。它们一般作为操作符图的最后几步。

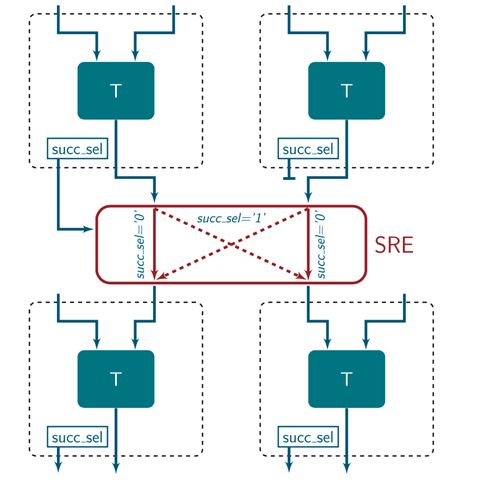

从混合系统结构图中可以看到,每个 RP 之间并不是直接输入输出互联,而是通过了一个上图所示的半静态路由元素(SRE)结构。论文以一个两路复用 SRE 为例,当 succ_sel 信号为 0 时,数据流会直接向下路由,为 1 时,会向另一侧路由。SRE 的存在使得可以用更少的 RP 组成一个支持查询范围更大的半静态操作符图。

四、混合系统工程流程

上图给出了混合系统的工作流程图,可以将其分为部署阶段和系统运行时。在部署阶段,除了需要导入数据之外,整个静态逻辑必须部署在 FPGA 上,每个操作符对应的 RM 也需要提前生成并存储在 RM 库中。

在系统运行时,主机通过分析输入的 SPARQL 查询,将其解析成相应的操作符图,检测其是否可以用配置在 FPGA 上,如果有不支持的操作符存在,那么会直接 CPU 端执行查询,如果所有操作符都支持,那么 ICAP 会选择对应操作符的 RM 配置在 FPGA 的半静态操作符图上。主机通过 PCIe 向 FPGA 端提供输入三元组,并接收 FPGA 端发回的结果进行后处理,FPGA 端负责具体的计算任务。

五、实验结果

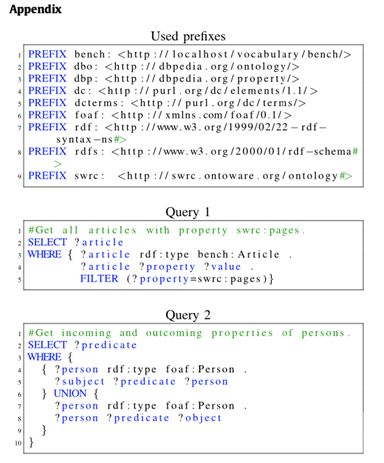

本文使用的是 Xilinx 的 Virtex-6 FPGA 卡和 PCIe 2.0 八通道通信接口,在 SP2Bench 三个不同大小的数据集(66M,131M 和 262M 个三元组)上进行了实验。下图是他们采用的 SPARQL 查询示例:

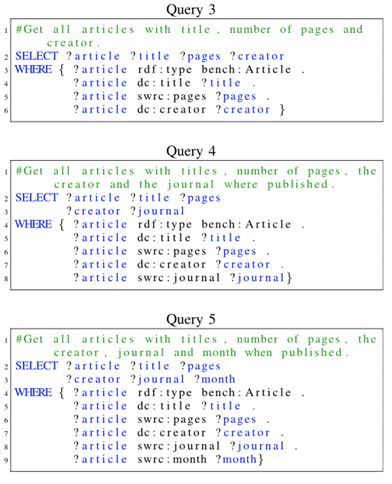

Query 1 是用到了 Filter 操作符的查询,Query 2 是用到了 Union 操作符的查询,Query 3-5 分别是用到了不同数量的 Join 操作符。他们在 FPGA 端部署的半静态操作符图如下:

最后的实验结果表明,加入了 FPGA 的混合系统比原来的 LUPOSDATE 系统的查询执行速度更快。并且随着数据规模的增大,加速比会更大,说明混合系统更加适合大规模的数据集上的查询。

六、总结

在这篇文章中,作者在 FPGA 上引入了半静态运算符图(SOG)的概念,为语义网数据库中的查询执行提供灵活的硬件加速器。作者没有为给定的查询系统运行时生成一个 FPGA 配置,而是以一定程度的灵活性部署了通用查询结构。

SOG 由多个具有公共接口的 RP 组成。在为每个 RP 部署系统期间,会生成一组部分位文件的 RM,并将其存储到存储库中。在系统运行时,作者的混合系统针对给定的 SPARQL 查询选择 RM,并通过 ICAP 将其配置为 RP,RP 设置 FPGA 上运算符图的最终结构。作为这项工作的主要贡献,耗时的 RM 生成在系统运行时之前执行,并且信号大大减少了查询执行期间的重新配置。