Physical implementation —— LEF and DEF

LEF

LEF 是Library Exchange Format 的首字母缩写,是C 家物理库的描述格式。LEF 分为tech lef 跟cell lef 两种,不论是哪个阶段的工具要使用lef 都必须先读入tech lef 再读入cell lef, 因为cell lef 中要引用tech lef 中定义的信息。

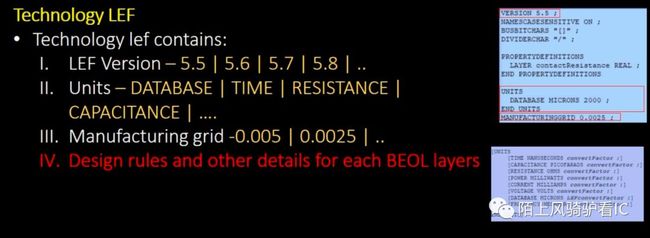

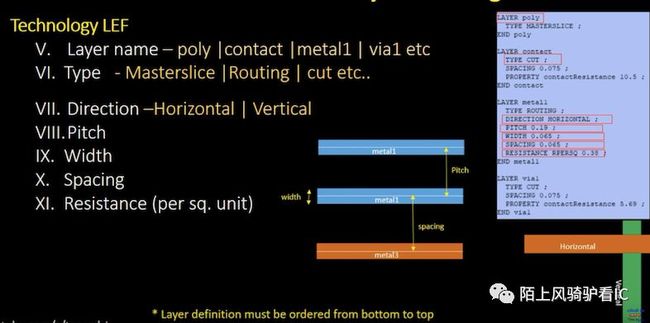

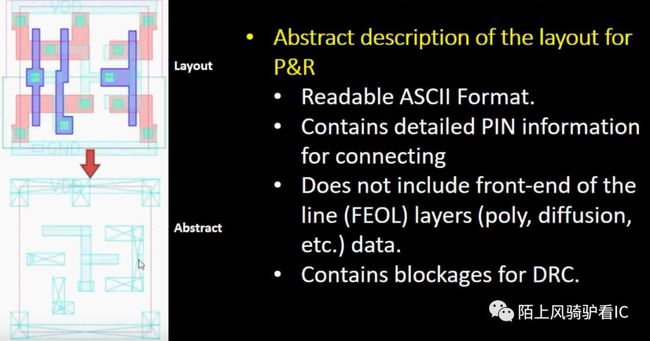

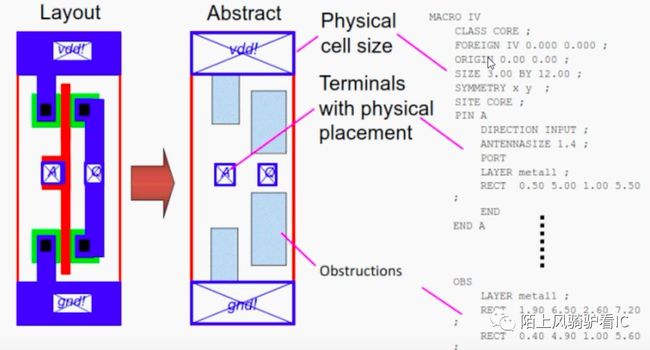

Tech lef 中定义了metal layer, via, design rule 等信息,请详细研读下面几张从油管上抠出来的图,图中较详细介绍了tech lef, cell lef 各包含哪些信息以及cell lef 跟cell abstract view 的对应关系。

layer type: routing, cut (contact), masterslice (poly, active), overlap.

design rule: width, pitch, spacing.

- via definition.

- metal direction.

- resistance and capacitance per unit square.

- antenna factor.

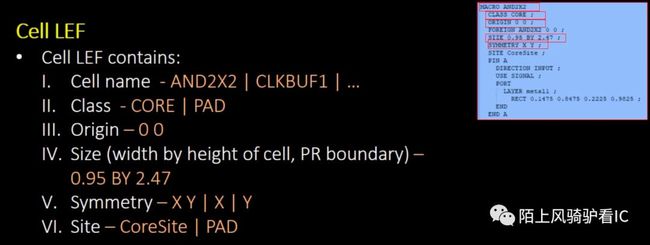

Cell lef 中定义了cell 的几何形状跟abstract view:

- site extension.

- cell descriptions, cell dimensions.

- layout of pins and blockages, capacitances.

check_design 会做lib/lef 一致性检查,可以报出哪些lib cell 没有对应的lef 哪些lef 又没有对应的lib cell. 工具会对有lib 没lef 的cell 自动设置dont_use 属性,所以一定要保证综合所用的所有std cell 对应的lef 都被读入。

读def 时,如果某些macro 的lef 缺失,工具会报PHYS-* 的Error, 没lef 工具无法知道cell 的长相,pin 的位置,所以一定要把所用到macro 的lef 都读入。

DEF

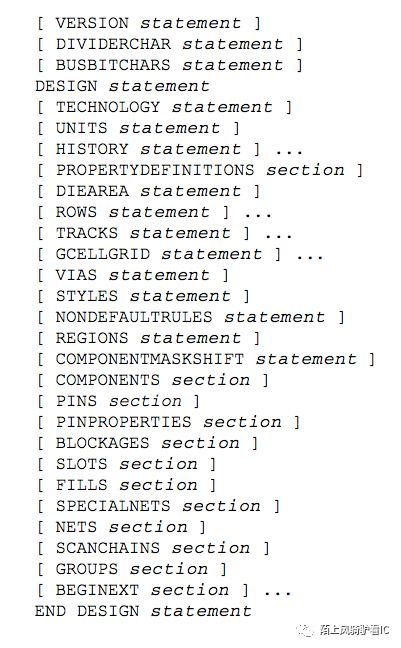

DEF 全称Design Exchange Format, 用于电路物理信息交互,是将数字实现前后端连接起来的桥梁。目前常用的DEF version 是5.8, 在DEF 中可以定义如下信息,本文不解析每一部分的含义,只概述做物理综合需要的部分信息。DEF file 有如下限定:

- 标识符的长度不能超过2048 个字符,如net 跟cell 的名字,通常如果设计中的某些cell 名字太长,在综合结束后都会做change_name 的动作,将其名字长度限定在2048 个字符之内;

- DEF 中的声明都是以";" 结束,而且必须在";"前加一个空格。

- DEF 中每个section 都只能指定一次,而且以"END SECTION" 结尾,DEF 文件通常都比较大,在拿到DEF 后可以用『 grep END 』来check 在当前的DEF file 中定义了哪些Section.

- DEF 中,除了NETS section 中 + ORIGINAL 之外,所有的objects 必须先定义后使用,其中一部分objects 从netlist 中读入,一部分objects 从techlef/lef 中读入,一部分objects 在DEF 中定义。

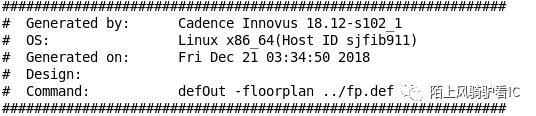

head

DEF 头部包含:

- 生成的工具及工具版本,此处为:Innovus 18.12-s102_1.

- Linux 的操作系统;

- 文件生产的日期;

- 当前设计的名字;

- 产生DEF 的命令,此处为:defOut -floorplan ../fp.def

units

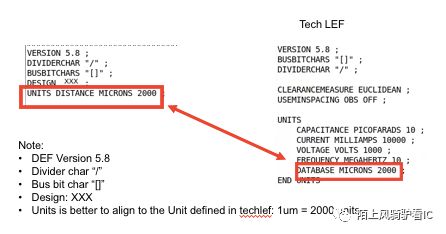

DEF 文件的第一部分定义了:

- DEF 的版本号,此处为5.8;

- 分割符;

- 总线比特符;

- 设计名;

- Units distance microns, 此处为2000.

其他部分都好理解,需要特别说一下Units, 这个units 的定义不是随心所欲可以改的,协议规定该值必须小于等于tech lef 中在DATABASE MICRONS 中指定的值,最好两边值一致,在某些先进工艺点,如果两个值定义不一致,VIA 会出现偏移。该值用于DEF 中实际距离的计算,如果为2000 则表示 1um = 2000 units。

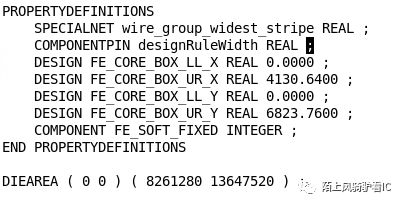

Properties and Die Area

需要在Properties 部分定义DEF 用到的所有Property, 同时Core2Die 的距离也在Properties 部分定义,到目前为止除了7nm H300 其他工艺对Core2Die 的距离无特殊要求,7nm H300 有特别具体的要求,否则会出现Track 偏移的问题。DIEAREA 定义了当前设计的形状及大小,如果是矩形为两个坐标,如果是多边形会有一串坐标。对应的坐标值除以Units distance microns 中units 的值即为实际的距离。

ROWS

所有的std cell 都需要摆放在ROW 上,所以在DEF 中需要将所有用到的SITE 都定义全,SITE 从Tech lef 中读入。

在DEF 中有几个section 的定义都需要指定方向,在ROW 的定义中也会指定方向,DEF 中的有效方向有以下几种。在上例中每两条相邻ROW 的方向差180 度,这样做的目的是:多条ROW 共用电源跟地。

TRACKs

要给每层可用于routing 的layer 定义好track 否则绕线资源不可用。这段原文描述比较好,翻译过来会变味,原文欣赏:"Defines the routing grid for a standard cell-based design. Typically, the routing grid is generated when the floorplan is initialized. The first track is located at an offset from the placement grid set by the OFFSET value for the layer in the LEF file. The track spacing is the PITCH value for the layer defined in LEF."

Components

用于综合的DEF 该部分内容:

所有的hard macro 都应该定义为placed 或fixed.

将所有的physical only cell 都写出来,占位置;

如果有power swtich 最好也写出来,占坑;

所有的hard macro 都应该有lef, 否则工具无法知道其形状,也会报错;

不要把STD cell 写出来,除非某些手工例化且有位置要求的STD cell.

Pins

此处的pin 指hard macro 的输入输出端口,该部分定义每个pin 的位置,最好每个pin 都assign 好位置,但是通常在实现初期有一些pin 没用到如DFT 的pin, 没有位置可以接受。

VIAs and SPECIALNETs

综合用的DEF 不需要signal nets, 但一定要把Special nets 写出来,尤其对16nm 之后的工艺结点,Special nets 会占去许多绕线资源,对timing 跟Congestion 都有很大影响。

Special nets 部分会用到VIA, 需要将所有用到的VIA 都提前定义好。

Lists the names and geometry definitions of all vias in the design. Two types of vias can be listed: fixed vias and generated vias. All vias consist of shapes on three layers:

a cut layer and two routing (or masterslice) layers that connect through that cut layer.

A fixed via is defined using rectangles or polygons, and does not use a VIARULE. The fixed via name must mean the same via in all associated LEF and DEF files.

A generated via is defined using VIARULE parameters to indicate that it was derived from a VIARULE GENERATE statement.

For a generated via, the via name is only used locally inside this DEF file. The geometry and parameters are maintained, but the name can be freely changed by applications that use this via when writing out LEF and DEF files to avoid possible via name collisions with other DEF files.

Blockages and Regions

Blockages 跟Regions 都属于设计约束,最好不要写到DEF 中,可以单独写到Tcl 文件中,如在Innovus 中用命令:“writeFPlanScript -section” 写出。