STA环境 - 时钟

目录

- 1. 指定时钟`create_clock`

-

- 1.1. 时钟延迟`set_clock_latency `

- 1.2. 时钟不确定度(时钟抖动)`set_clock_uncertainty `

- 1.3. 时钟过渡时间`set_clock_transition `

- 2. 衍生时钟`create_generated_clock`

- 3. 划定时钟域`set_clock_groups`

STA环境配置中对时钟如何约束

XDC约束技巧之时钟篇

1. 指定时钟create_clock

● 时钟树: 时序电路中从时钟源到各触发器CK端时钟路径构成的结构。

芯片端口输入输出的主时钟、以及RXCLK/TXCLK等随路时钟都必须由用户使用create_clock自主创建,该时钟就是时序分析的起点。

配置的SDC如下

# 名称: SYSCLK

# 周期: 20ns

# 占空比: 20ns内上升沿时刻为0ns,下降沿时刻为5ns

# 端口: SCLK

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

# 名称(默认端口名): CLKA

# 周期: 20ns

# 占空比(默认-waveform (0,period/2)): 50%

# 端口: CLKA

create_clock -period 20 [get_ports CLKA]

1.1. 时钟延迟set_clock_latency

分为网络延迟和源延迟。

● 网络延迟(network latency): 表示芯片内部时钟定义点到第一级触发器CK端的时钟延迟,即input2reg。

● 源延迟(source latency): 表示芯片外部时钟源(比如晶振时钟、数据随路时钟)到时钟定义点的时钟延迟

如下图所示。

理论上这些时钟延迟都为0,可以在STA时使用set_clock_latency 指令指定时钟树综合前所有终点的时钟延迟估计值。一旦时钟树建立完毕,就会忽略该约束,并使用实际走线延迟替代。

一般指定网络延迟即可,SDC如下

# 时钟CLK_CONFIG的上升沿和下降沿时钟延迟均为0.8ns

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

# 时钟MAIN_CLK的上升沿时钟延迟为1.8ns

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

# 所有时钟定义的下降沿时钟延迟为2.1ns

set_clock_latency 2.1 -fall [all_clocks]

# 时钟SYS_CLK的上升沿和下降沿源时钟延迟均为1.9ns

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

1.2. 时钟不确定度(时钟抖动)set_clock_uncertainty

从PLL出来的时钟信号周期存在一定程度的抖动。

当然理想情况下抖动为0,可以在STA时指令设定一个时间窗口,该窗口内任何时候都有可能产生时钟沿,这样的时间窗口就可以表示抖动量。

如下图

时钟抖动会提高对建立时间裕度和保持时间裕度要求,因此分为setup uncertainty 和 hold uncertainty。

如下图所示,effective clock period为根据时钟定义确立的预期时钟沿位置,setup uncertainty为早于预定时钟沿的的不确定度,hold uncertainty为晚于预定时钟沿的的不确定度

SDC指令如下

# 时钟CLK_CONFIG的setup uncertainty

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

# 时钟CLK_CONFIG的hold uncertainty

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

# 时钟SYS_CLK到CFG_CLK的跨时钟路径的hold uncertainty 为0.05ns

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

# 时钟SYS_CLK到CFG_CLK的跨时钟路径的setup uncertainty 为0.1ns

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

● 时钟偏斜(clock skew): 时钟信号从时钟源PLL到达不同终点的时间差。时钟延迟和时钟抖动导致了时钟偏斜。

1.3. 时钟过渡时间set_clock_transition

指时钟从阈值电压的起始点到终止点所需的时间。压摆率(Slew rate)是过渡时间的倒数。

指令如下

# 时钟CLK_CONFIG的上升沿过渡时间为0.1ns

set_clock_transition -rise 0.1 [get_clocks CLK_CONFIG]

# 时钟CLK_CONFIG的下降沿过渡时间为0.12ns

set_clock_transition -fall 0.12 [get_clocks CLK_CONFIG]

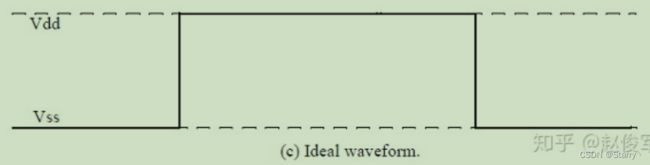

当然在实际仿真和分析中,经常直接使用如下图的理想波形进行时序分析,将电平转换时间近似成零。

2. 衍生时钟create_generated_clock

使用指定时钟(create_clock指令产生的时钟)经过MMCM/PLL/BUFR产生的时钟、或者是用户自行设计出来的时钟,需要约束衍生时钟create_generated_clock

4.1 Verilog 同步与异步

深度解析Create_clock与Create_generated_clock的区别

指令如下

# 名称: CLKP

# 周期: 10ns

# 占空比: 50%

# 端口: UPLL0/CLKOUT

create_clock -name CLKP -period 10 [get_pins UPLL0/CLKOUT]

# 名称: CLKPDIV2

# 源时钟: UPPL0/CLKOUT

# 分频系数: 2

# 端口: UFF0/Q

create_generated_clock -name CLKPDIV2 -source [get_pins UPLL0/CLKOUT] -divide_by 2 [get_pins UFF0/Q]

如果衍生时钟有多个源,则需要指定哪个是源时钟。

3. 划定时钟域set_clock_groups

静态时序分析—set_clock_groups

可将多个时钟分成多个组,通常时钟组之间为异步的。

# CLKA和CLKB为同步时钟,且与CLKC异步

set_clock_groups -asynchronous -group {CLKA CLKB} -group {CLKC}

# CLKA和CLKB为同步时钟,且与CLKC以及CLKC的衍生时钟 异步

set_clock_groups -asynchronous -group {CLKA CLKB} -group {[get_clocks -include_generated_clocks CLKC]}

如果两个时钟无需进行STA,但两个时钟都来自同一根线,就需要进行逻辑隔离,如下图

# C1和C2为来自同一根线,但相互之间不需要STA

set_clock_groups -logically_exclusive -group C1 -group C2

如果两个时钟需要进行STA,但两个时钟都来自同一根线,就需要进行逻辑隔离,如下图