半导体存储器件原理概述

半导体存储器件原理概述

文章目录

- 半导体存储器件原理概述

-

- 1 RAM原理

-

- 1.1 SRAM

- 1.2 DRAM

-

- 1.2.1 分层组织

- 1.2.2 时序

- 1.2.3 内存条重要标识的识别

- 1.2.4 DRAM技术发展

- 2 ROM

-

- 2.1 PROM

- 2.2 EPROM

- 2.3 EEPROM

-

- 2.3.1 原理

-

- 2.3.1.1 写入(Program)操作

- 2.3.1.2 擦除(Erase)操作

- 2.3.1.3 读取(Read)操作

- 2.3.2 EEPROM、Nor Flash和Nand Flash

- 2.3.3 Flash存储单元

- 2.3.4 3D Flash

- 2.3.5 Nand Flash的缺陷和对应方法

- 参考

1 RAM原理

随机访问存储器(Random Access Memory, RAM)是一种能访问任意位置存储单元的半导体器件。

1.1 SRAM

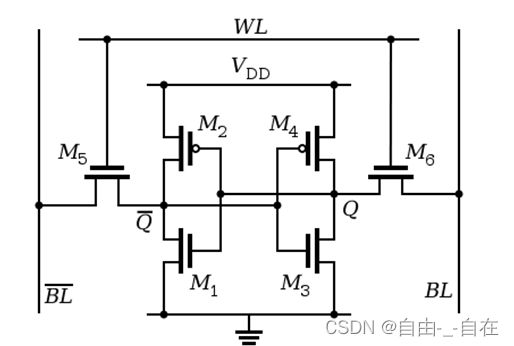

一个SRAM存储单元(存储一bit)由6个晶体管组成,其中4个场效应管(M1, M2, M3, M4)构成两个交叉耦合的反相器,另外两个场效应管(M5, M6)是存储基本单元到用于读写的位线的控制开关。利用晶体管的状态切换来存储数据,而不像电容器,因此读数据时不存在漏电问题,不需要刷新操作。但是由于SRAM需要的晶体管数多,因此成本高。其一般用做CPU的高速缓存。

1.2 DRAM

个DRAM存储单元由1个晶体管和1个电容器组成,利用电容量存储电量的多少来存储数据,由于电容器存在漏电问题,因此需要定期刷新。读数据时,电容量的电量会消失,因此每次访问之后,也需要刷新,以防止数据丢失。

1.2.1 分层组织

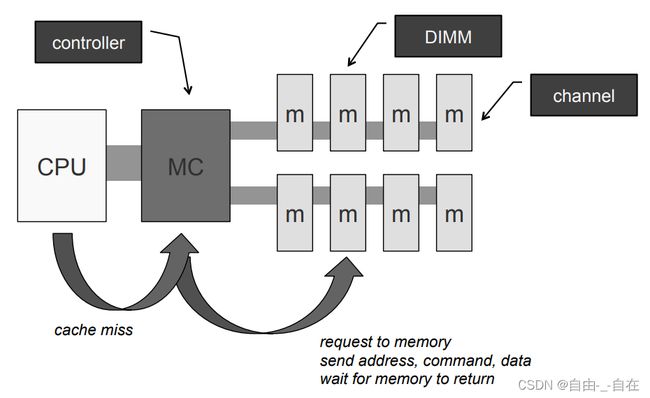

内存的分层组织如下:

-

内存控制器(memory controller):CPU直接与内存控制器进行通信;

-

通道(channel):一个内存控制器支持的通道数,由具体的内存控制器决定,一般都支持2~3个,通道之间的独立执行命令,互不干扰,因此通道数量表现了内存控制器并行处理的能力;

-

双列直插式存储模块(dual In-line memory module,DIMM):内存芯片的独立模组,指内存芯片被组织在一块独立的PCB上,并按DIMM形式的硬件接口与channel相连,因此DIMM实际上是内存条的封装形式;

-

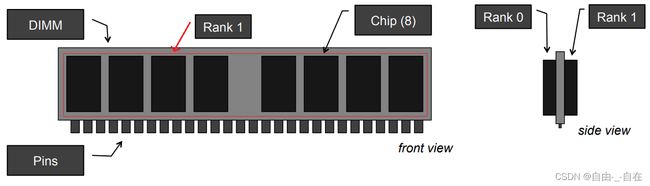

rank:rank是一块使用DIMM上部分或全部内存芯片(chips)所组成的内存区域,同一rank内的chips共享片选信号,而同一channel内的rank共享地址/命令信号。rank典型的位宽为64bit(与CPU一次处理的最大bit一致),带校验为72bit。DIMM上可能存在1、2或4个rank,被称为1-rank、2-rank或4-rank,在内存条上一般能看到1Rx4、2Rx4或2Rx8,这里的1R或2R就是指内存条上存在的rank数量,如图3展示了2Rx8的内存条;

-

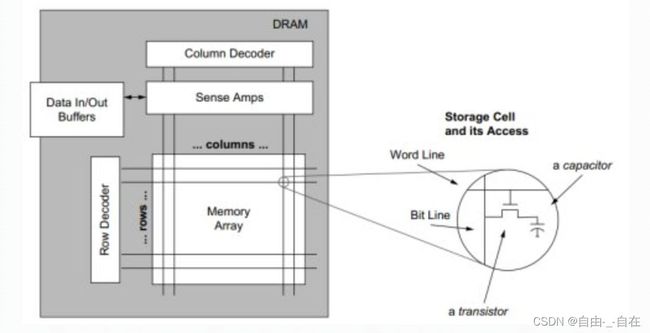

chip:DIMM/rank中独立的内存芯片,每个芯片内部都由n个bank组成,如图4;

-

bank:芯片内可独立访问的bit分区。rank提到的1Rx4中的x4就表示chip内bank的数量为4。bank按(row, col)将cell组织成矩阵的形式,如图5。对于bank而言一次读或写只能操作1bit数据;

-

元格(cell):存储1bit数据的存储单元。电路如图,其中字线(word line)控制晶体管的导通,位线(bit line)是访问存储电容的通道,可对其进行读取或写入操作。字线也被称为行地址线,位线也被称为列地址线。

1.2.2 时序

内存执行读写命令都有一定的步骤,而完成每个步骤都有相应的时延。

重要概念:

- Column Address Strobe:列地址选通脉冲

- Row Address Strobe:行地址选通脉冲

针对cell,具体有如下几个步骤:

- precharge:将位线上的电压保持在Vcc/2上,方便导通后感知电容电压;

- access:控制字线使得晶体管导通,拉升(逻辑1)或降低(逻辑0)位线上的电压;

- sense:由于位线电压过低并不能被正确感知,因此需要经过感知放大电路进行放大;

- restore:原存储电容逻辑为1的情况下,由于存储电容的电量经过上述过程不断流失,此时位线拉升至Vcc为存储电容充电,恢复其放电前的状态;原存储电容逻辑为0的情况下,由于存储电容的电量经过上述过程不断充电,此时位线拉升至0v为存储电容放电,恢复其放电前的状态。

- write recovery(写入独有):将数据写入时,若存储电容原为逻辑1,需要写入逻辑0,则将位线拉低至0v使其放电;若存储电容原为逻辑0,需要写入逻辑1,则将位线拉低至Vcc使其充电。

针对IMC(integrated memory controller,集成存储器控制器),常见有如下命令:

- active:将行地址通过地址线发送给SDRAM,然后其导通bank中的指定行,即控制字线;

- Read:将读取的列地址通过地址线发送给SDRAM,然后其在选通的行中将对应的列数据发送给host;

- Write:将写入的列地址通过地址线发送给SDRAM,将写入的数据通过数据线发送给SDRAM,其将数据再写入指定位置;

- Precharge:该操作以bank为单位进行,可对某一个bank进行,也可针对所有bank进行;

- Auto-Refresh:在一个刷新周期内就需要完成一次所有row的刷新操作,这要求host在刷新周期内必须对SDRAM发出一次Auto-Refresh指令;

- Self-Refresh:Host让SDRAM进入自刷新模式,降低功耗;

重要时序:

- tRCD = (access + sense):RAS to CAS Delay,即行地址选通脉冲后到可执行列地址选通脉冲的时延

- tCL 即CAS Latency:读取命令发出后到DRAM输出寄存器的间隔时间。

- tCWL 即Column Write Latency:写入命令发出后需要等待tCWL的时间才可以发送待写入的数据,一般与tCL保持一致。

- tRAS = (access + sense + restore 或 access + sense + restore + write recovery):RAS Active Time,内存每完成一个行、列地址激活操作到读写完成的全部时间。在受到access命令tRAS后,可进行precharge。

- tRP = (precharge) :RAS Precharge Time,RAS预充电时间,为下次读取或写入做准备。

- tCR 即Command Rate:首命令延迟是指从选定bank之后到可以发出行地址激活命令所经过的时间。

- tWR 即Write Recovery Latency:内存写入恢复时间,它定义了内存从写入命令发出(从开始写入算起)到下一次预充电间隔的时间,也就是tRP的前一个操作。

1.2.3 内存条重要标识的识别

示例:

8G 2Rx8 18-22-22-42

含义:

- 8G:内存的标称容量

- 2R:有2个rank

- x8:内存芯片含有8个bank

- 18:tCL

- 22:tRCD

- 22:tRP

- 42:tRAS

1.2.4 DRAM技术发展

- SDRAM(Synchronous DRAM)同步动态随机存储:host(IMC集成内存控制器)将提供给SDRAM同步时钟;

- SDR SDRAM(Single Data Rate SDRAM)单倍速率同步动态随机存储器:该技术只在时钟的上升沿传输数据;

- DDR SDRAM(Double Data Rate SDRAM)双倍速率同步动态随机存储器:该技术只在时钟的上升沿传输命令字段,而数据可在上升沿和下降沿同时传输。并采用prefetch技术(2n),提高DRAM内部一次IO的容量;

- DDR2 SDRAM(Double Data Rate 2 SDRAM)双倍速率2代同步动态随机存储器:在DDR基础上提升prefetch(4n);

- DDR3 SDRAM(Double Data Rate 3 SDRAM)双倍速率3代同步动态随机存储器:在DDR2基础上提升prefetch(8n);

- DDR4 SDRAM(Double Data Rate 3 SDRAM)双倍速率4代同步动态随机存储器:在DDR2基础上保持prefetch(8n),但提升了工作频率;

2 ROM

ROM是Read Only Memory的缩写,最开始的由来是因为其一旦被写入数据就是永久的,不能被删除。后来随着技术地不断发展,ROM也能被重复使用。

2.1 PROM

PROM是可编程只读存储器(Programmable Read Only Memory)的缩写。其生产出来时,所有位都表示1,如果某个位应该是0,我们可以通过燃烧使其为0。PROM的一个主要缺点是不可能更新它。换句话说,我们无法重新编程。相反,我们必须丢弃它,用一个新的芯片取而代之。

2.2 EPROM

EPROM是可擦可编程只读存储器(Erasable Programmable Read Only Memory)的缩写。我们可以擦除并重新编程EPROM而不用更换它。将存储芯片暴露在紫外线下,就可以对其进行擦除和写入操作。此外,通过封装顶部的透明熔融石英窗口更容易识别出EPROM。

2.3 EEPROM

EEPROM是电可擦可编程只读存储器( Electrically Erasable Programmable Read-Only Memory)的缩写。这是一种我们可以用电荷擦除和重新编程的记忆芯片。它由一组浮动栅晶体管组成。闪存(Flash)是EEPROM的一种,具有较高的密度和较低的写周期数。

2.3.1 原理

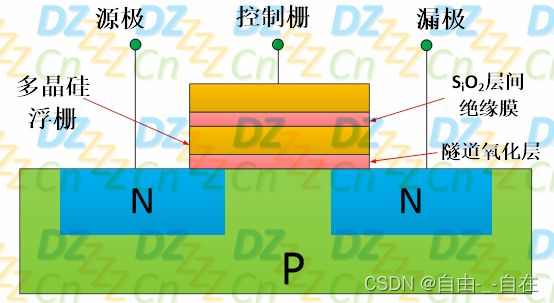

EEPROM一般采用FLOTOX(Floating Gate Tunneling Oxide)MOS管结构,即浮栅隧道氧化层晶体管,如下图:

多晶硅浮栅周围的氧化层与绝缘层将其与各电极相互隔离,这些氧化物的电阻非常高,而且电子从浮栅的导带向周围氧化物导带的移动需要克服较高的势叠,因此,浮栅中的电子泄漏速度很慢,在非热平衡的亚稳态下可保持数十年。多晶硅保存的电子就是我们需要存储的数据。

浮栅延长区的下方有个薄氧区小窗口,在外加强电场的作用下漏极与浮栅之间可以进行双向电子流动,继而达到对存储单元的“擦除”与“写入”操作。

flash是通过cell的导通状态决定其值是1还是0的,具体关系如下:

- 1:读其值时,其cell为非导通状态,表明该cell未执行过写入操作,即未保存电子;

- 0:读其值时,其cell为非导通状态,表明该cell执行过写入操作,即保存了电子。

具体原理可见,读取2.3.1.3操作部分。

2.3.1.1 写入(Program)操作

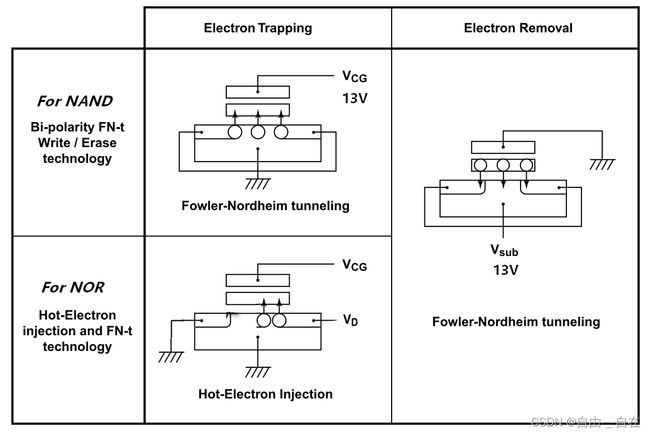

写入操作就是向浮栅注入电荷的过程,常用有两种技术给三端器件注入电子:

-

热电子注入(hot electron injection):源极接地,漏极和栅极接高电平,VCG >= VD ,热电子被水平偏置电压加速,到达漏极附近拥有更高的电势的耗尽区域。当这些电子得到足够能量足以超过衬底和门氧化层之间的能量势垒3.2 eV时,由于加在门氧化层两侧的Vd ,它们能够被注入门氧化层中,当一个高的正向电势 Vcg 被加载于控制门极时,这些电子被吸引到了浮栅区中。热电子注入模式工作电压较低,但编程电流很大,有较大的功耗,且写入速度慢。

-

F-N隧道效应(Fowler Nordheim tunneling):漏极和源极接地,栅极接高电平(一般为+12V),直接在浮栅与漏极之间形成正向强电场,电子从漏极通过隧道氧化层进入浮栅。F-N隧道效应工作电压高,但编程电流很小,功耗小,且写入速度快。

2.3.1.2 擦除(Erase)操作

写入操作就是移除浮栅中电荷的过程,一般利用F-N隧道效应。漏极和源极接地,栅极接负的高电平(一般为-12V),直接在浮栅与漏极之间形成反向强电场,电子从浮栅通过隧道氧化层进入漏极。

2.3.1.3 读取(Read)操作

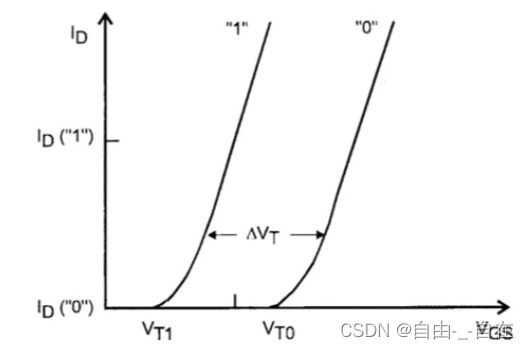

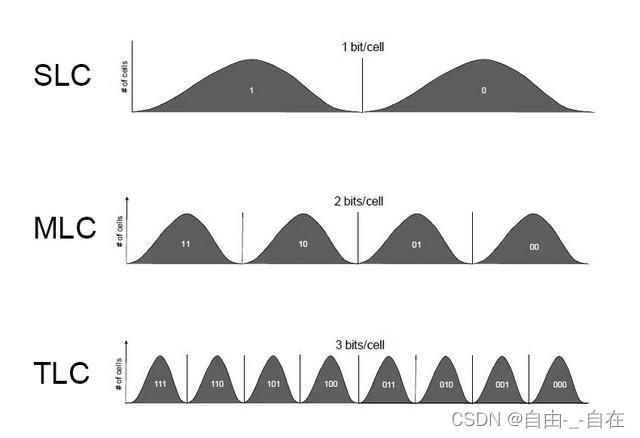

三端器件在浮栅注入电荷后,使漏极和源极之间导通需要给栅极更大的电压,如图3。VT0为浮栅注入电荷后,使三端器件导通的最低电压;而VT1则为未注入电荷时,使其导通的最低电压。在进行读取操作时,会给定一个介于两者间的电压VRead,若导通,则浮栅没有电荷,为逻辑“1”;若未导通,则浮栅有电荷,为逻辑“0”。这里是以三端器件的开闭状态来决定是逻辑1还是逻辑0,开态对应逻辑1,闭态对应逻辑0。

2.3.2 EEPROM、Nor Flash和Nand Flash

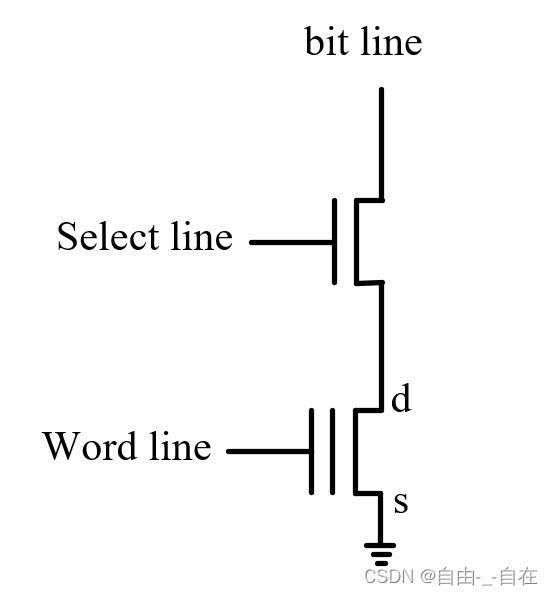

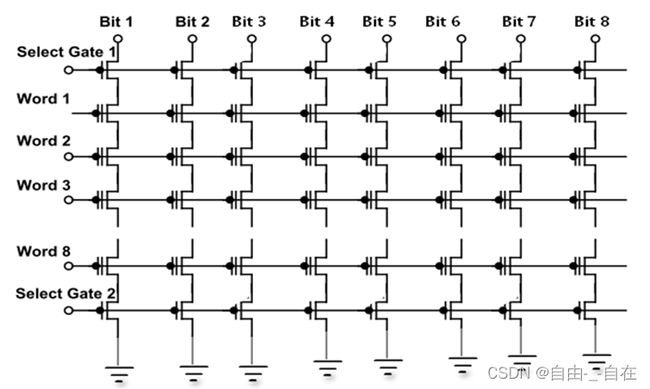

- EEPROM:其存储单元一般由两个场效应管组成,一个作为选通器,一个用三端器件做为存储器使用,如图4。选通器的存在,使得我们可以对任意bit进行擦除或写入操作,因此真正的EEPROM可以随机访问和修改任意一个字节,因此可以直接存储在运行状态的程序代码。但是其单位成本高昂,所以EEPROM的大小几乎不超过1M。

-

Flash:闪存的由来是因其按存储单元按块组织,且能在一瞬间被删除而得来。Nor Flash和Nand Flash的擦除操作一致,将一块存储单元内的所有word line偏置负电压,将浮栅上的电荷释放掉,擦除过程就完成了。

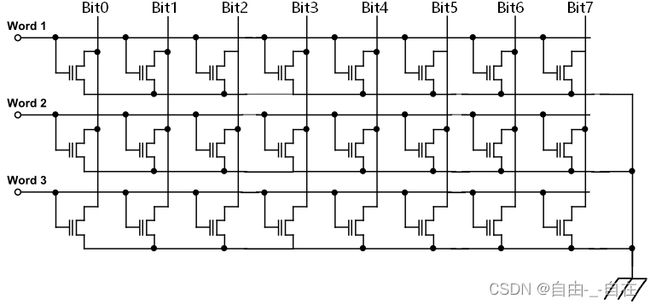

- Nor Flash:同一bit下的存储单元的漏极与位线相连,漏极与地相连,是一种典型的并联结构。特性:(1)当任意word被选中后,就可实现对应存储单元的读取,因此Nor flash具有随机访问并且读取效率高的特性;(2)并联结构占用面积大,存储密度低,不适合大容量存储;(3)写入采用热电子注入方式(word line和bit line偏置正电压),效率低,写入速度慢,不适合频繁写入的场合;

- Nand Flash:同一bit line下的存储单元源极和另一存储单元的漏极相连,是一种串联的结构。当需要读取数据时,将除读取页对应的word line之外的word line置高电平使其导通,这样bit line读取到的数据就取决于读取页中存储单元的导通与否。当要执行写入操作时,需要对写入bit的word line置强正电压,其它word line和其它bit line置低正电压,写入的bit line置 GND,每次写入单个bit花销巨大,因此一般都是写入整个word line上的bit,即按页写入。特性:(1)串联结构决定无法按位读取,因此只能按页读取,按块擦除;(2)串联结构占用面积小,存储密度高,适合大容量存储;(3)写入采用F-N隧道效应注入方式(word line偏置正电压),效率高,写入速度快,适合频繁写入的场合;

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-LazBnd1X-1652194510305)(nand-flash-unit.png)]

Nand Flash芯片内部存储组织结构:

- 一个芯片有若干个die(或LUN)

- 一个die有若干个plane(区域)

- 一个plane有若干个block

- 一个block有若干个page

- 一个page由成千上万个存储单元组成(一般为4KB内存+218B ECC校验),这些存储单元共用一个word line

其中,DIE是芯片接收和执行命令的基本单元;而每个plane都有自己独立的Cache/Page寄存器,其大小为一个Page的大小;Page为Flash读写的基本单位;block是Flash擦除的基本单位,这是因为同一个block中的存储单元是共用一个衬底,当对衬底施加强电压,则上面所有浮栅中的电子都被擦除了。

2.3.3 Flash存储单元

最开始Flash的一个存储单元仅能存储一bit的数据,该存储单元被称为SLC,即Single level cell。我们通过图3知道,存储单元的逻辑值是通过给栅极一个在阈值电压[VT1,VT2]范围内的电压,然后根据三端器件是否导通决定的。而阈值电压是根据浮栅内的电荷数量决定,当我们能够精确控制电荷注入的数量,那么我们就能得到多个阈值电压,如MLC(Multi level cell)有3个阈值电压,其能存储2bit,TLC(Triple level cell)有7个阈值电压能存储3bit,而QLC(Quad level cell)有15个阈值电压能存储4bit。

2.3.4 3D Flash

传统Flash存储芯片中的存储单元都是集成在2D平面,而3D Flash则是像建楼房一样,将存储单元一层层堆叠起来,因此就有了16 层, 32层,64层,128层3D Flash。

2.3.5 Nand Flash的缺陷和对应方法

缺陷:

-

存储数据有效期:浮栅注入电荷后仍会慢慢逃逸出去,一般定义电荷量减小到初始值的50% 时,就称为数据丢失。SSD存入数据后大概10年才会数据丢失,当然频繁擦除后这个时间会缩短。

-

PE(Program/Earse)次数限制:擦除、写入过程中浮栅下介电层里的化学键退化,导致介电作用减弱,数据保存的时间越来越短,直到最终不能使用。

-

读写干扰:读时会对block中除读Page外的其它页的word line施加电压,这会对其它Page存储单元中的电荷有轻微的影响;写时,会对本Page施加强电压,因此会对本Page未写入的存储单元和临近存储单元造成影响。

-

按页写入、按块擦除:因为Nand Flash是按照存储单元串联的制造工艺,造成block中的存储单元共用衬底,擦除时是对衬底施加强电压;page中的存储单元共用word line,写入时对word lone施加强电压。

方法:

- EDC(Error Detection Code)/ECC(Error Code Correction, 或者 Error Checking and Correcting):存储单元中的电荷会因为漂移效应,导致cell中的电压值改变,从而使得存储单元中存储的位变化;另一种情况是在读或写的时候,由于干扰导致电荷发生改变。这两种情况造成的位反转(bit reversal)可以通过校验解决,存储校验值的区域称为OOB(Out Of Band)。

- 闪存转换层(Flash Translateion Layer, FTL):因此制造工艺的原因存在一些天然的坏块造成可用的物理地址不连续,为了给上层使用的用户提供连续的地址空间,设置了FTL。其给上层用户提供连续的逻辑地址,对下将其映射到实际的物理地址。

- 异处更新(out-of-place Update):对于磁盘而言,修改数据时可直接将扇区上的原数据覆写即可。而对flash而言,需要将block擦除后,再重新写入,这被称为Erase Before Overwrite。如block的大小为512KB,而修改的数据为4KB,则需要规定写惩罚倍数为512/4 = 128。因此SSD采用异处更新的方式,即某一Page已有数据,下次再对该Page有写入操作时,会将数据写入另外的Page,同时改变逻辑地址到物理地址的映射,并设置之前Page的数据为无效数据。

- 磨损均衡(Wear leveling):因为block擦除的次数是有限的,频繁对一些block进行擦除,则整个SSD就会快速报废,因此需要采用算法将擦除操作尽量平均到所有的块上,以延长SSD的寿命。

- 垃圾回收(Garbage Collection,GC):因为异处更新导致block上并不全是有效数据,当无效数据增多就会占据大量的可用存储空间,因此需要通过GC将几个block的有效数据搬运至新的block中,并将原有的block进行擦除,以备新的数据写入。

参考

彻底讲投内存超频-理论片

DRAM 原理

图解内存的工作原理及时序介绍

存储器分类

内存控制器和cpu的问题

Memory中的Channel/Rank/Bank解析

内存时序

EEPROM工作原理

Nand基本原理

的Channel/Rank/Bank解析](https://blog.csdn.net/miaomao1989/article/details/51508195/)

内存时序

EEPROM工作原理

Nand基本原理