电工学复习【9】-- 触发器和时序逻辑电路

Sd非和Rd非都是输入端,Q和Q非都是输出端

被遮住的部分:可能是0

Rd非是直接置零端,如果输入的Rd = 0,则Rd非为1,此时输出结果会被强制置零

Sd非是直接置一端,如果输入的Sd = 0,则Sd非为1,此时输出结果会被强制置一

高电平就可以看作输入是 1

低电平就可以看作输入是0

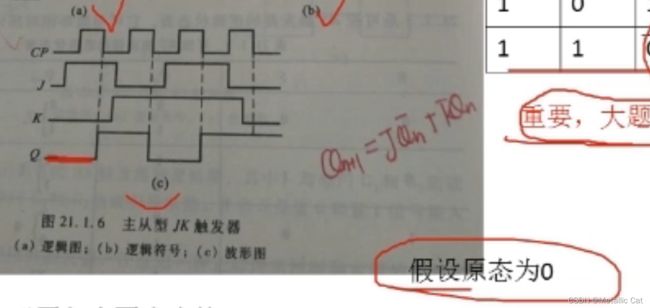

jk触发器只在时钟脉冲的下降沿触发

主从型jk触发器的状态表必须得背下来

画上面输出Q波形图的画法:

1.将时钟脉冲的所有下降沿用虚线延长到输出Q所在的波形图处(如上图)

2.根据下降沿上J 和 K的波形图处于原态还是上升沿,以及我们背下来的JK触发器的输入输出表来判断此时Q应该是上升,下降还是保持不变

3.判断完状态后,Q的状态会持续到下一次下降沿判断为止

D触发器 --- 上升沿触发

所以在画Q这个输出电压的时候步骤依然同上,但是延长的线要从下降沿线变为上升沿线,且真值表也要替换为D触发器特有的真值表。

设初始状态是0的意思就是将输出Q初始值置为0,反应在波形图上就是Q的波形图一开始处于低电位状态

上面这个初始状态我们又称为原态,符号表示是Qn

上面这一道题的分析:

1.J ,K 触发器的J端/K端没有外来输入时默认为高电位,所以上题中的J触发器处于高电位

2.上面这个电路图中K端与Q端用电线相连,所以K端处的电位与Q端相同

3.通过上述分析我们直到J端由于一直没有外界输入所以一直处于高电位,而K端则与Q端电位相同(已知Q的初始状态Qn),有了上面这些要素后我们就能够画出Q的波形图了

21.1.3这道题首先我们要知道:

1.这道题中并没有给出Q的原态是多少,所以我们要分为两种情况来进行分析,分别是原态Qn = 0和 = 1 两种情况。

2.结合JK触发器的真值表我们就可以得知道两种情况下的Qn+1是多少

如果 两种情况下的Qn+1都等于 Qn非的话,那么我们认为该触发器具有计数功能

两种情况下 Qn+1 = 1/0 ---- 功能是置1/0

两种情况下 Qn+1 = Qn ---- 功能是保持

做题步骤1:列出控制端的逻辑表达式:

从电路图的右边的第一个触发器开始,分别写出其J端和K端的输入值等于多少,就和上面那张图一样来写

从右往左一步步走!!

上面这种J和K端无输入的方式被称为悬空输入,处于悬空输入状态的J端和K端默认处于高电位

写完时钟方程之后我们就要写状态表

ps:上面这个状态表第四列的Qo全都改成Ko

1.表的左边是时钟脉冲到来的次数,到来0次时我们认为输出的Q都处于初态,且初态等于0

时钟脉冲来一次其输出波形图就会发生翻转,从0变1,从1变0

2.横列第一列则是各个时钟方程排开,然后横列的最后一列则是电路图中从左往右各个JK触发器的输出值排列(如图)

3.首先Q0的值我们是知道的,它就是由时钟脉冲决定的,首先时钟脉冲等于0次时,Q0等于0,然后我们就可以得出Q1,Q2,Q3....等等其他的输出值,等于1次时,Q0=1,等于两次时Q0=0,就这样一直循环,一直求下去,直到我们遇到所有输出值都为0000的时候才停止

做完以上步骤之后我们需要做上面这个步骤

1.异/同步判断 ---- 如果每个JK触发器的时钟脉冲都是同一个时钟脉冲的话就是同步,否则就是异步,如下图这种就都是同一个时钟脉冲,所以是同步:

下面这种就是异步

2.几进制 --- 我们写出的真值表中时钟脉冲停在哪一个次数A,那么就是A进制

3./加减法计数器 --- 如果真值表中的输出结果是 000 , 001,010,011这样递增的话就是加法计数器,如果是 111 , 110 , 101 ...这样递减的话就是减法计数器

然后我们就要画时序图和波形图

1.画出时钟脉冲的波形图

然后又因为JK触发器下降沿触发,所以将下降沿以虚线的方式向下延长

沿长完后将所有输出结果按照输出的顺序将输出的结果按照从上到下的顺序写出

然后根据我们的真指表开始画出输出结果的波形图 --- 1为高位,0为低位(从高位到低位的变化点一定在下降沿处)

要记住悬空的都默认是 1 哦

异步计数器的处理和同步计数器一致

唯一有一点不同的是!!!! 异步计数器具有多个时钟脉冲,但是!!这多个时钟脉冲中一定有一个主脉冲,其他都是从脉冲

而当我们列真值表的时候左边第一列我们只列主脉冲

这里面CP就是主脉冲

从脉冲的值是根据从买从脉冲判断的,而JK触发器只有在输给它的时钟脉冲处于下降沿的时候才能够有输出值的改变

首先我们要知道主脉冲CP的波形图 --- 已知 0,1,0,1的变

然后是Q0的波形图 --- 由CP加JK触发器知道

然后Q0就等于中间那个JK触发的从时钟脉冲,此时我们再画从时钟脉冲的波形图

然后根据这个波形图画Q1的波形图,然后再画Q2的波形图,就是这样一个逻辑

这个波形图和我们前面那些波形图虽然长得不一样,但其实都是一个东西,按照上面那些步骤来分析就可以了。