Linux 网络驱动 嵌入式网络简介(一)

嵌入式的网络硬件接口

SOC 内部没有网络 MAC 外设

嵌入式网络硬件分为两个部分:MAC和PHY,一般查看数据手册来判断这款芯片是否有内置MAC,若有只需外接一个PHY芯片即可。

比如 S3C2440、S5PV210,4412 等都没有内置的MAC,所以这类开发板都是通过DM9000来完成有线网络功能的,还有些网络芯片更强大,内部集成了TCP/IP协议栈,对外提供一个SPI接口,比如W550内置了TCP/IP协议栈,虽然操作简单了,但是这类芯片网速不够快。

SOC与外部MAC+PHY芯片的连接如图

SOC 内部有网络 MAC 外设

一般通用的SOC都会集成网络MAC外设,比如STM32F4/F7/H7 系列、NXP 的 I.MX系列,内部集成网络 MAC 的优点如下:

1:内部 MAC 外设会有专用的加速模块,比如专用的 DMA,加速网速数据的处理。

2:网速快,可以支持 10/100/1000M 网速。

3:外接 PHY 可选择性多,成本低。

正点原子 ALPHA 开发板板载了两颗 PHY 芯片,型号为 LAN8720 或 SR8201F。

MII/RMII 接口

内部 MAC 通过 MII/RMII 接口来与外部的 PHY 芯片连接,完成网络数据传输。

MII 接口

MII 全称是 Media Independent Interface,直译过来就是介质独立接口,它是 IEEE-802.3 定

义的以太网标准接口,MII 接口用于以太网 MAC 连接 PHY 芯片,连接示意图如图 69.1.2.1 所

示:

MII 接口一共有 16 根信号线,含义如下:

TX_CLK :发送时钟,如果网速为 100M 的话时钟频率为 25MHz,10M 网速的话时钟频率

为 2.5MHz,此时钟由 PHY 产生并发送给 MAC。

TX_EN :发送使能信号。

TX_ER :发送错误信号,高电平有效,表示 TX_ER 有效期内传输的数据无效。10Mpbs 网

速下 TX_ER 不起作用。

TXD[3:0]:发送数据信号线,一共 4 根。

RXD[3:0] :接收数据信号线,一共 4 根。

RX_CLK :接收时钟信号,如果网速为 100M 的话时钟频率为 25MHz,10M 网速的话时钟

频率为 2.5MHz,RX_CLK 也是由 PHY 产生的。

RX_ER :接收错误信号,高电平有效,表示 RX_ER 有效期内传输的数据无效。10Mpbs 网

速下 RX_ER 不起作用。

RX_DV :接收数据有效,作用类似 TX_EN。

CRS :载波侦听信号。

COL :冲突检测信号。

MII 接口的缺点就是所需信号线太多,这还没有算 MDIO 和 MDC 这两根管理接口的数据

线,因此 MII 接口使用已经越来越少了

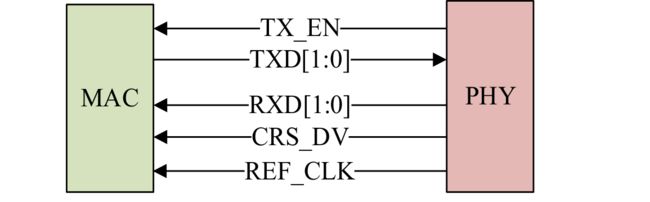

RMII 接口

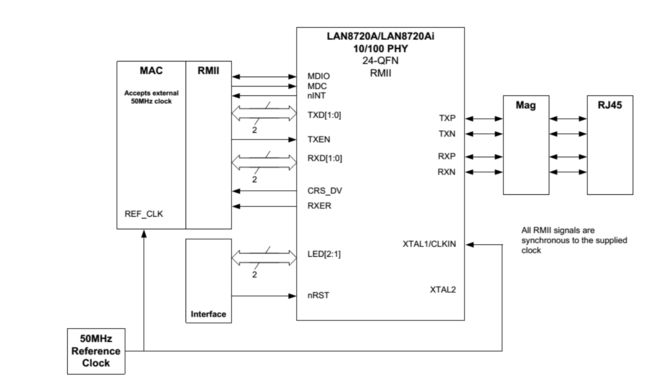

RMII 全称是 Reduced Media Independent Interface,翻译过来就是精简的介质独立接口,也就是 MII 接口的精简版本。RMII 接口只需要 7 根数据线,相比 MII 直接减少了 9 根,极大的方便了板子布线,RMII 接口连接 PHY 芯片的示意图如图

TX_EN :发送使能信号。

TXD[1:0] :发送数据信号线,一共 2 根。

RXD[1:0]:接收数据信号线,一共 2 根。

CRS_DV :相当于 MII 接口中的 RX_DV 和 CRS 这两个信号的混合。

REF_CLK :参考时钟,由外部时钟源提供, 频率为 50MHz。这里与 MII 不同,MII 的接

收和发送时钟是独立分开的,而且都是由 PHY 芯片提供的。

MDIO 接口

MDIO 全称是 Management Data Input/Output,直译过来就是管理数据输入输出接口,是一个简单的两线串行接口,一根 MDIO 数据线,一根 MDC 时钟线。驱动程序可以通过 MDIO 和MDC 这两根线访问 PHY 芯片的任意一个寄存器。MDIO 接口支持多达 32 个 PHY。同一时刻内只能对一个 PHY 进行操作,那么如何区分这 32 个 PHY 芯片呢?和 IIC 一样,使用器件地址即可。同一 MDIO 接口下的所有 PHY 芯片,其器件地址不能冲突,必须保证唯一,具体器件地址值要查阅相应的 PHY 数据手册

RJ45 接口

网络设备是通过网线连接起来的,插入网线的叫做 RJ45 座,RJ45 座要与 PHY 芯片连接在一起,但是中间需要一个网络变压器,网络变压器用于隔离,以及滤波等,网络变压器也是一个芯片,但是现在很多 RJ45 座子内部已经集成了网络变压器,RJ45 座子上一般有两个灯,一个黄色(橙色),一个绿色,绿色亮的话表示网络连接正常,黄色闪烁的话说明当前正在进行网络通信。这两个灯由 PHY 芯片控制,PHY 芯片会有两个引脚来连接 RJ45 座上的这两个灯,内部 MAC+外部 PHY+RJ45 座(内置网络变压器)就组成了一个完整的嵌入式网络接口硬件,如图 所示

I.MX6ULL ENET 接口简介

I.MX6ULL 有两个网络接口,也就是两个 MAC 外设,一个 MAC 连接一个 PHY 芯片形成一个完整网络接口,本节我们简单了解一下 I.MX6ULL 自带的 ENET 接口。I.MX6ULL 内部自带的 ENET 外设其实就是一个网络 MAC,支持 10/100M。实现了三层网络加速,用于加速那些通用的网络协议,比如 IP、TCP、UDP 和 ICMP 等,为客户端应用程序提供加速服务。I.MX6ULL 内核集成了两个 10/100Mbit/S 的网络 MAC,符合 IEEE802.3-2002 标准,MAC层支持双工、半双工局域网。MAC 可编程、可以作为 NIC 卡或其他一些交换器件。根据 IETFRFC 2819 协议,MAC 实现了 RMON(Remote Network Monitoring)计数功能。MAC 内核拥有硬件加速处理单元来提高网络性能,硬件加速单元用于处理 TCP/IP、UDP、ICMP 等协议。通过硬件来处理帧头等信息,效果要比用一大堆软件处理要好很多。ENET 外设有一个专用的 DMA,此 DMA 用于在 ENET 外设和 SOC 之间传输数据,并且支持可编程的增强型的缓冲描述符,用以支持 IEEE 1588。

I.MX6ULL 内部 ENET 外设主要特性如下:

1)、实现了全功能的 802.3 规范前导码/SFD 生成、帧填充、CRC 生成和检查。

2)、支持零长的前导码。

3)、支持 10/100M 动态配置。

4)、兼容 AMD 远端节点电源管理的魔术帧中断检测。

5)、可以通过如下接口无缝的连接 PHY 芯片:

·4bit 的 MII 接口,频率为 2.5/25MHz。

·4bit 的 MII-Lite 接口,也就是 MII 接口取消掉 CRS 和 COL 这两根线,频率也是

2.5/25MHz。

·2bit 的 RMII 接口,频率为 50MHz。

6)、MAC 地址可编程。

7)、多播和单播地址过滤,降低更高层的处理负担。

8)、MDIO 主接口,用于管理和配置 PHY 设备。

……

I.MX6ULL 的 ENET 外设内容比较多,详细的介绍请查阅《I.MX6ULL 参考手册》的“Chapter

22 10/100-Mbps Ethernet MAC(ENET)”章节。我们在编写驱动的时候其实并不需要关注 ENET

外设的具体内容,因为这部分驱动是 SOC 厂商编写的,我们重点关注的是更换 PHY 芯片以后

哪里需要调整

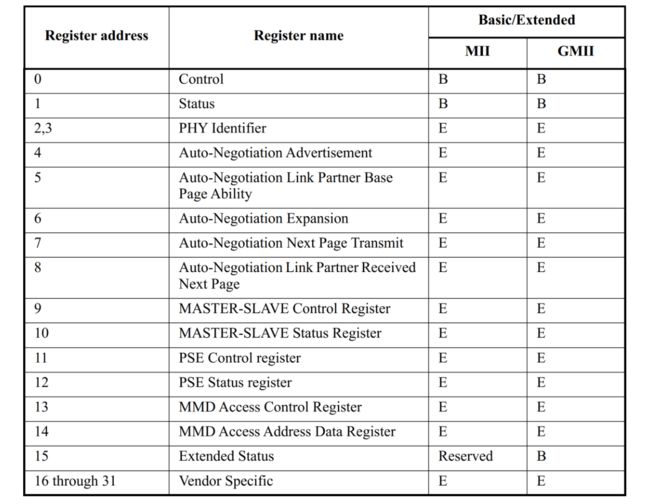

PHY芯片详解

PHY 是 IEEE 802.3 规定的一个标准模块,前面说了,SOC 可以对 PHY 进行配置或者读取PHY 相关状态,这个就需要 PHY 内部寄存器去实现了。PHY 芯片寄存器地址空间为 5 位,地址 0~31 共 32 个寄存器,IEEE 定义了 0~15 这 16 个寄存器的功能,16~31 这 16 个寄存器由厂商自行实现。也就是说不管你用的哪个厂家的 PHY 芯片,其中 0~15 这 16 个寄存器是一模一样的。仅靠这 16 个寄存器是完全可以驱动起 PHY 芯片的,至少能保证基本的网络数据通信,因此 Linux 内核有通用 PHY 驱动,按道理来讲,不管你使用的哪个厂家的 PHY 芯片,都可以使用 Linux 的这个通用 PHY 驱动来验证网络工作是否正常。事实上在实际开发中可能会遇到一些其他的问题导致 Linux 内核的通用 PHY 驱动工作不正常,这个时候就需要驱动开发人员去调试了。但是,随着现在的 PHY 芯片性能越来越强大,32 个寄存器可能满足不了厂商的需求,因此很多厂商采用分页技术来扩展寄存器地址空间,以求定义更多的寄存器。这些多出来的寄存器可以用于实现厂商特有的一些技术,因此 Linux 内核的通用 PHY 驱动就无法驱动这些特色

功能了,这个时候就需要 PHY 厂商提供相应的驱动源码了,所以大家也会在 Linux 内核里面看到很多具体的 PHY 芯片驱动源码。不管你的 PHY 芯片有多少特色功能,按道理来讲,Linux 内核的通用 PHY 驱动是绝对可以让你这 PHY 芯片实现基本的网络通信,因此大家也不用担心更换 PHY 芯片以后网络驱动编写是不是会很复杂。

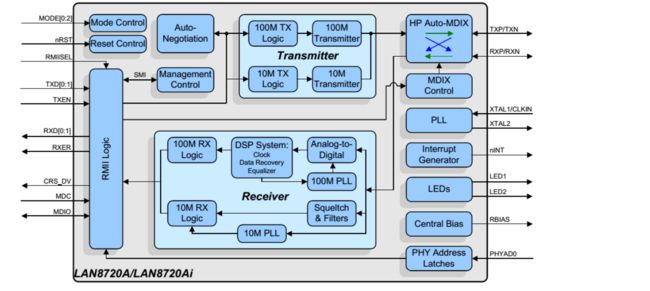

LAN8720A 详解

LAN8720A 简介

LAN8720A 是低功耗的 10/100M 单以太网 PHY 层芯片,可应用于机顶盒、网络打印机、嵌入式通信设备、IP 电话等领域。I/O 引脚电压符合 IEEE802.3-2005 标准。LAN8720A 支持通过 RMII 接口与以太网 MAC 层通信,内置 10-BASE-T/100BASE-TX 全双工传输模块,支持10Mbps 和 100Mbps。LAN8720A 可以通过自协商的方式选择与目的主机最佳的连接方式(速度和双工模式)。支持 HP Auto-MDIX 自动翻转功能,无需更换网线即可将连接更改为直连或交叉连接。

LAN8720A 的主要特点如下:

· 高性能的 10/100M 以太网传输模块

· 支持 RMII 接口以减少引脚数

· 支持全双工和半双工模式

· 两个状态 LED 输出

· 可以使用 25M 晶振以降低成本

· 支持自协商模式

· 支持 HP Auto-MDIX 自动翻转功能

· 支持 SMI 串行管理接口

· 支持 MAC 接口

LAN8720A 功能框图如图所示:

LAN8720A 中断管理

LAN8720A 的器件管理接口支持非 IEEE 802.3 规范的中断功能。当一个中断事件发生并且相应事件的中断位使能,LAN8720A 就会在 nINT(14 脚)产生一个低电平有效的中断信号。LAN8720A 的中断系统提供两种中断模式:主中断模式和复用中断模式。主中断模式是默认中断模式,LAN8720A 上电或复位后就工作在主中断模式,当模式控制/状态寄存器(十进制地址为 17)的 ALTINT 位为 0 时 LAN8720A 工作在主模式,当 ALTINT 位为 1 时工作在复用中断模式。正点原子的 ALPHA 开发板虽然讲 LAN8720A 的中断引脚连接到了 I.MX6ULL 上,但是并没有使用中断功能,关于中断的具体用法可以参考 LAN8720A 数据手册的 29~30 页

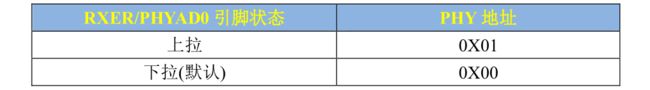

PHY 地址设置

MAC 层通过 MDIO/MDC 总线对 PHY 进行读写操作,MDIO 最多可以控制 32 个 PHY 芯

片,通过不同的 PHY 芯片地址来对不同的 PHY 操作。LAN8720A 通过设置 RXER/PHYAD0

引脚来设置其 PHY 地址,默认情况下为 0,其地址设置如图所示:

正点原子 ALPHA 开发板的 ENET1 网络的 LAN8720A 上的 RXER/PHYAD0 引脚为默认状态(原理图上有个 10K 下拉,但是没有焊接),因此 ENET1 上的 LAN8720A 地址为 0。ENET2网络上LAN8720A 上的 RXER/PHYAD0 引脚接了个 10K 上拉电阻,因此 ENET2 上的LAN8720A 地址为 1。

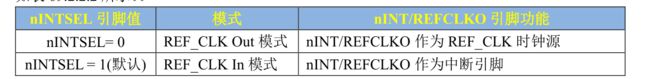

nINT/REFCLKO 配置

nINTSEL 引脚(2 号引脚)用于设置 nINT/REFCLKO 引脚(14 号引脚)的功能。nINTSEL 配置如表所示:

对于正点原子的 ALPHA 开发板的两个 LAN8720A 而言,全都工作在默认的 REF_CLK In 模式下。当 LAN8720A 工作在 REF_CLK In 模式时,50MHz 的外部时钟信号应接到 LAN8720 的XTAL1/CKIN 引脚(5 号引脚)上,如图所示:

为了降低成本,LAN8720A 可以从外部的 25MHz 的晶振中产生 REF_CLK 时钟。使用此功能时应工作在 REF_CLK Out 模式时。当工作在 REF_CLO Out 模式时 REF_CLK 的时钟源如图所示。

前面说了,正点原子的 ALPHA 开发板工作在 REF_CLK In 模式下,因此需要外部 50MHz时钟信号,I.MX6ULL 有专用的网络时钟引脚,因此 ALPHA 开发板是通过 I.MX6ULL 的ENET1_REF_CLK 和 ENET2_REF_CLK 这两个网络时钟引脚来为 LAN8720A 提供 50MHz 的时钟。

LAN8720A 内部寄存器

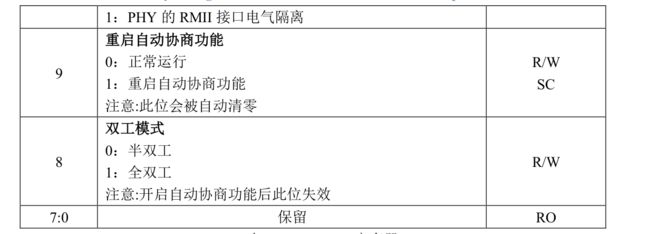

LAN8720A 的前 16 个寄存器满足 IEEE 的要求,在这里我们只介绍几个常用的寄存器,首先是 BCR(Basic Control Rgsister)寄存器,地址为 0,BCR 寄存器各位如表所示。

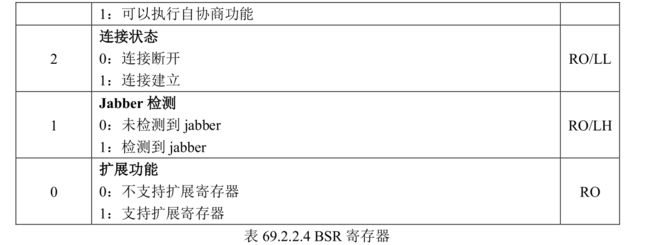

接下来看一下 BSR(Basic Status Register)寄存器,地址为 1。此寄存器为 PHY 的状态寄存

器,通过此寄存器可以获取到 PHY 芯片的工作状态,BSR 寄存器各位如表所示:

接下来看一下 LAN8720A 的 PHY ID 寄存器 1 和 ID 寄存器 2,地址为 2 和 3,后面就称为寄存器 2 和寄存器 3。这两个寄存器都是 PHY 的 ID 寄存器。IEEE 规定寄存器 2 和寄存器 3 为PHY 的 ID 寄存器,这两个寄存器组成一个 32 位的唯一 ID 值。IEEE 规定了一叫做 OUI 的 ID组成方式,全称是 Organizationally Unique Identifier,OUI 一共 32 位,分为三部分:22 位的 ID+6位厂商型号 ID+4 位厂商版本 ID,组成如图所示:

LAN8720A 的 ID 寄存器 2 如表所示:

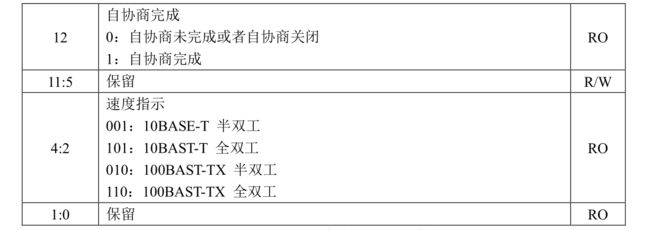

特殊控制/状态寄存器中我们关心的是 bit2~bit4 这三位,因为通过这 3 位来确定连接的状态

和速度,关于 LAN8720A 这个 PHY 就讲解到这里。