Intel64和IA-32架构软件开发者手册第1卷:基本架构

第1章-关于本手册。给出了英特尔®64和IA-32架构软件开发者手册的所有五卷的概述。它还描述了这些手册中的符号约定,并列出了程序员和硬件设计人员感兴趣的相关Intel手册和文档。

第2章- Intel®64和IA-32架构。介绍Intel 64和IA-32架构以及基于这些架构的Intel处理器系列。它还概述了这些处理器的常见特性,以及Intel 64和IA-32架构的简要历史。

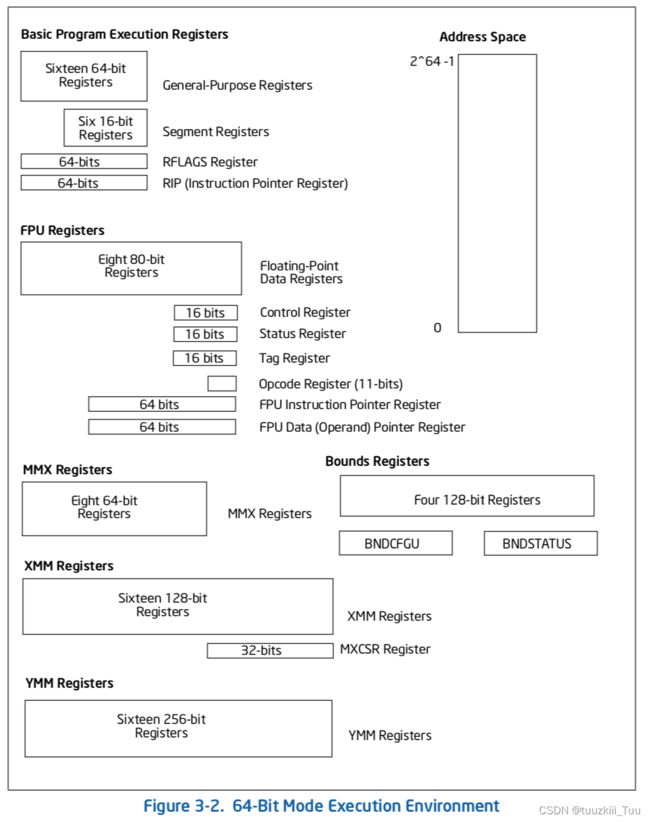

第3章-基本执行环境。介绍了内存组织的模型,并描述了应用程序使用的寄存器集。

第4章-数据类型。描述处理器识别的数据类型和寻址模式;提供实数和浮点格式以及浮点异常的概述。

第5章-指令集总结。列出所有Intel 64和IA-32指令,分为技术组。

第6章-过程调用、中断和异常。描述过程堆栈和机制用于进行过程调用以及处理中断和异常。

第7章-使用通用指令编程。描述在基本数据类型、通用regis和段regis上操作的基本加载和存储、程序控制、算术和字符串指令;还描述在保护模式下执行的系统指令。

第8章- x87 FPU编程。介绍x87浮点单元(FPU),包括浮点寄存器和数据类型;概述了浮点指令集,并描述了处理器的浮点异常条件。

第9章-使用Intel®MMXTM技术编程。描述Intel MMX技术,包括MMX寄存器和数据类型;还提供了MMX指令集的概述。

第10章-使用Intel®Streaming SIMD Extensions (Intel®SSE)编程。描述SSE扩展,包括XMM寄存器、MXCSR寄存器和打包的单精度浮点数据类型;提供了SSE指令集的概述,并提供了编写访问SSE扩展的代码的指导方针。

第11章-使用Intel®Streaming SIMD Extensions 2 (Intel®SSE2)进行编程。描述SSE2扩展,包括XMM寄存器和打包的双精度浮点数据类型;提供了SSE2指令集的概述,并提供了访问SSE2扩展的代码编写指南。本章还描述了可以用SSE和SSE2指令生成的SIMD浮点异常。它还提供了将对SSE和SSE2扩展的支持合并到操作系统和应用程序代码中的一般指导方针。

第12章-使用Intel®Streaming SIMD Extensions 3 (Intel®SSE3)编程,补充流媒体SIMD扩展3 (SSSE3), Intel®流媒体SIMD扩展4 (Intel®SSE4)和Intel®AES新指令(Intel®AES- ni)。提供SSE3指令集、补充SSE3、SSE4、AESNI指令的概述,以及编写访问这些扩展的代码的指南。

第13章-使用XSAVE特性集管理状态。描述XSAVE特性集说明,并解释软件如何启用XSAVE特性集和启用XSAVE的特性。

第14章-使用AVX, FMA和AVX2编程。提供Intel®AVX指令集,FMA和Intel AVX2扩展的概述,并提供了访问这些扩展的代码编写指南。

第15章-使用Intel®AVX-512编程。提供Intel®AVX-512指令集扩展的概述,并给出了访问这些扩展的代码编写指南。

第16章-使用Intel事务性同步扩展进行编程。描述支持锁省略技术的指令扩展,以改进具有争用锁的多线程软件的性能。

第17章-英特尔®内存保护扩展。提供了英特尔®内存保护扩展的概述,并提供了访问这些扩展的代码编写指南。

第18章-控制流执行技术。提供控制流强制技术(CET)的概述,并提供编写访问这些扩展的代码的指导方针。

第19章-输入/输出。描述处理器的I/O机制,包括I/O端口寻址、I/O指令和I/O保护机制。

第20章-处理器识别和特征确定。描述如何确定处理器中可用的CPU类型和特性。

1.3.1 x86是小端存储

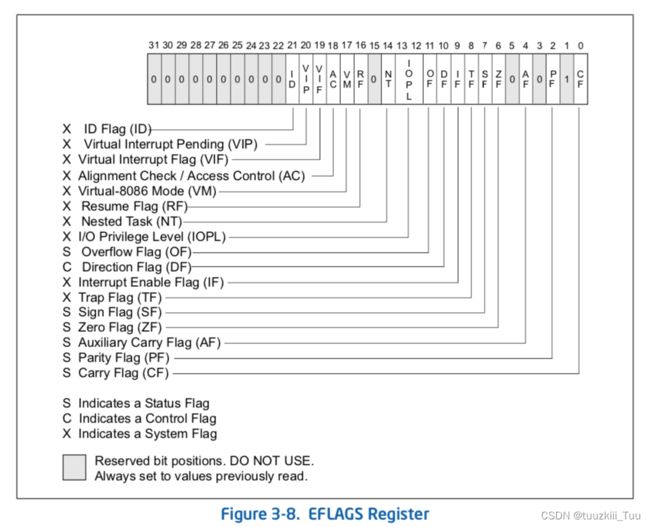

1.3.2 许多寄存器有保留位,但因为保留位是不确定的,在软件处理寄存器时不能考虑保留位

1.3.4 处理器使用字节寻址,也支持分段寻址

下面的段地址标识DS寄存器所指向的段中地址FF79H的字节:

DS: FF79H

下面的段地址标识代码段中的指令地址。CS寄存器指向代码段,EIP寄存器包含指令的地址。

CS: EIP

1.3.6 异常是指指令导致错误时通常发生的事件。某些类型的异常可能会提供错误代码。错误代码会报告有关该错误的附加信息。

用于显示异常和错误代码的符号示例如下: # PF(错误代码)

在某些情况下,产生错误代码的异常可能无法报告准确的代码。这种情况下,错误代码为零,如下所示为通用保护异常: # GP (0)

发展历程

1978--16位处理器,即8086和8088

1982--Intel286处理器,引入了保护模式操作,支持段交换基础上的虚拟内存管理

1985--Intel386TM处理器,第一个32位处理器

1989--Intel486TM处理器,增加了更多的并行执行能力

1993--Intel Pentium处理器,增加了第二个执行管道来实现超标量性能

1995-1999--P6系列处理器,基于超标量微架构,它设定了新的性能标准

2000-2006--Intel Pentium4处理器系列,

2001-2007--Intel Xeon 处理器

2003-2006--Intel Pentium M 处理器系列,高性能、低功耗的移动处理器

2005---Intel Pentium 处理器极致版,引入了双核技术。这种技术提供了高级的硬件多线程支持

2006-2007--Intel Core Duo和Intel Core Solo处理器

2006--Intel®Xeon®处理器5100、5300系列和Intel®Core2处理器家族

2008--Intel Atom®处理器系列,于一种新的微架构,Intel Atom®微架构

2013--基于Silvermont微架构的Intel Atom®处理器系列

2008-- Intel CoreTMi7处理器系列,支持Intel 64架构

2010--Intel®Xeon®处理器7500系列,基于Nehalem微架构

2010--Intel®CoreTM处理器系列,横跨英特尔酷睿i7, i5和i3处理器

....累了

3 基本执行环境

三种基本运行模式:

1 保护模式-这种模式是处理器的原生状态。保护模式的功能之一是能够在受保护的多任务环境中直接执行“实地址模式”8086软件。这个特性被称为virtual-8086模式,尽管它实际上并不是处理器模式。Virtual-8086模式实际上是一个受保护的模式属性,可以为任何任务启用。

2 实地址模式-该模式通过扩展实现了Intel 8086处理器的编程环境(例如切换到受保护或系统管理模式的能力)。在上电或复位后,处理器被置于实地址模式。

3 系统管理模式(SMM) -该模式为操作系统或执行人员提供了一种透明的机制,用于实现平台特定的功能,如电源管理和系统安全。当外部SMM中断引脚(SMI#)被激活或从高级可编程中断控制器(APIC)接收到SMI时,处理器进入SMM。

在SMM中,处理器切换到一个单独的地址空间,同时保存当前运行的程序或任务的基本上下文。smm特定的代码可以透明地执行。当从SMM返回时,处理器被放回到系统管理中断之前的状态。SMM是与Intel386TM SL和Intel486TM SL处理器一起引入的,并与奔腾处理器家族一起成为标准的IA-32功能。

在64位架构中,还有:

兼容性模式(IA-32e模式的子模式)—兼容性模式允许大多数遗留的16位和32位应用程序在64位操作系统下运行而无需重新编译。

兼容模式由操作系统(OS)在代码段的基础上启用。这意味着单个64位操作系统可以支持64位应用程序,并支持运行在兼容模式下的遗留32位应用程序(未重新编译为64位)。

兼容模式类似于32位的保护模式。应用程序只能访问线性地址空间的前4gbyte。兼容模式使用16位和32位的地址和操作数大小。与保护模式一样,这种模式允许应用程序使用物理地址扩展(PAE)访问大于4gbyte的物理内存。

关于运行时的基础资源:

•地址空间- 任何在IA-32处理器上运行的任务或程序都可以寻址一个高达4gbytes(232字节)的线性地址空间和一个高达64gbytes(236字节)的物理地址空间。参见第3.3.6节,“保护模式下的扩展物理寻址”,了解更多关于寻址大于4gbytes的地址空间的信息。

•基本程序执行寄存器- 八个通用寄存器、六个段寄存器、EFLAGS寄存器和EIP(指令指针)寄存器组成了一个基本的执行环境,在这个环境中可以执行一组通用指令。这些指令对字节、字和双字整数执行基本的整数算术,处理程序流控制,对位和字节字符串进行操作,并寻址内存。有关这些寄存器的更多信息,请参阅第3.4节“基本程序执行寄存器”。

•x87 FPU寄存器- 8个x87 FPU数据寄存器、x87 FPU控制寄存器、状态寄存器、x87 FPU指令指针寄存器、x87 FPU操作数(数据)指针寄存器、x87 FPU标签寄存器和x87 FPU操作码寄存器提供了一个执行环境,用于操作单精度、双精度和双扩展精度浮点值、字整数、双字整数、四字整数和二进制编码的十进制(BCD)值。有关这些寄存器的更多信息,请参见8.1节“x87 FPU执行环境”。

•MMX寄存器- 8个MMX寄存器支持在64位封装的字节、字和双字整数上执行单指令、多数据(SIMD)操作。有关这些寄存器的更多信息,请参见第9.2节“MMX技术编程环境”。

•XMM寄存器 - 8个XMM数据寄存器和MXCSR寄存器支持对128位封装的单精度和双精度浮点值以及128位封装的字节、字、双字和四字整数执行SIMD操作。有关这些寄存器的更多信息,请参见10.2节“SSE编程环境”。

•YMM寄存器 - YMM数据寄存器支持对256位封装的单精度和双精度浮点值以及对256位封装的字节、字、双字和四字整数执行256位SIMD操作。

•边界寄存器 -- 每个BND0-BND3寄存器都存储与指向内存缓冲区的指针相关的上下边界(各64位)。它们支持Intel MPX指令的执行。

•BNDCFGU和BNDSTATUS - BNDCFGU在边界检查上配置用户模式MPX操作。BNDSTATUS提供了MPX操作引起的#BR的附加信息。

•Stack - 为了支持过程或子例程调用和过程或子例程之间的参数传递,在执行环境中包含了堆栈和堆栈管理资源。栈位于内存中。有关堆栈结构的更多信息,请参见第6.2节“堆栈”。

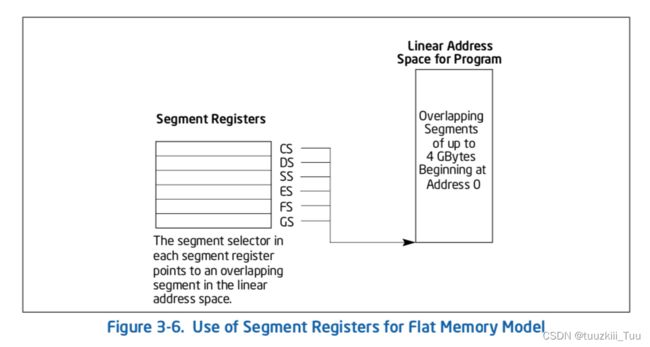

关于内存的组织

三种内存管理模式

1. 逻辑地址存的是物理地址

2. 逻辑地址存的是页号(段号)+偏移量,要先去查页号对应的物理段号,类似分页机制

3. 逻辑地址存的是页号(段号)+偏移量,页号直接就是物理段号

关于basic寄存器

• EAX — Accumulator for operands and results data 操作数和结果累加器

• EBX — Pointer to data in the DS segment 指向DS段中的数据的指针

• ECX — Counter for string and loop operations 用于字符串和循环操作的计数器

• EDX — I/O pointer

• ESI — Pointer to data in the segment pointed to by the DS register; source pointer for string operations 指向DS寄存器所指向的段中的数据的指针;字符串操作的源指针

• EDI — Pointer to data (or destination) in the segment pointed to by the ES register; destination pointer for string operations 指向ES寄存器所指向段中的数据的指针;目的指针字符串操作

• ESP — Stack pointer (in the SS segment)

• EBP — Pointer to data on the stack (in the SS segment)

段寄存器

EFLAGS寄存器

状态标志

数据类型