基于Xilinx Artix7的PCB设计总结

浅谈PCB设计

在这篇博客里笔者想把一些工作中积累的PCB设计知识以及Xilinx Artix7硬件设计要点分享出来,也许能为大家以后的工作带来一些帮助,利用下班时间笔者动手自己画了一块开发板焊接打样,把需要的硬件资源都扩展到一起如图1所示,这里面也有走了一些弯路和曲折,所以这篇博客主要用来总结和归纳。

谈到做PCB硬件设计,大家都明白要先做原理图,再画封装库,接着布局布线,最后投板焊接后回来调试,实际在工作中走过这个流程,都会对PCB设计有个整体上的大概了解,当然原件选型、阅读手册、电路搭建、电源设计、布局布线等等这些展开来说每一块都完全够写一本厚重的书了,所以这里我们就实际项目工程来简单谈一谈PCB设计,如何把我们的板子做得精致美观做得皮实耐用。

图1 DIY Artix7开发板外观

嵌入式工作中,有句耳熟能详的话:需求决定硬件,硬件决定软件。通常嵌入式产品在硬件上需要考虑很多方面,但批量PCB板后的成本是永远绕不开的话题,这就涉及到了SOC芯片选型、PCB层叠设计、外围电路的搭建等多个方面。举个现实工程的例子,比如一个设备的前面显示屏板子,如果主芯片选STM32F429去驱动,那么因为需要跑ST官方的Emwin等人机界面图形库,所以需要外扩一个sdram来为显示屏图像做缓存;为了显示开机logo、界面上其他图标,需要一个外扩flash去存储这些图片;显示面板上又需要掉电保存一些参数,所以外扩一个eeprom等等,然后软件去根据板载的硬件平台去做相关的程序开发。

当然实际项目当中民品PCB板考虑经济因素一般是4层或者6层居多,如果是军品则考虑更多的性能指标,可能会选择8层以上,原件也选型比民品稳定性高。一般来说4层PCB板即可满足绝大部分民品的需求,相比2层板PCB设计余量更大且价格比2层板贵得有限,同时方便选取参考面做阻抗匹配、空间大方便等长设计等等,一般标准4层板单线为6mil的线宽,差分走线为4.9mil线宽,差分线间距为7.8mil,再做好对内等长5-10mil即可。如果线密度较大需要降低走线宽度,则可以通过调整板厚来实现,比如DIY Artix7开发板单线调整 为5mil,差分走线为4.9mil,差分线间距为8.2mil,这里感兴趣的同学可以下载SI9000去计算PCB板阻抗或者直接咨询板厂。一般来说PCB层数是由SOC主芯片而定的,比如选择QFP封装或者仅有256个引脚的BGA封装,即使板子上带有ddr3颗粒或者sdram颗粒,选择4层板通过调整走线基本都可以做出来,但是如果选择484个引脚的BGA封装芯片一般就需要6层板甚至更高的层数。

在SOC主芯片选型之前要多明确功能方面的需求,可以多翻翻官方芯片手册,选择可用的同时也选择性价比最高的,这时候我们更应该多关注有没有需要特别注意的地方,比如有的SOC芯片需要不同种类的电压供电才能正常工作,这些电压之间有没有上电的顺序要求;比如通过需求评估要外挂四颗ddr3颗粒作为SOC芯片的外扩内存,但有的SOC芯片手册里明确写到不支持fly-by拓扑,只能做T拓扑;比如一个项目里需要多个uart和spi,那么选的SOC芯片引脚是否足够,如果不够能否做引脚复用,是否有多个dma通道方便程序上的编写,如果有些不确定的地方请多参考官方手册以及相关市面上成熟的开发板设计,其实在最初做这款DIY Artix7开发板的时候,Artix7芯片的bank上电顺序,以及Artix7芯片滤波电容的选取,不同bank供电电压开始也有不清楚的地方,笔者也反复核实了Xilinx官方硬件设计手册和Xilinx官方的开发板,打板焊接后,慢慢调试稳定。所以还是建议朋友们在做好嵌入式软件的同时也多去关注硬件以及整个产品的架构,多涉猎周边的知识,这对大家以后的发展都非常有帮助。比如,FPGA做得熟练又掌握了医疗设备相关知识,或者电力电子相关知识等等行业方面的背景知识,那么未来的待遇一定会很好,而且随着项目积累可替代性很低。

Xilinx Artix7选型

DIY开发板板载一颗Xilinx A7系列芯片作为开发板的主控芯片,它的型号则是经典的XC7A35T-2FTG256C,可能有朋友会问,为什么要选择这颗芯片呢,Xilinx 7系列不应该还有Spartan7以及K7,V7嘛,图2为Xilinx官方手册对7系列芯片的宣传画。

图2 Xilinx 7系列芯片的宣传画

笔者之前因为工作需要,为了完成项目转产也反复研究过Xilinx 7系列的芯片手册,虽然Xilinx芯片种类很多,但是从研发角度考虑,个人认为Xilinx有两款芯片一款是Spartan-6XC6SLX9,另一款就是XC7A35T-2FTG256C,可以说是性价比之王,下面简单地为大家分析下Xilinx芯片的选型问题。

图3 Xilinx A7 系列FPGA 芯片

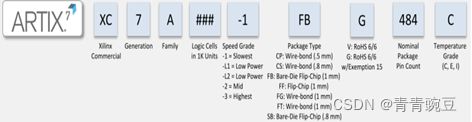

曾经用惯了Spartan6觉得应该追随Spartan7的脚步了,但可惜现实却不是这样,因为Spartan7这款芯片定位比较尴尬,它相比A7、K7、V7推出得更晚,也就是说更新颖,可在资源上和A7差别不大,价格却因为供货问题虚高不下。而相比之下A7已经稳定供货了很多年,充分被市场所检验,型号丰富可以满足客户不同的需求。站在实际研发的角度,有两个地方笔者觉得A7很难能可贵:一、A7系列虽然都是BGA封装但是却有256PIN、325PIN、484PIN、676PIN等等给客户选型,客户可以根据自己需求来选型,对于一般的项目A7 256PIN四层板基本可以搞定,然后再评估是否需要外扩sdram或者ddr3内存颗粒,以及需要选多大的资源是35T、50T、还是100T等等,如果需求上要外扩2颗ddr3内存颗粒,可以看看484PIN能否满足需求,引脚是否够分配等等;二、A7系列比如484PIN的型号,不论是35T、50T还是100T、200T资源,它的引脚定义和芯片封装都完全相同,硬件上可以做到最大程度的兼容性,其中Artix7系列的命名说明如图4所示。

图4 Xilinx Artix7芯片命名规则示意图

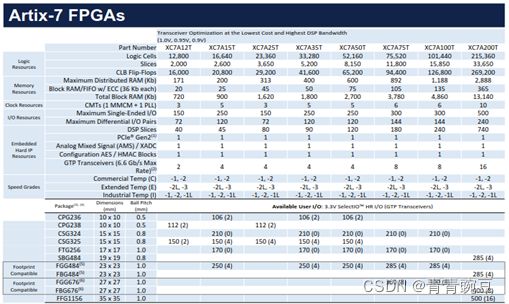

Artix7各个型号的资源情况如图5所示,这里朋友们可以在实际项目工程中,根据Vivado生成的资源报告来预估合适自己项目工程的芯片型号,当然实际项目当中,还是非常地灵活的,可以具体情况去具体分析,比如有些资源可以替代,RAM和FIFO在FPGA设计当中用到的很多,Xilinx的Vivado环境下可以用不同资源去生成RAM和FIFO,既可以用LUT生成,也可以用Block RAM去生成;比如做数字信号处理FFT运算和其他IP核有串行计算和并行计算的配置可选,如果对计算时间要求不是特别严格的情况下可以配置成串行的节约资源;再比如做图像视频开发,板载只有两颗ddr3颗粒,在读写速度方便显然不如四颗ddr3颗粒,为平衡硬件成本和用户体验,可以折中缓存三帧图片处理,实际应用中也取得很好的效果。

图5 Xilinx Artix7芯片各个型号的资源逻辑数量

Xilinx Artix7硬件设计要点

这里真是抛砖引玉,和大家分享下Artix7在做这款DIY开发板和做实际项目工程中积累到的一些经验,首先Xilinx官方硬件设计手册:ug475_7Series_Pkg_Pinout和ug483_7Series_PCB,一定要好好看下,毕竟是官方手册上面很多细枝末节都有提到,这两个手册对于整个Xilinx 7系列A7、K7、V7、Spartan7各个型号引脚定义,上电顺序、封装尺寸等等都有详细的说明,其次Xilinx官方也推出了一些Artix7开发板比如Nexys、Arty、Basys3,有很多细节值得去借鉴,最后市面上也有一些大厂的开发板硬件电路方面也具有很好的参考性,可以在硬件设计的过程中去多参考一些已经大批量转产的大厂电路板。

下面笔者从主芯片供电电路、主芯片滤波电容选取、Bank电压及引脚配置、外围电路搭建、PCB板硬件设计四个方面结合Artix7芯片简单谈一谈,也都是实践过后得到的一些总结和心得吧,希望对大家的工作学习有所启发和帮助。

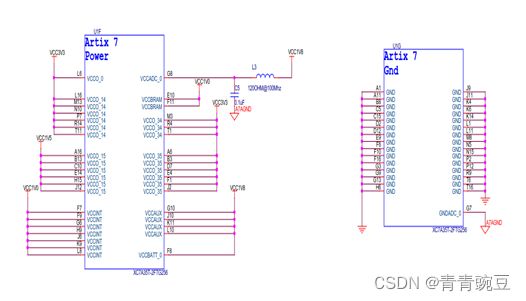

一、主芯片供电电路

谈到供电Artix7这款芯片,其实内部有很多种类的电压,比如VCCO是FPGA的IO接口的参考电压,VCCINT是FPGA的核心电压,VCCADC是FPGA内部AD转化电路的供电电压,VCCAUX是FPGA的辅助电压,VCCBRAM则是FPGA内嵌的块RAM存储器的供电电压,这里面还是有一定的上电顺序要求,一般来说上电顺序是: 1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCO,其中1.0V是VCCINT和VCCBRAM电压、1.8V是VCCAUX和VCCADC电压,1.5V是外接ddr3颗粒Bank的参考电压,3.3V是一般VCCO Bank的参考电压,这就需要多个DC/DC转换芯片,所以这里参考了其他厂家的电源设计,使用TLV62130RGT作为板载的DC/DC芯片,因为该芯片本身自带有EN和PG引脚,这就使得对PCB板上电顺序硬件上可以控制,电源供电的详细硬件设计如图6所示,DIY开发板Artix7芯片的引脚供电电压如图7所示。

图6 DIY Artix7开发板的DC/DC供电电路

图7 DIY Artix7开发板的供电引脚

二、主芯片滤波电容选取

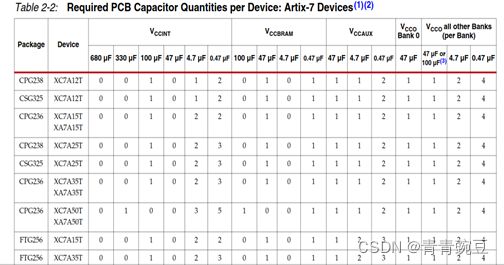

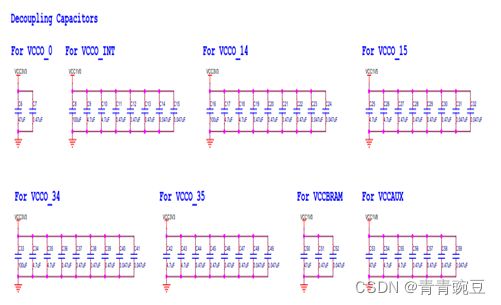

谈到滤波电容的选取,一定要好好仔细阅读ug483_7Series_PCB官方手册,上面有详细的写到Xilinx 7系列的每款FPGA芯片需要多大容值的,多少数量的滤波电容,滤波电容的合理使用和放置对整板硬件上的稳定运行起到至关重要的作用,笔者曾购买过市面上的其他核心板做实验,在实际使用过程中容易出现硬件上不稳定的Bug,其实很大程度上是因为过度去节省FPGA下的滤波电容导致,所以建议朋友们不要为了节省电容而导致硬件的不稳定,这在转产时候会非常头疼,图8是ug483_7Series_PCB官方硬件设计手册的截图,我们对照XC7A35T-2FTG256C型号即可选择好Artix7下面的对应的滤波电容,在做这款开发板的时候也有些细枝末节不确定的地方,笔者也参考了Xilinx官方推出的Arty原理图,DIY开发板Artix7滤波电容的选取如图9所示。

图8 ug483_7Series_PCB官方手册截图

图9 DIY Artix7开发板滤波电容的设计

三、Bank电压及引脚配置

接触过FPGA的同学可能会记得写xdc约束文件时候,有不同的引脚电平定义,比如LVCMOS33、 LVCMOS15、LVTTL、LVDS等等,这其实和硬件PCB板上对FPGA的每个Bank供电电压有关系,举个例子,豌豆开发板主控芯片是XC7A35T-2FTG256C,它包含有四个Bank,分别是Bank14、Bank15、Bank34、Bank35,PCB板上对这些Bank的供电引脚供多大的电压,直接决定了这个Bank上的IO引脚输出什么样的电平,比如Bank15在开发板上外接了ddr3颗粒,需要对其供电引脚供1.5V参考电压,那么连接这个Bank的IO在.xdc约束文件上需要定义为LVCMOS15或者LVTTL,Bank14、Bank34、Bank35在PCB板上是由3.3V电压做参考,所以对应的IO可以定义为LVCMOS33或者LVTTL,同时在实际项目工程中,比如在做 FPGA高速接口设计,经常遇到需要让FPGA的IO输出LVDS电平,那么这时候就需要在硬件PCB板上把其对应的Bank供电引脚用2.5V电压供电。

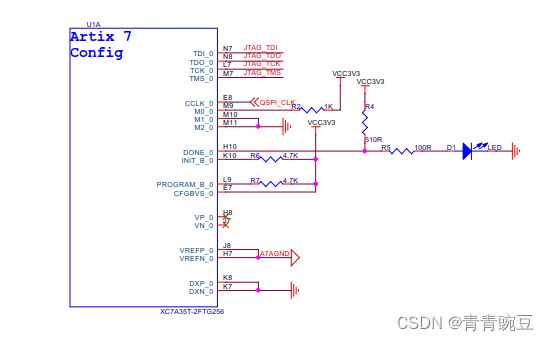

拿这颗XC7A35T-2FTG256C芯片来说,除了Bank14、Bank15、Bank34、Bank35以及供电接地引脚之外,还有一些引脚是做特殊功能使用的,其实对于Artix7系列芯片而言,这些引脚名是一样的,在绘制原理图的笔者把这些特殊引脚放到一起如下图10所示,这样做容易后期检查和维护,这些引脚包括了JTAG下载调试引脚:TDI_0,TDO_0,TCK_0,TMS_0,还有一些其他特殊功能的引脚,这里ug475_7Series_Pkg_Pinout官方手册里也做了详细说明是需要上拉还是下拉亦或者不接,这里也参考了Xilinx官方推出的开发板原理图把VREFP_0和VREFN_0接到模拟地,和其他数字地用一个磁珠来隔离。

这里需要注意的一点就是一般Xilinx的FPGA芯片会外接一个qspi flash用来存储编译后的.mcs程序文件,这个qspi flash和FPGA芯片连接引脚是固定的,其中CCLK_0需要连接其时钟引脚,而其他的引脚IO_L1P_T0_D00_MOSI_14、IO_L1N_T0_D01_DIN_14、IO_L2P_T0_D02_14、IO_L2N_T0_D03_14分别对应其DQ0-DQ3,IO_L6P_T0_FCS_B_14需要去连接片选CS引脚,这里也可以编写FPGA程序来人为控制将.mcs程序通过对应时序逻辑烧写到这颗qspi flash里,从而实现远程更新程序的目的(关于FPGA远程进行程序更新的博客,笔者在后续会写两篇博客详细去叙述设计过程),官方文档ug470_7Series_FPGAs_Configuration_User_Guide,里面关于flash的选型和外接电路等等配置都有非常详细的解读。

图10 DIY Artix7开发板初始化引脚硬件设计

四、外围电路搭建

通过前面的介绍,这颗XC7A35T-2FTG256C芯片已经硬件上稳定跑了起来,如果是在做实际项目,那么我们就需要根据项目需求选取合适的外围电路,也举个实际工程的项目的例子,做一款精密仪器仪表,控制板是由一颗STM32和一颗Artix7组成的,而Artix7在这里起到主要的作用,包括和STM32通过SPI总线通信、对后端adc实时采样计算电压、电流的有效值、平均值、峰值等送至STM32端,对adc采样的点做FFT快速傅里叶变化,还原其输入波形并将其打包输出到STM32端,响应STM32端传来的设置dac指令,包括电压、电流、频率波形等,再通过DDS信号发生器输出,对外连接了USB2.0和RS232接口,接口可以通过上位机输入特殊形状的波形,FPGA读取这些点写入保存到eeprom里,这样就可以断电重启后由STM32控制直接输出指定频率的上位机设定的波形形状。那么结合这个实际项目,XC7A35T-2FTG256C芯片就应该和STM32连接一个SPI总线,并且硬件上和后端adc模拟转数字、dac数字转模拟芯片连接,一个IIC总线连接eeprom,同时硬件上还需要和外挂的USB2.0接口芯片FT232HL,和RS232接口芯片MAX3232连接,用于上位机通信。

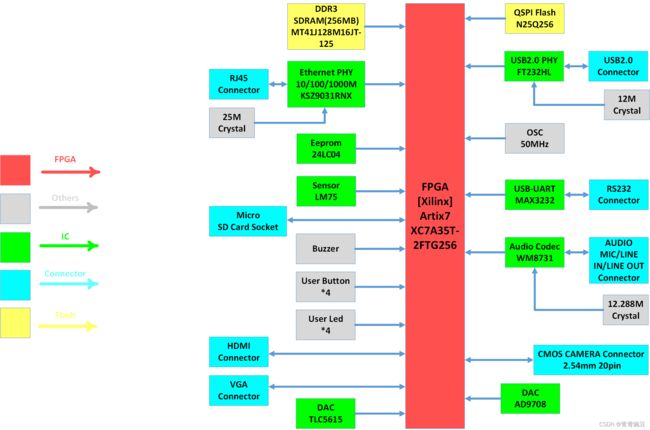

如图11所示,是DIY Artix7开发板原理图整体设计架构,笔者根据工作学习需要把很多常用模块,比如温度传感器、eeprom、按键、指示灯、sd卡、蜂鸣器等集成在这块开发板上;同时开发板也包含了常用的外接接口如USB2.0、千兆网口、RS232串口;板上配有镁光的ddr3内存颗粒方便大家对大数据量的存储和处理、qspi flash方便掉电保存.mcs文件;另外开发板上包括了一颗串行dac,一颗并行dac,方便做复杂数字信号处理的前期验证;同时VGA和HDMI、CMOS摄像头接口也让这块开发板可以很好地去做图像视频处理的实验;最后配上一颗音频编解码芯片WM8731,在闲暇之余也可以研究下音频信号的输入和输出。

图11 DIY Artix7开发板原理图整体设计架构

五、PCB板硬件设计

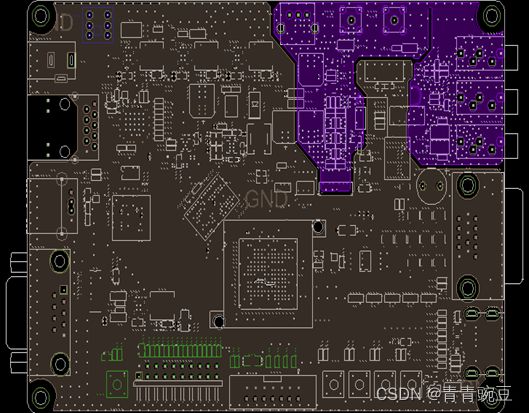

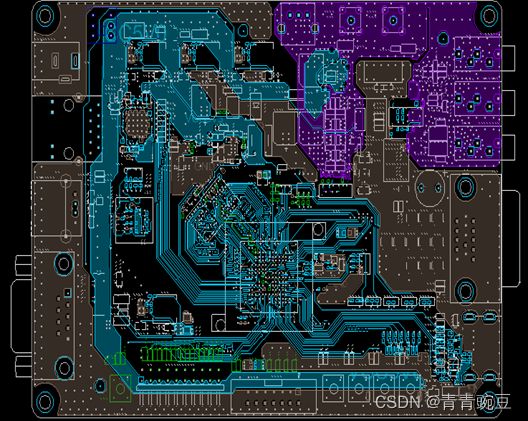

经过前面的需求分析和原理图设计、以及原件封装库制作,后面就到了PCB layout设计的环节了,现实工作中很多FPGA工程师甚至硬件工程师,对PCB layout设计看得很淡,并没有太多的深入专研,甚至觉得板子拉通就可以,实在拉不通就增加层数即可,可事实上PCB layout设计在整个硬件设计上占有重要的地位,直接决定了PCB板的性能好坏。图12到图15分别是DIY Artix7开发板顶层、地层、电源层、底层PCB layout设计图。因为FPGA的IO口本身就具有很强的可复用性,所以在PCB设计的时候可以通过调整走线,再修改原理图,最大程度上保证走线顺畅,从而方便布局布线,也可以节约PCB板层数,极大节约成本。

在设计这块DIY开发板的时候,因为考虑到主芯片XC7A35T-2FTG256C只有256个引脚,所以采用了四层PCB板设计,整块开发板走线50ohm阻抗匹配,差分100ohm阻抗匹配,对核心模块比如ddr3进行了等长设计,信号线同组同层,严格按照规范进行PCB layout设计,此外模拟地和数字地层、电源层也做好了很好的分割,保证顶层和底层走线会有很好的参考平面,在整块开发板的布局上做到整齐美观、性能良好、丝印清晰,最后考虑到线密度较大,实际布线时单线用了5mil线宽进行走线,并调整了差分走线的线间距。

图12 DIY Artix7开发板顶层PCB文件

图13 DIY Artix7开发板地平面PCB文件

图14 DIY Artix7开发板电源平面PCB文件

图15 DIY Artix7开发板底层PCB文件