JT硬件乐趣

DC-DC电源中电感下方的铜箔如何处理

挖空处理:

TPS5430Demo板 500kHz

LM25085Demo板 350kHz

MAX77827Demo板

不挖空处理:

LM3150Demo板 750kHz

TPS40200Demo板 200kHz

LT3476Demo板

不挖的时候,电感下方的铜箔形成涡流效应,A对信号线产生干扰,B同时涡流降低了电源的效率(影响极小),产生热量,实际降低了DC模块的效率,但是起到了屏蔽的左右,有效阻挡辐射带来的干扰

,降低对电路其他部分的干扰

挖掉的时候,电磁波未被屏蔽而向外泄露,可能对其他部分产生干扰,同时可能会带来EMC超标

此时选择电感的类型就决定了电感下铜箔是否作挖空处理

工字型 半封闭 铁氧体一体成型式磁全封闭(最优)

现今,一般优先选用一体成型式电感,不挖空,用地屏蔽

PCB过孔

电容应就近打过孔,2个会更好

芯片供电电源的过孔不要放在电容和IC之间,会增加电容与电源管脚之间的分布参数,瞬态电流索取问题,带来环路增大的风险

盘中孔工艺可以尝试的用起来,能极大的降低走线电感带来的问题

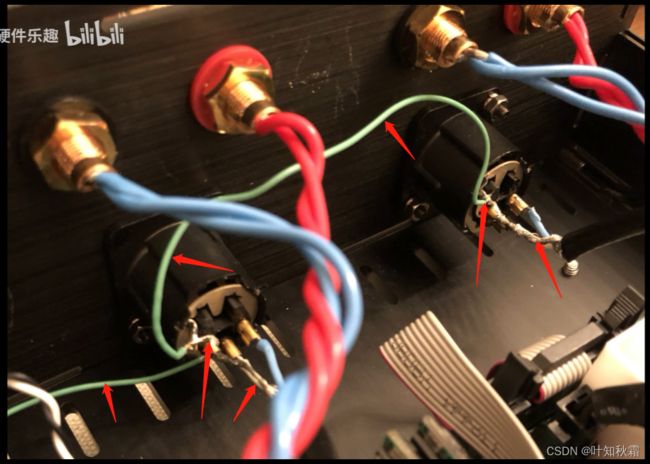

金属屏蔽的机壳,有PE屏蔽层,应就近接外壳

非屏蔽机壳,有屏蔽层的线缆应该采用星型方式连接,注意屏蔽层不要在机壳内离PCB过近

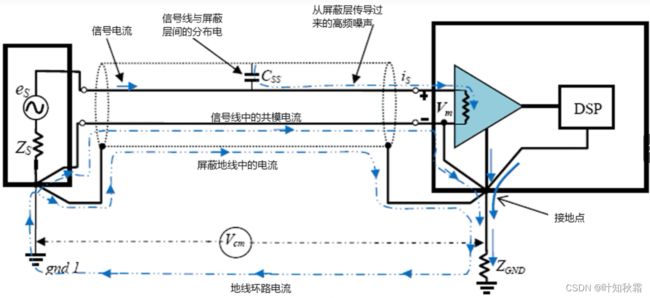

地线环路是造成地线50Hz噪声的主要原因,环路不是关键,公用地线才是罪魁祸首

地线环路不是理想的导体,上面会存在走线电感和分布电容等,如果上面感应出大的干扰,同时接地环境又不良的时候,干扰会不断在环路中流动,感应到被屏蔽的信号上,带来小信号的扰动

平衡差分线的机制是,差分线的两根对地的阻抗相同,共模干扰在其上感应的噪声信号大小相同,相位相同,在接收端会被相减抵消,从而差分传输的信号得到了平衡,有效的传输

音频设备第一脚问题

A.线缆的屏蔽地线到机箱地的线段过长,会感应很大的射频干扰

B.共用地线导致的干扰耦合

C.PE地线过长,会使共模电压增加

D.屏蔽线在机箱内部过长的走线,会充当天线,将射频信号耦合到机箱内部的电路上

修改后

正确做法是屏蔽直接就近接外壳PE

屏蔽地线中的共模电流带来的噪声

金属机壳的机箱接地或者不接地都不会影响机箱的电磁屏蔽效果,重点考虑电路布线、线缆布局以及机箱开孔问题

机箱的接地质量要可靠

注意机箱上的开孔和开槽,当机箱上有电流流动是,由于开孔或者开槽等,会在槽不同边形成不同电流,会产生天线效应,引起辐射超标等问题

PCB的地与外壳地是否直通,是个需要讨论的话题

1.PCB的地和机箱地分隔开来,浮地系统

2.台式电脑的主板的逻辑地是通过金属螺丝拧到机箱上的,出于EMC考虑(若此时接地没做好,会适得其反,产生更坏的结果。考察客户的PE相线的可靠性)

3.逻辑GND和外壳地之间跨接一个高压陶瓷电容

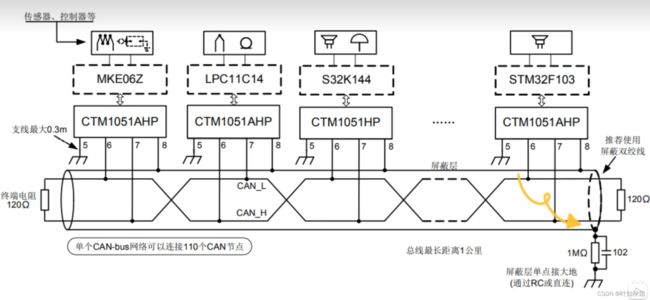

4.屏蔽的话,可以一端接地也可以两端都接PE

每个设备单独外壳单独接PE,同时通信屏蔽层连接在一起,最终统一接大地,或通过RC接大地

电子技术发展到如今,由于多层板工艺和高速信号的回流都是紧贴其前向路径,已经没有必要进行模拟和数字地的划分了,只需要进行合理的数字模拟的模块化处理即可。统一地成为主流

带状线缆信号线缆之间加地线,减小串扰(屏蔽)和回流路径(降低辐射发射)

高频工作的电路,如果高频电流的索取,不是从就近的电容上时,势必会从远端的电源上索取,此时由于走线的走线电感和分布电容,直流阻抗等影响,会在这段导线上产生噪声,噪声会沿着电路传输到其他模块电路,共用地线存在走线电感和分布电容等,也会将某个功能模块的干扰噪声传输到其他功能模块

SPI总线串接匹配电阻

信号之所以需要匹配,是信号波长和传输导线接近时(1/10γ或者1/8γ),才需要阻抗匹配,防止信号反射带来的波形失真问题,否则容易通信错误

若SPI的Tr为10ns,那1/10的时间传输距离是 1ns*3*10^8m/s÷2(导线中速度减半)=15cm,所以导线传输距离大于15cm时,需要作阻抗匹配

IIC总线的上拉电阻,太大时,由于分布电容和器件输入电容组成的RC充电电路,上升沿会变缓,太小时,器件会接收过大的灌电流,可能损坏器件,所以最后实际加入不同阻值的上拉电阻,使用示波器实测,观察上升沿和时钟周期的关系,会不会影响正常的数据通信为准

阻抗不连续点,会发生波的反射现象

USB驱动器的驱动端的内阻一般没有45Ω那么大,所以一般会串联一个电阻,这个电阻加上内阻等于45Ω,差分走线的一半,不然高速通信时的反射干扰会增加误码率。具体的设计中这个电阻取值多大,需要参照不同的器件手册说明书选定。其他高速接口的串联匹配电阻同理,详查规格书后做相应的设计

最后,综合上面的仿真结果和分析,我们可以对串联走线阻抗突变对信号质量的影响做如下总结:

(1)串联走线阻抗突变越大,对信号质量的影响也就越大。因此在进行PCB布线设计时,我们的串联走线阻抗突变应尽可能的小;

(2)信号的上升时间越长,串联走线阻抗突变段对信号质量的影响越小,即信号质量就越好。

(3)阻抗突变段的长度越长,串联走线阻抗突变段对信号质量的影响越大,当突变长度足够短时,影响可以忽略不计。因此在进行布线设计时,我们应该把走线的阻抗突变段尽可能的控制在较短的长度内,当然,具体的长度还要结合对应信号的上升时间进行评估。