Makefile 【2】— 普通变量和自动变量定义、使用($@、$^、$< 作用)、变量覆盖 override、变量的来源 origin

1、变量的定义

Makefile 文件中定义变量的基本语法如下:

变量的名称=值列表变量的名称可以由大小写字母、阿拉伯数字和下划线构成。等号左右的空白符没有明确的要求,因为在执行 make 的时候多余的空白符会被自动的删除。至于值列表,既可以是零项,又可以是一项或者是多项。如:

name_list = aa bb cc调用变量的时候可以用 $(name_list) 或者是 ${name_list} 来替换,这就是变量的引用。实例:

OBJ=main.o test1.o test2.o test3.o

test:$(OBJ)

gcc -o test $(OBJ)当要添加或者是删除某个依赖文件的时候,我们只需要改变变量 OBJ 的值就可以了。

2、变量的赋值

Makefile 的变量的四种基本赋值方式:

- 简单赋值 ( := ) 编程语言中常规理解的赋值方式,只对当前语句的变量有效。

- 递归赋值 ( = ) 赋值语句可能影响多个变量,所有目标变量相关的其他变量都受影响。

- 条件赋值 ( ?=) 如果变量未定义,则使用符号中的值定义变量。如果该变量已经赋值,则该赋值语句无效。

- 追加赋值 ( += ) 原变量用空格隔开的方式追加一个新值。

2.1、简单赋值

编写 Makefile

x := a

y := $(x)b

x := cc

all:

echo "x=>$(x)"

echo "y=>$(y)"终端输入 make 查看结果

echo "x=>cc"

x=>cc

echo "y=>ab"

y=>ab变量 y 只与之前定义的 x 相关,不管 x 之后是否有变化。

2.2、递归赋值

编写 Makefile

x = a

y = $(x)b

x = cc

test:

echo "x=>$(x)"

echo "y=>$(y)"终端输入 make 查看结果

echo "x=>cc"

x=>cc

echo "y=>ccb"

y=>ccb变量 y 与最新的 x 值相关。

2.3、条件赋值

编写 Makefile

x = a

y = $(x)b

x ?= cc

test:

echo "x=>$(x)"

echo "y=>$(y)"终端输入 make 查看结果

echo "x=>a"

x=>a

echo "y=>ab"

y=>ab在定义 x ?= cc 之前 x 已经定义过,所以该行不生效。

编写 Makefile

#x = a

y = $(x)b

x ?= cc

test:

echo "x=>$(x)"

echo "y=>$(y)"终端输入 make 查看结果

echo "x=>cc"

x=>cc

echo "y=>ccb"

y=>ccb2.4、追加赋值

编写 Makefile

x = a

y = $(x)b

x += cc

test:

echo "x=>$(x)"

echo "y=>$(y)"终端输入 make 查看结果

echo "x=>a cc"

x=>a cc

echo "y=>a ccb"

y=>a ccb3、自动变量

关于自动化变量可以理解为由 Makefile 自动产生的变量。自动化变量的取值根据执行的规则来决定,取决于执行规则的目标文件和依赖文件。下面是对所有的自动化变量进行的说明:

| 自动化变量 | 说明 |

|---|---|

| $@ | 表示规则的目标文件名。如果目标是一个文档文件(Linux 中,一般成 .a 文件为文档文件,也成为静态的库文件),那么它代表这个文档的文件名。在多目标模式规则中,它代表的是触发规则被执行的文件名。 |

| $% | 当目标文件是一个静态库文件时,代表静态库的一个成员名。 |

| $< | 规则的第一个依赖的文件名。如果是一个目标文件使用隐含的规则来重建,则它代表由隐含规则加入的第一个依赖文件。 |

| $? | 所有比目标文件更新的依赖文件列表,空格分隔。如果目标文件时静态库文件,代表的是库文件(.o 文件)。 |

| $^ | 代表的是所有依赖文件列表,使用空格分隔。如果目标是静态库文件,它所代表的只能是所有的库成员(.o 文件)名。一个文件可重复的出现在目标的依赖中,变量 $^只记录它的第一次引用的情况。就是说变量$^会去掉重复的依赖文件。 |

| $+ | 类似$^,但是它保留了依赖文件中重复出现的文件。主要用在程序链接时库的交叉引用场合。 |

| $* | 在模式规则和静态模式规则中,代表“茎”。“茎”是目标模式中“%”所代表的部分(当文件名中存在目录时,“茎”也包含目录部分)。 |

main: main.o name.o greeting.o

g++ $^ -o $@

main.o: main.cpp

g++ -c $^ -o $@

name.o: name.cpp

g++ -c $< -o $@

greeting.o: greeting.cpp greeting.h

g++ -c $< -o $@对比之前写的 Makefile 中的命令,我们可以发现

- $@ 代表的是目标文件;

- $^ 代表的是所有依赖的文件;

- $< 代表的是依赖文件中的第一个;

我们在执行 make 的时候,make 会自动识别命令中的自动变量,并自动实现自动化变量中的值的替换。

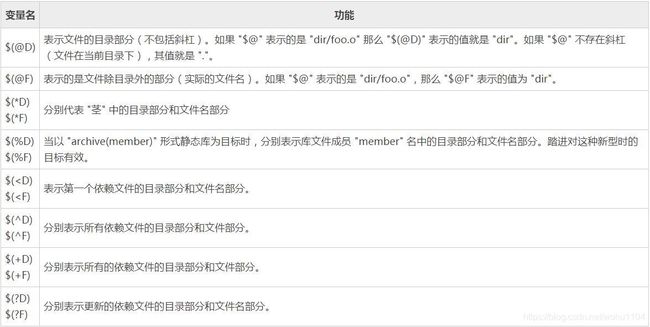

make 中在这些变量中加入字符 D 或者 F 就形成了一系列变种的自动化变量,这些自动化变量可以对文件的名称进行操作。

4、变量覆盖 override

作用是使 Makefile 中定义的变量能够覆盖 make 命令参数中指定的变量

语法:

override =

override :=

override += 下面通过一个例子体会 override 的作用:

(1)Makefile 内容 (没有用 override)

SRCS = a.cpp b.cpp

all:

echo "SRCS is $(SRCS)"执行 make 结果:

wohu@ubuntu:~/cpp/func$ make SRCS=c.cpp

echo "SRCS is c.cpp"

SRCS is c.cpp

wohu@ubuntu:~/cpp/func$ (2)Makefile 内容 (用 override)

override SRCS = a.cpp b.cpp

all:

echo "SRCS is $(SRCS)"执行 make 结果:

wohu@ubuntu:~/cpp/func$ make SRCS=c.cpp

echo "SRCS is a.cpp b.cpp "

SRCS is a.cpp b.cpp

wohu@ubuntu:~/cpp/func$ 5、判断变量的来源

语法:

$(origin ) 返回值有如下类型:

| 类型 | 含义 |

|---|---|

| undefined | 没有定义过 |

| default | 是个默认的定义, 比如 CC 变量 |

| environment | 是个环境变量, 并且 make时没有使用 -e 参数 |

| file | 定义在 Makefile 中 |

| command line | 定义在命令行中 |

| override | 被 override 重新定义过 |

| automatic | 是自动化变量 |

示例:

# Makefile 内容

val-in-file := test-file

override val-override := test-override

all:

@echo $(origin not-define) # not-define 没有定义

@echo $(origin CC) # CC 是Makefile默认定义的变量

@echo $(origin PATH) # PATH 是 bash 环境变量

@echo $(origin val-in-file) # 此Makefile中定义的变量

@echo $(origin val-in-cmd) # 这个变量会加在 make 的参数中

@echo $(origin val-override) # 此Makefile中定义的override变量

@echo $(origin @) # 自动变量, 具体前面的介绍执行 make

$ make val-in-cmd=val-cmd

undefined

default

environment

file

command line

override

automatic