计算机组成原理实验1---运算器 预习报告

本实验为哈尔滨工业大学计算机组成原理实验,实验内容均为个人完成,目的是分享交流,如有抄袭将追究责任,笔者能力有限,若因此影响读者的分数,本人深表抱歉。

一、 实验目的

- 了解运算器的组成结构

- 基于数据通路图,观察并分析运算器的工作原理

- 基于信号时序图,观测并分析运算器的工作原理

二、 实验预习

1.学习使用 TDX-CMX 实验台,然后回答下列问题。

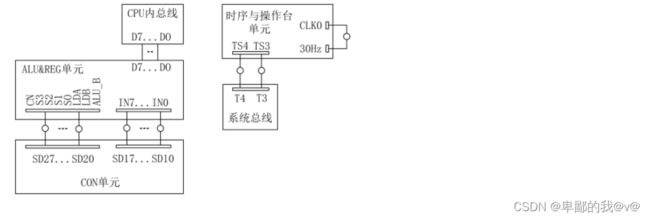

实验台上“时序与操作台单元”中 KK1 功能是选择时序单元的工作状态,KK2 功能是选择时序单元的节拍信号,ST 功能是产生一个节拍信号;方波信号 300Hz、30Hz 和 3Hz 位于实验台的时序与操作台单元单元,ALU 位于实验台的 ALU®单元,数据输入位于实验台的 IN单元单元(我看指导书上写的ALU的输入是IN单元 但是不理解为啥输入AB寄存器要通过CON上的SD17等),数据总线和地址总线位于实验台的系统总线单元。

- 注:CON单元那几个控制部件,是选择什么操作的(算数运算、移位运算、逻辑运算、LDA表示把存的数存入A寄存器中、LDB表示把数存入寄存器B中)

- CON右边是A和B的输入,从左到右依次是高位到低位

- 输入之前,一定要多按几下节拍器,这样才会通过时序逻辑将数据传输过去。

- FZ零标志位,FC进位标志位,要注意这两个的信息。

2.参看实验台运算器实现原理,填写括号处的部件名称或信号名称。

3.ALU 完成哪些基本的逻辑运算、算术运算和移位运算。

3.ALU 完成哪些基本的逻辑运算、算术运算和移位运算。

- 逻辑运算:

- 取AB其中之一

- AB按位或

- AB按位与

- A取非

- 算术运算:

- 加法运算、

- 带进位的加法运算、

- 减法运算、

- 减一运算、

- 加一运算。

- 移位运算:

- A不带进位循环右移B位

- A逻辑右移一位

- A带进位循环右移一位

- A逻辑左移一位

- A带进位循环左移一位

功能如图所示,要了解各种运算的硬件实现。

4.画出 4×4 阵列乘法器原理图,分析延迟与哪些因素有关?

影响因素:与乘数位数有关 与门电路延迟有关

分析:阵列乘法器的工作过程类似于人的手算乘法,FA(全加器)的斜线方向是进位输出,竖线方向是输入和输出,图中最后一行构成了一个串行加法器。由于FA一级是无需考虑进位的,他的进位被暂时保留下来不往前传递,因此同一级中任意一位FA加法器的进位输出和输出几乎是同时形成的,和“串行移位“相比可大大减少同级间的进位传递延迟,所以送往最后一行的串行加法输入与 门电路的级数有关 即与乘积位数有关,也与门电路的延迟有关。

5.简述 Quartus 环境下载 sof 文件到 FPGA 的操作流程。

从桌面上双击打开Quarts,导入文件点击file,openproject找到文件所在的路径安装路径/FPGA/Multiply/Multiply,导入后点击open programma;添加硬件,选择USB,点击左上角start,等待烧录成功。

(1)从桌面打开软件

(2)导入文件

(3)选择打开文件

(4)导入后双击program device

(5)点击Hardware setup添加硬件

(6)选择USB

(7)点击start烧录

(8)查看左上角烧录成功

三、 实验步骤及原始数据记录

本次实验包括基本运算器实验和阵列乘法器实验两部分。

外部PC机实现

- 本机运行

- 把时序与操作台单元的“MODE”用短路块短接,使系统工作在四节拍模式,JP1(在 ALU® 单元)用短路块将 1、2 短接,按图 1 所示连接实验电路,并检查无误。图中将用户需要连接的信号用圆圈标明(其它实验相同)。

图 1 实验一接线图

- 将时序与操作台单元的开关 KK2 置为‘单拍’档,开关 KK1、KK3 置为‘运行’档。确认连线正确。

- 打开电源,如果听到有‘嘀’报警声,说明有总线竞争,应立即关闭电源,重新检查接线,直到错误排除。然后按动 CON 单元的 CLR 按钮,将运算器的 A、B 和 FC、FZ 清零。

连线如图所示,注意相同面的正反相同,否则会读数麻烦。

-

用输入开关向暂存器 A 置数

按动 2 次时序单元的 ST 按钮,产生 T1、T2 节拍后,拨动 CON 单元的 SD17…SD10 数据开关,形成二进制数 01100101(或其它数值),数据显示亮为‘1’,灭为‘0’。置 LDA=1, LDB=0,按动 2 次 ST 按钮产生 T3、T4节拍,则将二进制数 01100101 置入暂存器 A 中, 暂存器 A 的值通过 ALU单元的 A7…A0 八位 LED 灯显示。(我感觉前提条件得控制LDA指令将传递寄存器打开指令)

如图所示位ST位置

记录:

暂存器 A 的数据(二进制):01 100 101

按动 2 次 ST 按钮后 ALU 中 A7~A0 中数据(二进制):01 100 101

-

用输入开关向暂存器 B 置数

按动 2 次时序单元的 ST 按钮,产生 T1、T2 节拍后,拨动 CON 单元的 SD17…SD10 数据开关,形成二进制数 10100111(或其它数值)。置 LDA=0, LDB=1,按动 2 次ST 按钮产生 T3、T4 节拍,则将二进制数 10100111 置入暂存器 B 中,暂存器 B 的值通过 ALU 单元的 B7…B0 八位 LED 灯显示。

记录:

暂存器 B 输入数据(二进制):10 100 111

按动 2 次 ST 按钮后 ALU 中 B7~B0 中数据(二进制):10 100 111

改变运算器的功能设置,观察运算器的输出

按动 2 次时序单元的 ST 按钮,产生 T1、T2 节拍后,置 ALU_B=0、 LDA=0、LDB=0, 然后按表 3 设置 S3、S2、S1、S0 和 Cn 的数值,并观察数据总线 LED 显示灯显示的结果。

如置 S3、S2、S1、S0 为 1001,运算器作加法运算;置 S3、S2、S1、S0 为 0010,运算器作逻辑与运算。按动 2 次 ST 按钮产生 T3、T4 节拍,观察 FC、FZ 标志位变化。

- 当S3S2S1S0 = 1001,运算器做 加法运算,

寄存器A内容01 100 101,寄存器B内容10 100 111

FC = 1 FZ = 0

- 当S3S2S1S0 = 0010,运算器做 逻辑与运算,

寄存器A内容01 100 101,寄存器B内容10 100 111

FC = 1 FZ = 0

连接运行

环境的建立及操作的简单介绍

下图演示所需下载的软件,找到安装包并点击进行安装

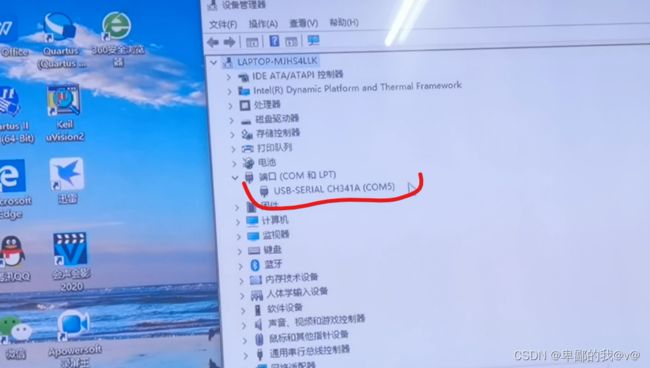

安装完以后,此电脑右键->属性->设备管理器(有些电脑打开设备管理器的方式不同,具体问题具体分析)->找到端口 就能看到是否连接USB接口

安装TDX-CMX

安装完以后打开发现 下位机已复位代表环境搭建成功

点击右上角来介绍一下我们的门电路

分为主存和微存,可以修改数据的值

修改完之后点击,刷新指令数据区域,数据就完成了更新

通过下拉可以实现不同的实验查看,对于本实验来说,选择运算器实验

上图表示可以选择不同的时序方式控制查看程序,单拍运行、单周期运行、单机器指令运行、连续运行,当然也可以打开示波器,通过配合我们扩展单元的逻辑层

点击运行就可以

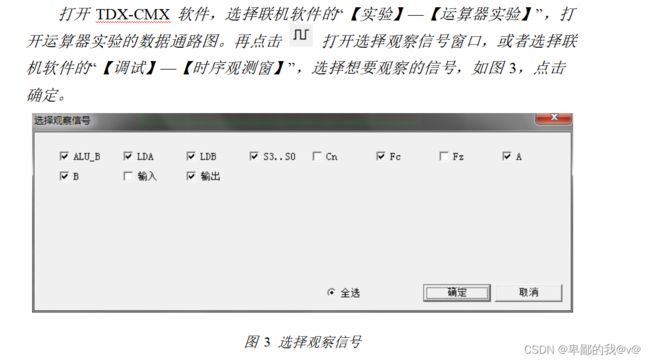

时序观测窗口可以选择我们想要观察的信号

点击确定 就可以进行时序观测了

如果还有不明白的 就在实验的帮助菜单中 实验帮助 选择指导书 继续查询

操作

如果实验箱和 PC 联机操作,则可通过软件中的数据通路图来观测实验结果,也可通过软件中的信号时序图来观测实验结果。

-

观测数据通路图

打开 TDX-CMX 软件,选择联机软件的“【实验】—【运算器实验】”,打开运算器实验的数据通路图,如图 2 所示。

操作方法同本机运行,每按动一次 ST 按钮,数据通路图会有数据的流动,反映当前运算器所做的操作,或在软件中选择“【调试】—【单节拍】”,其作用相当于将时序单元的状态开关 KK2 置为‘单拍’档后按动了一次 ST 按钮,数据通路图也会反映当前运算器所做的操作。

重复上述操作,并完成表 3。然后改变 A、B 的值,验证 FC、FZ 的锁存功能。点击联机软件的 “【回放】—【保存…】” 按钮,可保存数据通路图的实验过程。

表 2 记录运算结果

观测时序逻辑

弹出时序观测窗,操作方法同本机运行,记录操作过程的时序图,时序图左侧标明信号的名称

四 阵列乘法器验证实验

实验步骤

烧录见上方实验预习

上图为安装路径

- 根据上述阵列乘法器的原理,使用 Quartus 软件编辑相应的电路原理图并进行编译,其在 FPGA 芯片中对应的引脚如图 4 所示,框外文字表示连线标号,框内文字表示该引脚的含义(本实验例程见‘安装路径\FPGA \Multiply\Multiply.qpf’工程)。

- 关闭实验系统电源,按图 5 连接实验电路,图中将用户需要连接的信号用圆圈标明。

给A和B 置不同的数,观察相乘的结果。 完成实验报告表格。记录被乘数、乘数和乘积:

SD17~SD10输入数据:(00000101)SD07~SD00输入数据:(0 0000011)

L7~L0:(00001111)

下面是该阵列乘法器实现逻辑图,补充括号内缺失的信号名称。

- A3B1

- A3B0

- A3B1

- A3B3

这个图具体是怎么填的我也不知道,就是根据阵列乘法器的原理图找规律

思考题

1.本实验完成了 8 位加法器的设计,如何在实验台上实现 16 位加法运算?

可将十六位加法的低八位和高八位分为两组依次进行计算,首先进行低八位的加法计算,得到结果的低八位和一位进位,然后进行高八位加法运算,如果低八位的进位是0则得到十六位加法的高八位,如果低八位的进位是一则再将结果加一得到十六位加法的高八位。

2.试比较教材中无符号原码一位乘(4 位)与实验中阵列乘法器的时间延迟。

教材中的无符号原码一位乘(4位)需要进行四次加法和四次移位,每次都会有延迟。而阵列乘法器只有在四次进位时产生延迟。原码一位乘需要四次加运算四次右移运算设每次加法的延迟是2.5ty右移运算的延迟是txT1=10ty+4tx阵列乘法器前三行每行的延迟都是一位加法器的延迟2ty,最后一行的延迟是6ty,T2=3*2ty+3*2ty=12ty,因为右移运算的延迟显著大于一位加法运算,所以T1>T2。

3.思考题:将 A=01H 和 B=02H 进行逻辑与运算,观察运算器零标志 FZ 的时序,是否和进位标志

五.实验总结

本实验通过对底层硬件的操控和实践,了解了运算器的底层工作逻辑,并通过数据通路图和信号时序图,观察并分析运算器的工作原理 ,加强了对陌生软件的操作能力,同时,通过芯片的连接和管脚的辨别将理论付诸实际,增强了动手能力,同时将上课的理论知识转化为电路实现。通过对阵列乘法器的验证和实现,了解了对运算器进行优化的思路、方向,观察了乘法的结果,本次实验收获巨大。

六.操作注意事项

1. 实验箱上电后,等待设备就绪,端口会自动连接,如果初始化失败,按实验箱上的“复位”按钮。

2. 设备就绪后,进行登录。按学号、密码登录成功后,如果没有实验计划,请按“复位”,设置好端口后,重新登录。

3. 编辑实验报告单时,避免从word直接复制粘贴带有格式的文本,可以把答案保存在记事本txt上,进行复制粘贴,或者在报告编辑区手动输入。

4. 关于实验报告单中需要上传图片的题目,请准备低像素的图片,如果上传不成功,先完成其他内容,下次进行编辑。

5. 优先完成实验内容,如时序图上传、运算表格的编辑。实验报告可以后续从登录界面左上角功能中“查看历史实验报告”中进行编辑。