计算机组成原理-----存储器(上)

下周就实验了,写个文章开始女娲补天,如果有时间的话会加一些习题,本文参考唐朔飞计算机组成原理教材和视频和王道考研教材和视频,如有错误欢迎批评指正。

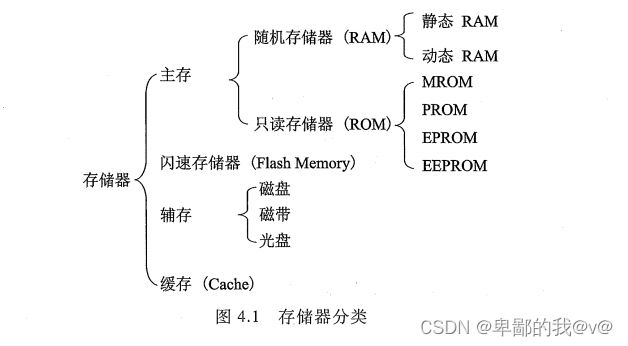

存储器整体架构:

组成分类

计算机的存储系统

![]()

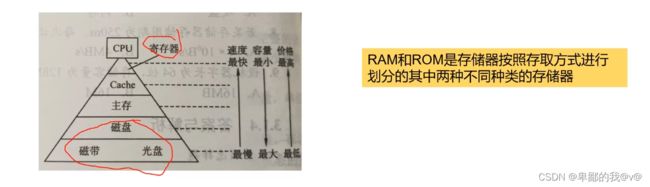

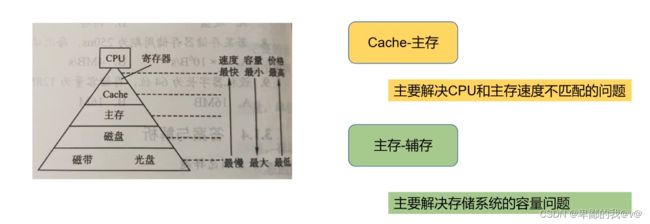

分级存储模式:

为了解决速度容量价格之间的矛盾

性能指标:

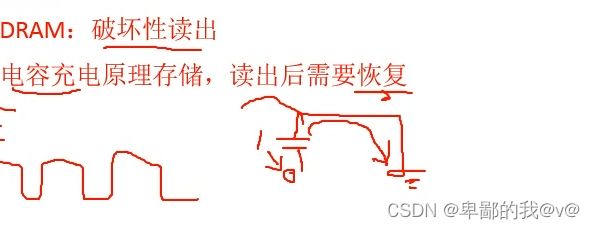

存取周期:存取时间加上恢复时间。为什么需要恢复时间,对于不同的存储器原因不同,举两个例子,首先是静态存储器SRAM,在读入和写入完之后,他会根据新的地址准备相应的数据信号,下方是他的波形图,发现数据并没有用简单的波形图来代替,这是因为他的数据是有很多位的,每一位通过不同的线传过来,到达的时间不一样,这就需要等待一段时间等大家都稳定下来,这样读出来的数据才不会出错

![]()

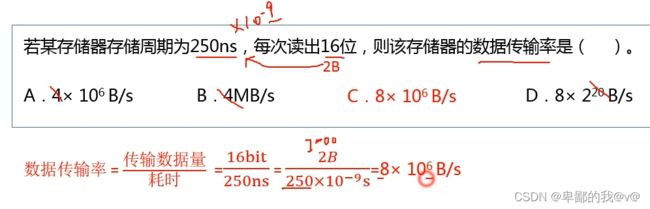

数据传送:

这个题很简单主要学习一下常用的单位换算。

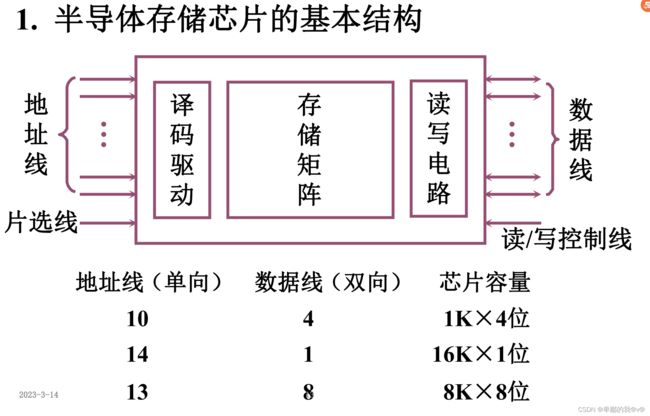

存储芯片的组成

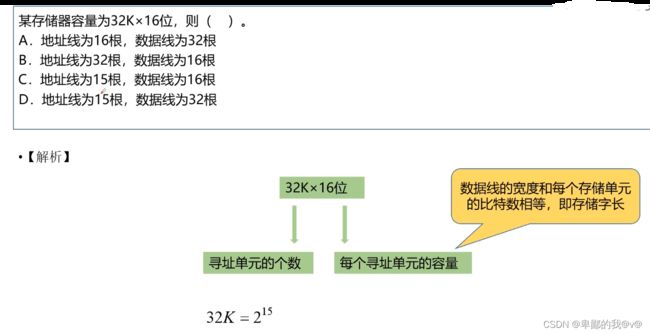

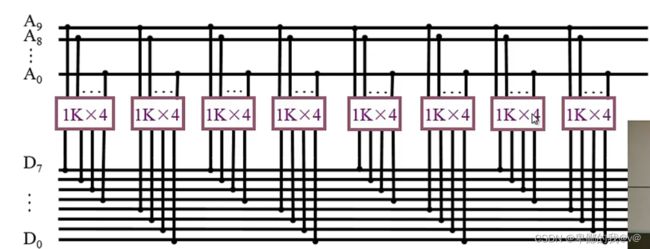

地址范围*数据的位数

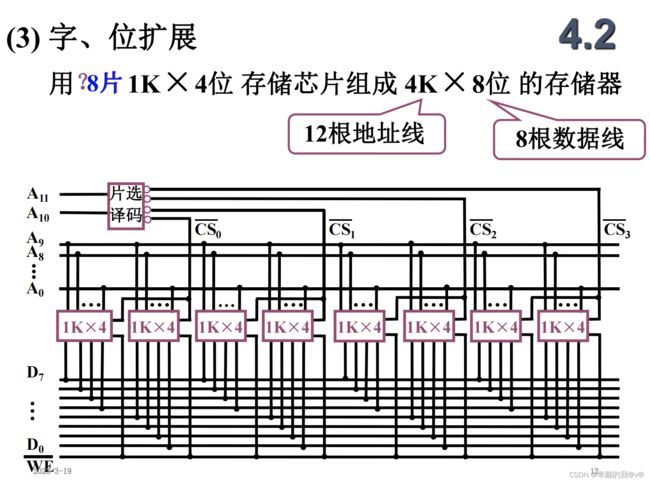

如果想要得到4K*8的芯片,需要4*2=8个第一个芯片的扩展,此时,地址线是12根,数据线是8根

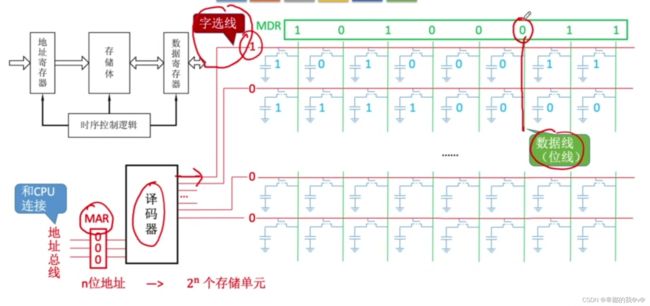

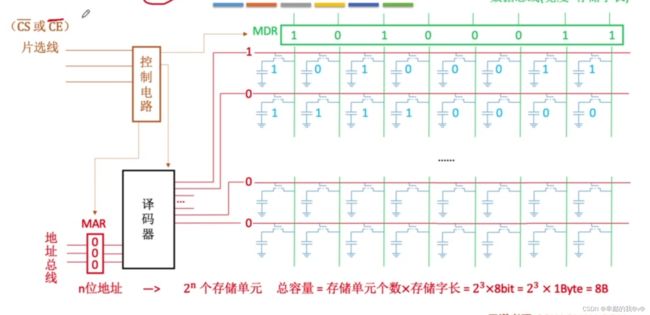

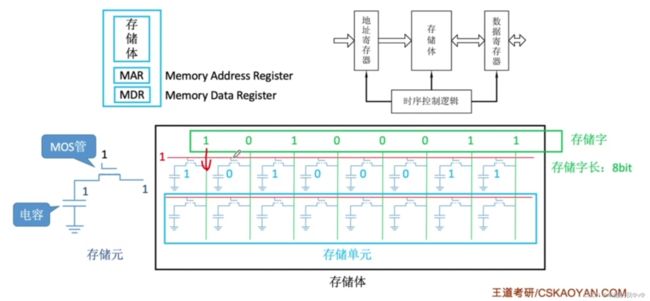

总的来说分成存储矩阵(可以存放数据),译码驱动,读写电路

基本的半导体元件和原理

存储体由MOS管和电容构成,由于是串联关系,所以给一根线通电会显示八个位也就是一个字节的01状况,一个字节等于多少个比特,这个得看存储体的结构

存储体由MOS管和电容构成,由于是串联关系,所以给一根线通电会显示八个位也就是一个字节的01状况,一个字节等于多少个比特,这个得看存储体的结构

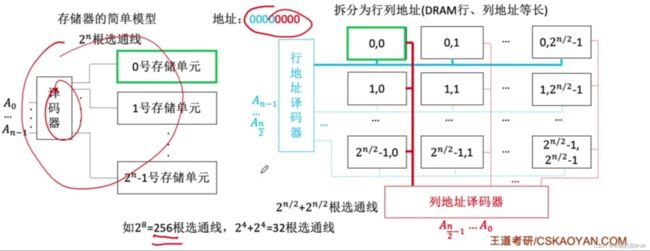

n位译码器能对应2的n次方的存储单元,也就是由2的n次方个地址总线

通过数据线送到MDR中,存储容量等于存储单元个数*字长

除此之外,还需要控制电路,通常用片选线表示输入信号,上面带一个横杠表示低电平有效

片选先用于决定存储哪一个芯片,如右图所示,若想要选取那个对号的芯片需要将这个芯片的CS横置为0,其他置为1,这样就能选取所需要的芯片了

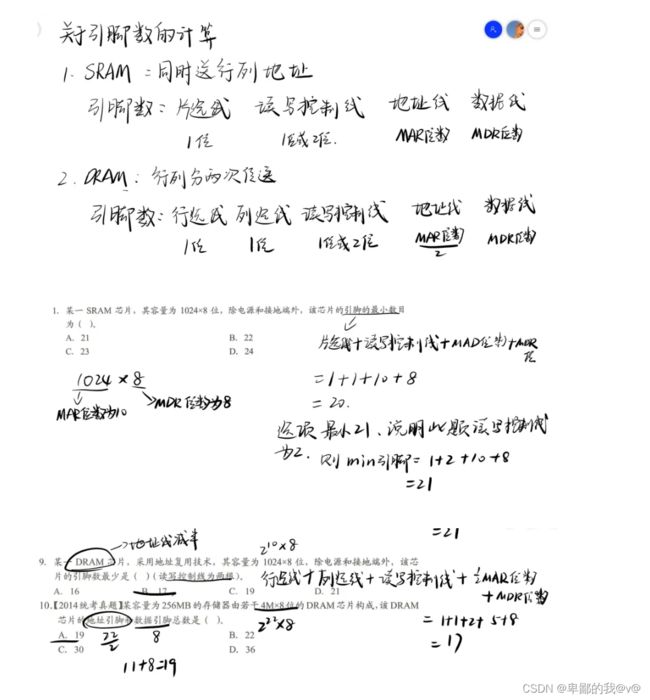

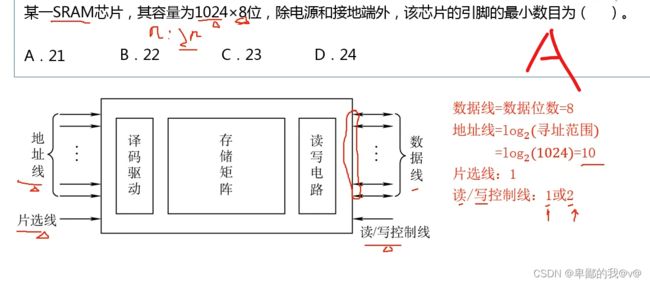

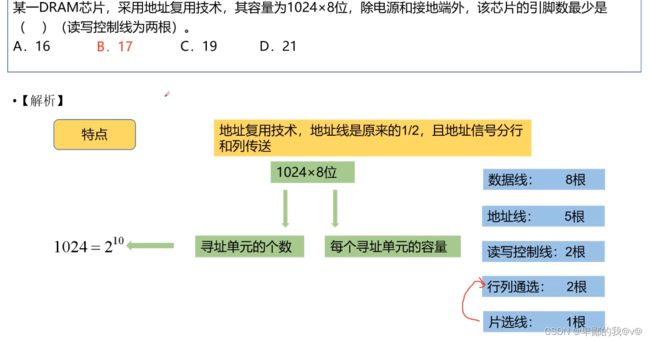

所以衍生了一类题型,引脚数的计算

转载链接:计组关于引脚数的计算 - 哔哩哔哩 (bilibili.com)

某容量为256MB的存储器由若干4M×8位的DRAM芯片构成,该DRAM芯片地址引脚和数据引脚总数为()_dram的地址引脚和数据引脚_雒十四的博客-CSDN博客

补充知识(单位换算):

1B=8b B表示byte,即 字节 b表示bit ,即 位 ,1字节=8位,1KB=1024B=1024*8b

计算机存储计量单位

1. 计算机最小存储计量单位是:BIT(位)

2. 计算机最基本存储计量单位是:Bytes(字节)

3. Bit和Bytes的关系:8Bit=1Bytes

4. 其他常用单位:1KB(1千字节)、1Mb(1兆字节)、1GB(1千兆字节)、1TB(1千G)

5. 常用单位之间以210 为进制单位即1024为进制.

6. 常用单位之间的换算:

1K=1Kb=1024b=8*1024 Bit

1M=1Mb=1024K=1024Kb=1024*1024b

1G=1Gb=1024M=1024Mb=1024*1024KB=1024^3b

1TB=1024GB=10242MB=10243KB=10244B=8*10244位

存储器的性能指标

(1):存储容量 主存存放二进制代码的总位数=存储元个数*每个存储元的位数

(2):存储速度

存储时间:存储器的访问时间

既可以是读时间,也可以是写时间

存储周期:连续两次独立的存储器操作

时钟周期-->机器周期--->指令周期

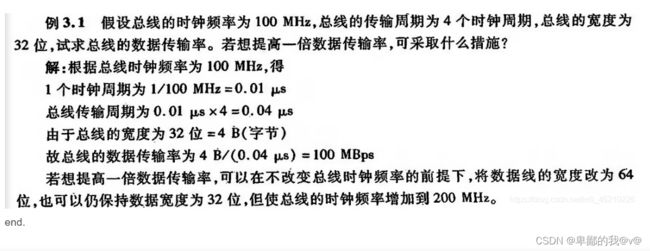

总线周期 一个周期有四拍

凡是有周期的都是受时间控制

(3):带宽:单位时间传送的二进制位数:位/s

数据总线的宽度/总线的周期计算机组成求带宽_燚燚燚536的博客-CSDN博客

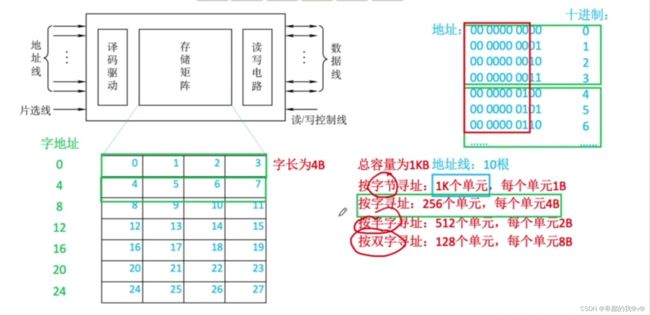

寻址

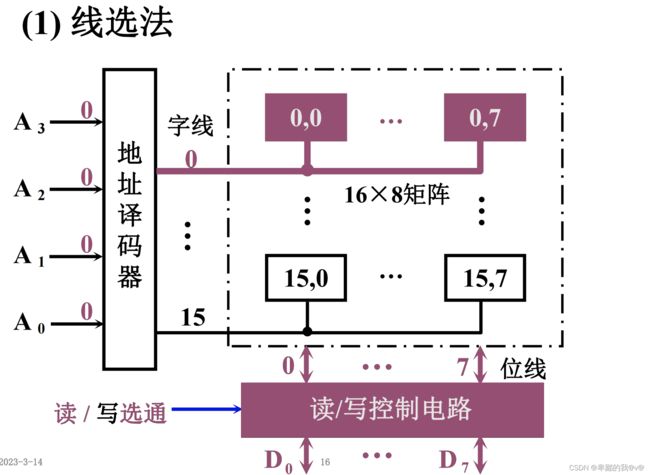

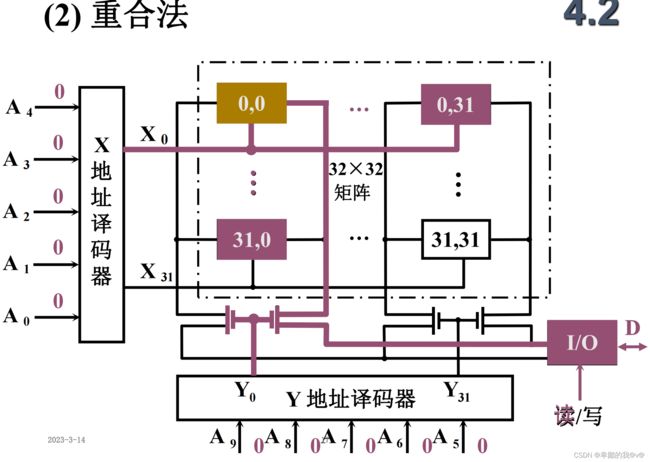

线选法/重合法

以按字寻址为例,每一行都是一个字,字长为4B,寻址只需要在末尾填两个0,比如一号单元就是100---------四号地址。

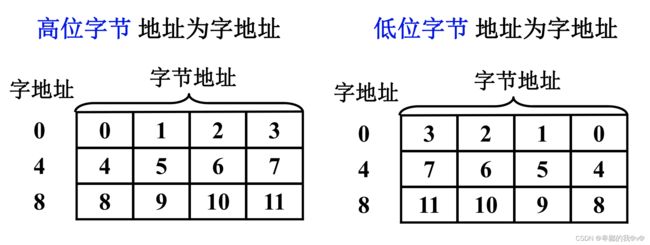

主存在存储单元中地址的分配:

高位字节存放在低地址把他叫做大端法,高位字节存放在高地址叫小端法

![]()

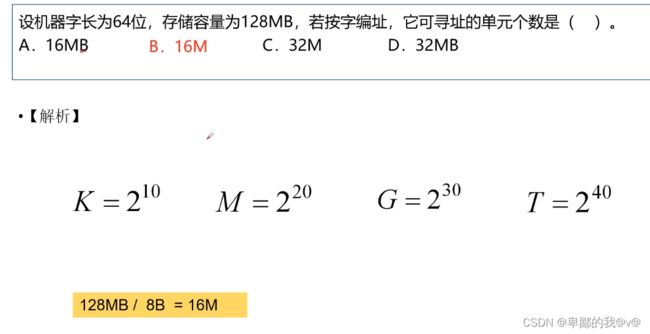

字的寻址范围和字长有直接关系,字节的寻址方式就是八位一寻址 解析:

按字寻址和按字节寻址_大多数的沉默|的博客-CSDN博客

算法 :

1.24位 就有2^24个地址空间

1Mb = 2^20b

所以是2^4Mb = 16Mb

2.地址线是24根,若字长为16位,16位两个字节需要一根地址线区分,所以剩下23根地址线,即8MW

3.地址线是24根,若字长为32为,32位三个字节需要两根地址线区分,所以剩下22根地址线,即4MW

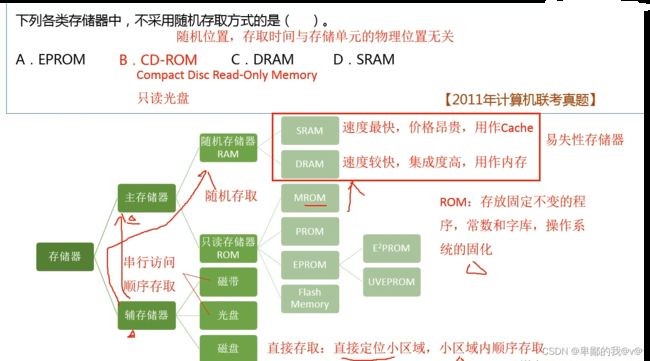

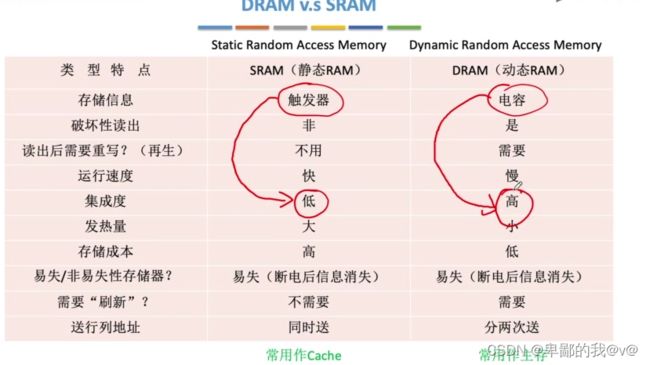

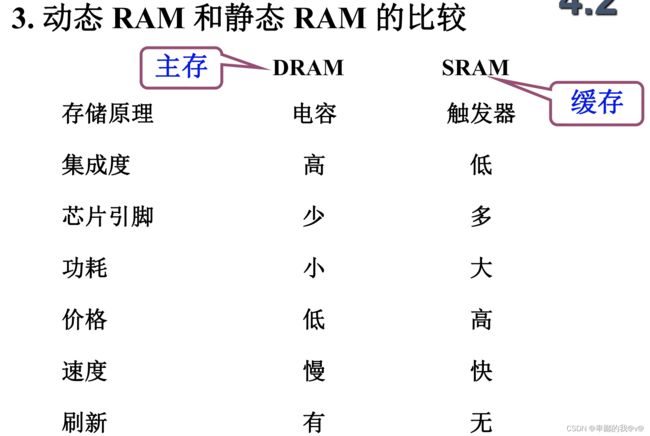

RAM

- DRAM 用于主存

- SRAM 用于cache

存储元件不同导致的特性差异

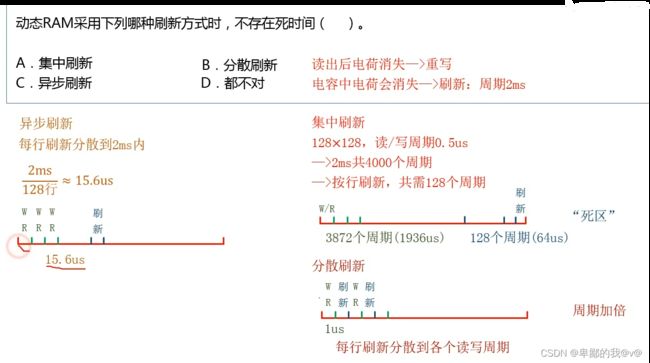

由于DRAM破坏性读入的性质,因此每次放电完之后要对他进行充电,即"刷新"过程,因此需要对刷新进行分析和讨论,关于刷新周期,一般是2nm,关于刷新存储单元,采用行列的方法,可以减少硬件的使用 。

分析译码过程↑

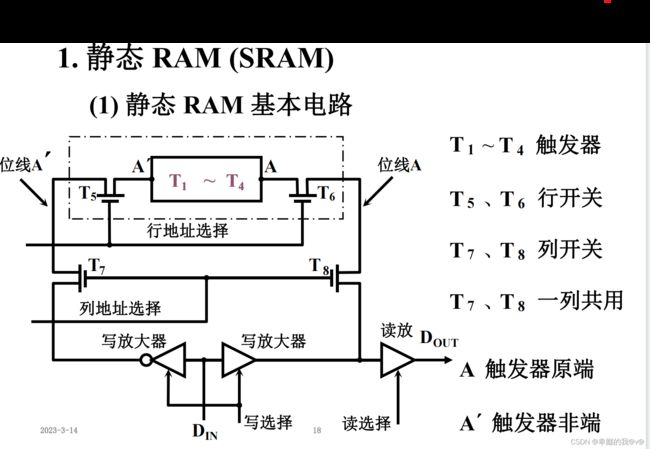

SRAM

SRAM基本结构

本质是一个双稳态触发器,具体工作过程看如下的视频

4.2 主存储器(上)4.2-a3_哔哩哔哩_bilibili

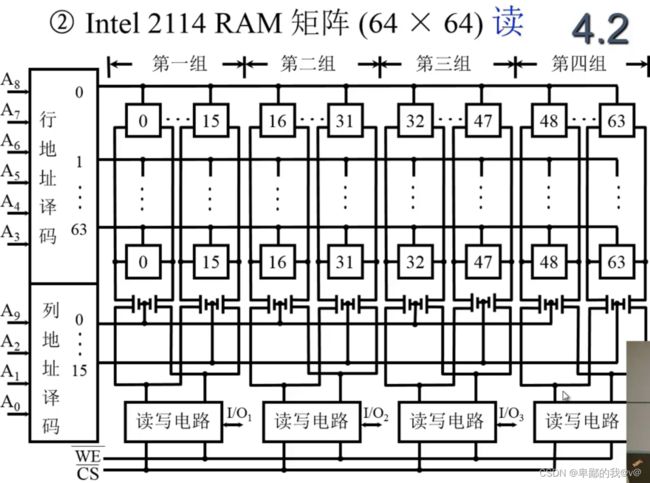

静态RAM四组读取数据方式

64位行地址,16位列地址,行地址控制第几行选中,然后将这64分成4组,每组16个,由下方的列地址译码器控制

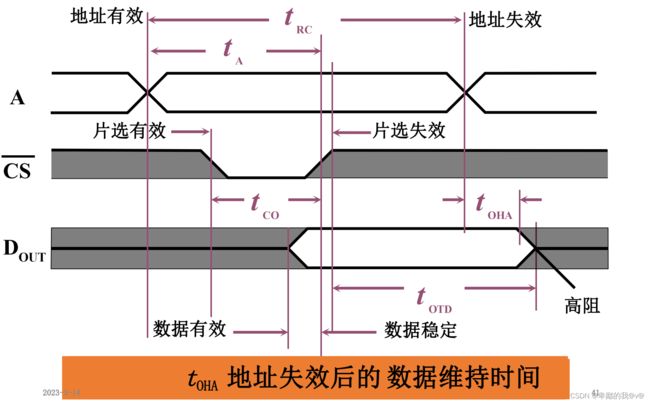

静态RAM读取数据时序

只有当片选信号有效的时候才能对数据进行读操作,![]() 代表地址保持的时间,也就是读周期的时间

代表地址保持的时间,也就是读周期的时间

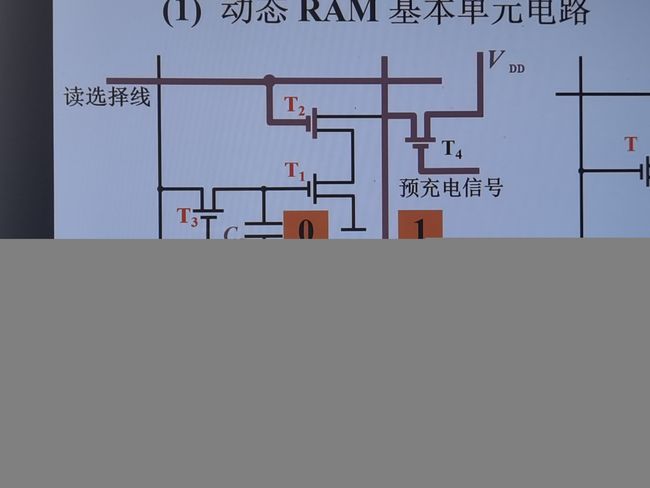

DRAM

基本组成:

由MOS管组成,MOS管就是加上高/低电压才能导通

简单介绍一下元件:他是由一个栅极电容(存放电荷1/不存放电荷0),接通之后就会出现有电流和无电流的现象,MOS管决定是否是通路,

如果加5V的电压就导通,也就是将这个数据选择,

工作过程

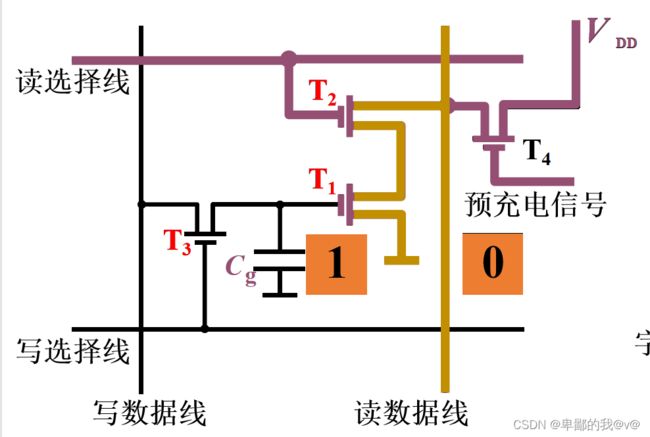

双管RAM

- 首先电路收到一个预充电信号,

门电路打开,

门电路打开, 往里充电,将电信号传递给读数据线,使读数据线置成高电平

往里充电,将电信号传递给读数据线,使读数据线置成高电平 - 读的地址通过译码驱动电路,通过读数据线,选择了

这条通路,这条通路被打开之后,如果

这条通路,这条通路被打开之后,如果 存放的是数据0的话,

存放的是数据0的话, 的门就不能打开,读数据线那端仍然保持高电平

的门就不能打开,读数据线那端仍然保持高电平 - 那么假如

中存放的是高电平1,就会使读数据线导通,由于读数据线是接地的,因此读数据线为0

中存放的是高电平1,就会使读数据线导通,由于读数据线是接地的,因此读数据线为0

写入的信息和实际存的信息是相反的逻辑

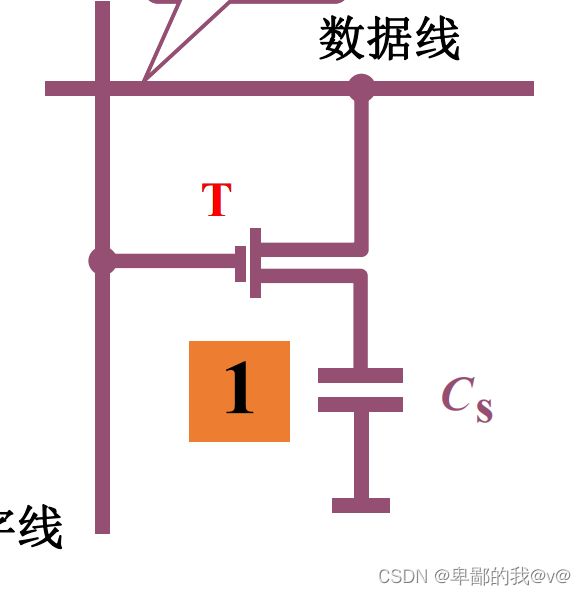

单管RAM

读出时数据线有电流 为 “1”

写入时 CS 充电为 “1” 放电为 “0”

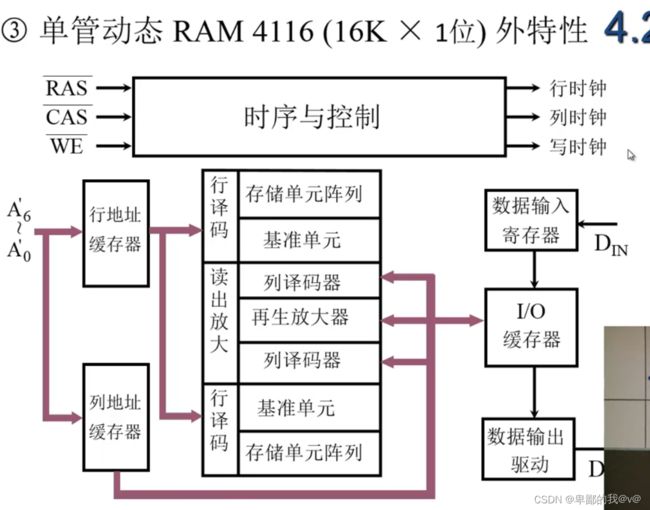

只有七个管脚,要处理14位也就是16K的数据,通过上方的时序与控制逻辑,将行地址和列地址存入缓冲器中。

特点

随着时间的推移,电容可能会放电,所以需要对RAM电路不断进行刷新

DRAM的刷新方式:

同步刷新,异步刷新,分散刷新

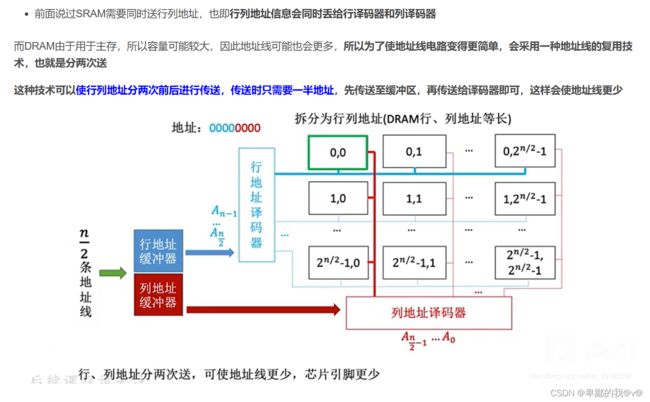

DRAM地址复用技术 :

RAM&ROM比较

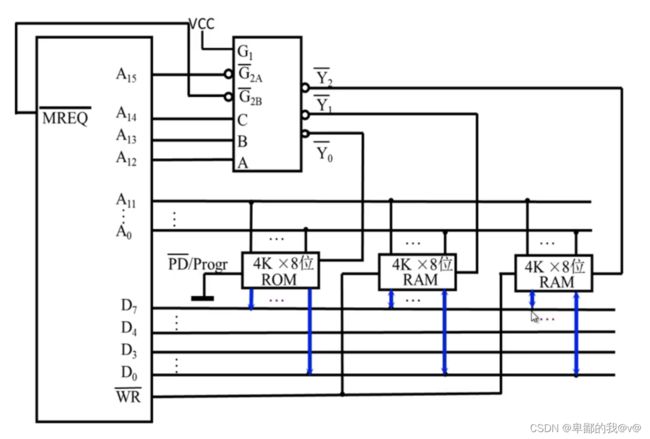

*存储器和CPU的连接

- 地址线连接

- 数据线连接

- 读/写命令的连接

- 片选线的连接

- 合理选择存储芯片

- 其他,时序负载

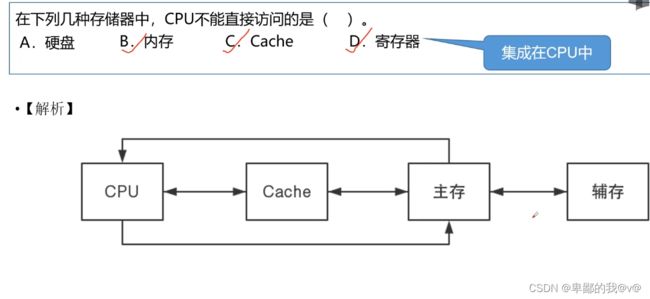

寄存器是集成在CPU内部,两种结构:缓存和主存结构:为了解决主存和CPU之间速度不匹配的问题,主存和缓存结构是为了解决存储容量问题

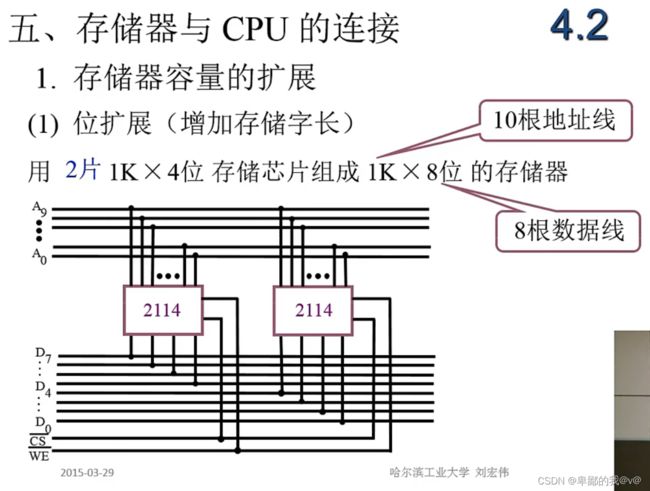

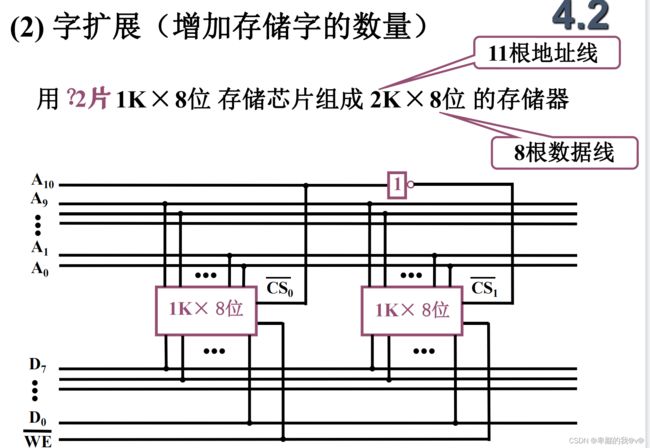

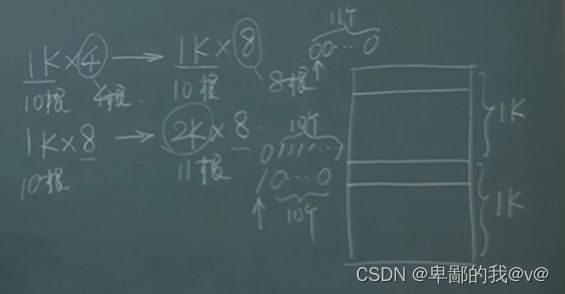

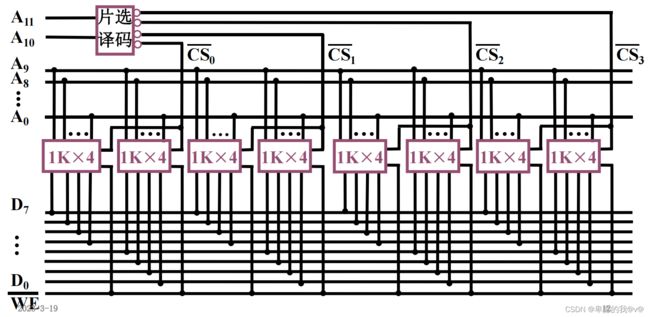

存储容量的扩展

(1)位扩展

用两个芯片组成存储器 通过片选线决定使用哪个芯片

最高位决定是高字位还是低字位

首先是数据线的扩展,两个芯片为一组,组成了1K*8的芯片,连接八位数据线

然后就是片选线,四个为一组,通过24译码器决定第几组的第几个

然后就是片选线,四个为一组,通过24译码器决定第几组的第几个

合理选择存储芯片

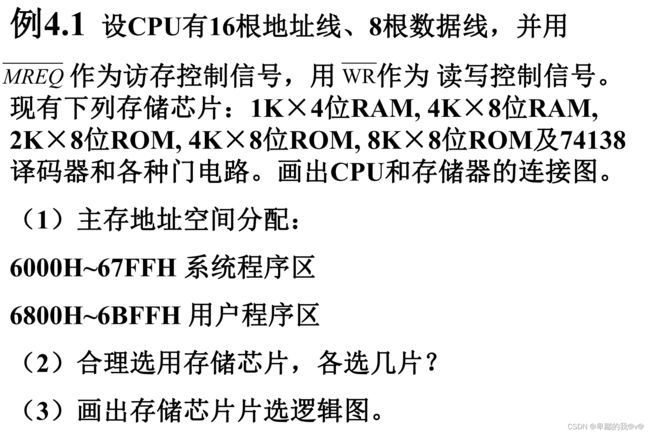

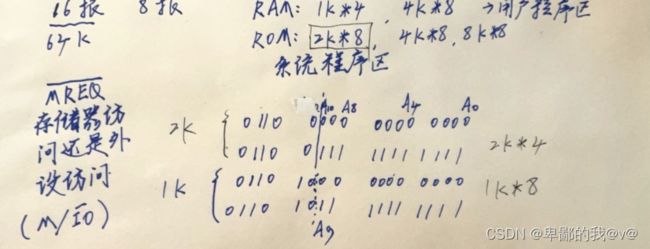

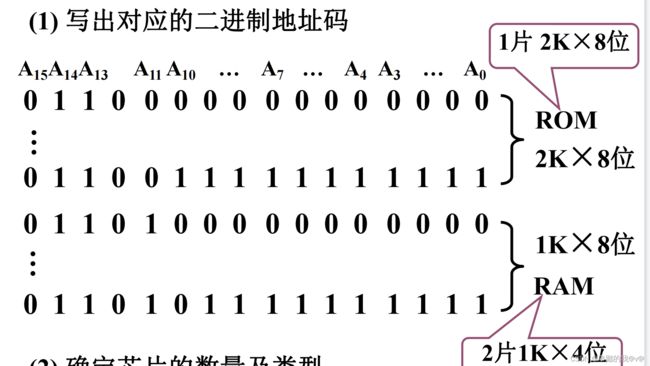

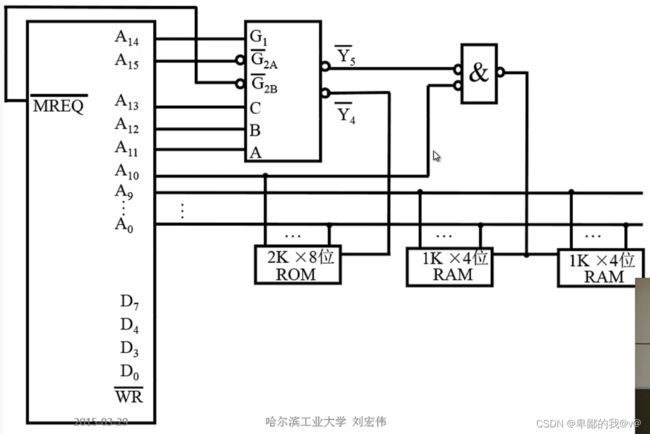

exp1:

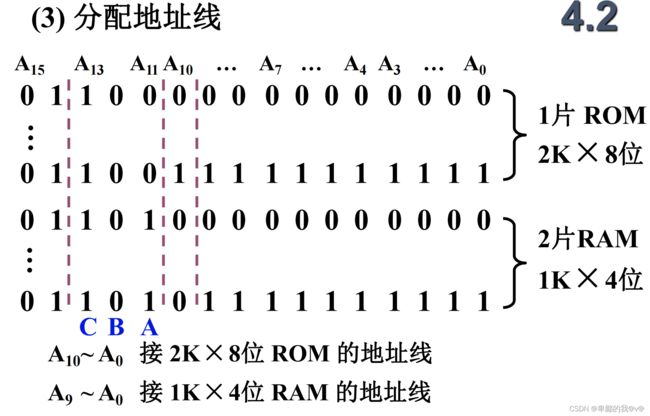

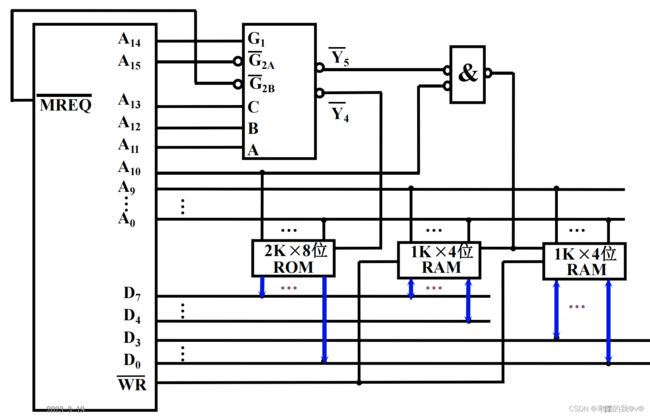

(2) 1片ROM 两片RAM

(4)G1恒置为高电平,下面的G2a横杠和B表示低电平有效,MREQ必须是低电平才能访问存储器,首先![]() 到

到![]() 分配地址总线,

分配地址总线,![]() 到

到![]() 通过一个三八译码器,由于只有两种情况,所以外面只需要伸出两根线,如果是4就连接ROM(因为只有一个芯片不需要选择),如果是5的话

通过一个三八译码器,由于只有两种情况,所以外面只需要伸出两根线,如果是4就连接ROM(因为只有一个芯片不需要选择),如果是5的话

光![]() 非不能决定是哪一个芯片,所以还需要借用一下

非不能决定是哪一个芯片,所以还需要借用一下![]() 来共同构成片选端,变成一个与的结果,去控制两个芯片的

来共同构成片选端,变成一个与的结果,去控制两个芯片的![]() 端

端

之后RAM设置成低四位和高四位连接,再加一个WR读写端。

![]() 再取非 00->0

再取非 00->0

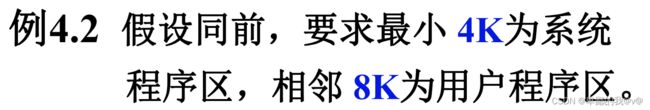

exp2:

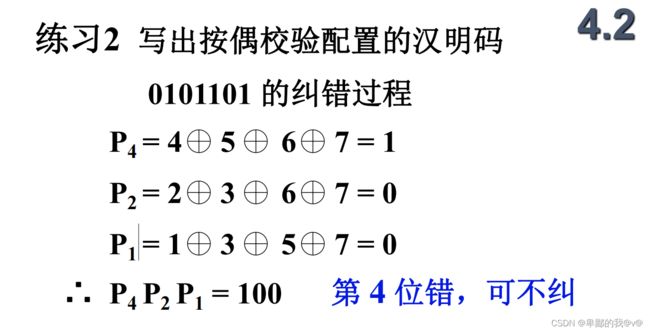

存储器的校验问题

存储器的校验指的是采用一定的手段方法判断传输过来的数据是否正确

常见的是奇偶校验:偶校验是看1的个数是不是偶数,

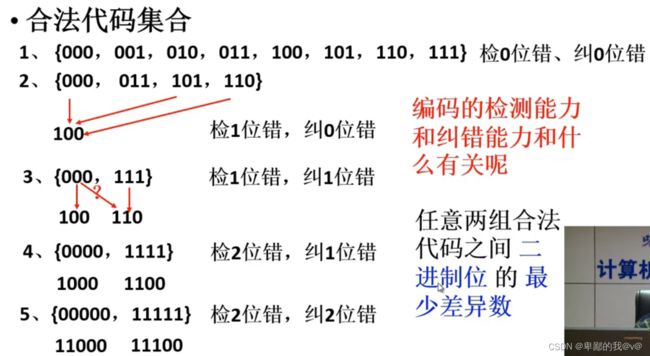

基本概念

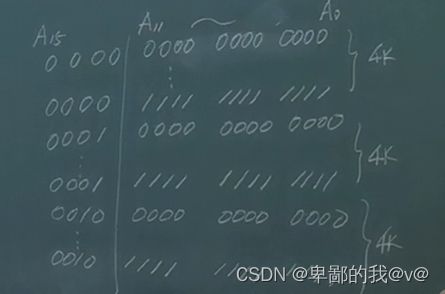

编码的距离:两组合法代码之间二进制位数的最少差异,编码的纠错能力和编码的距离有关

编码的检错能力和纠错能力究竟和什么有关呢?

给出一组公式并用上方的公式验证:

![]()

通常检测错误的位数要大于等于纠错的错误位数。

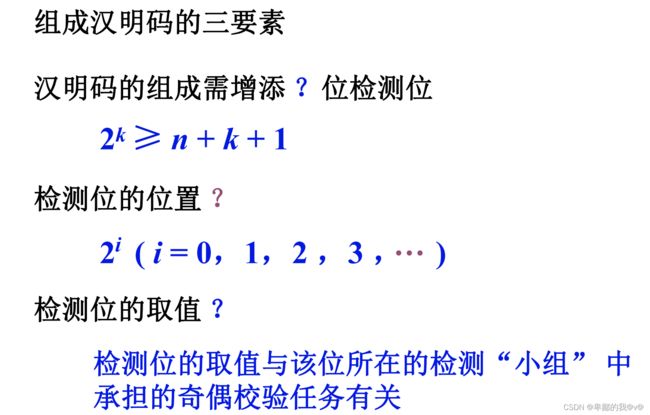

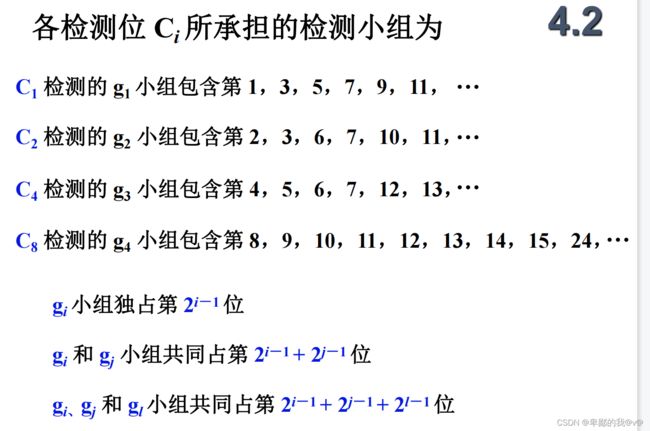

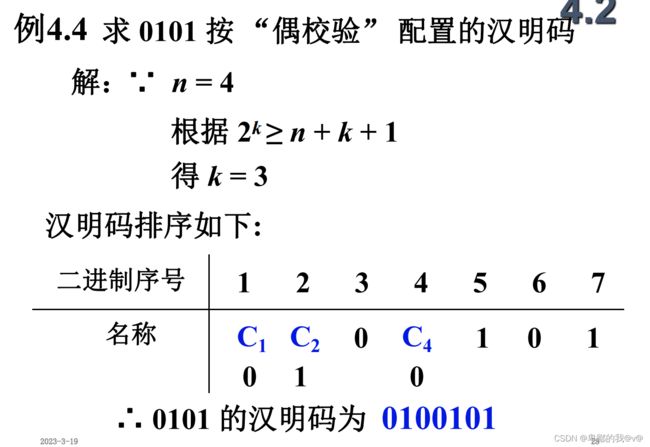

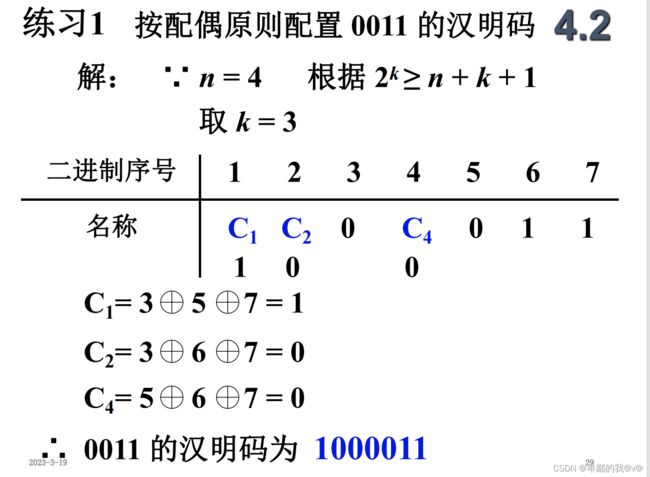

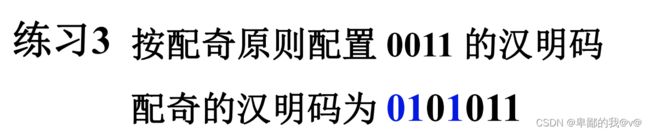

汉明码

汉明码的组成

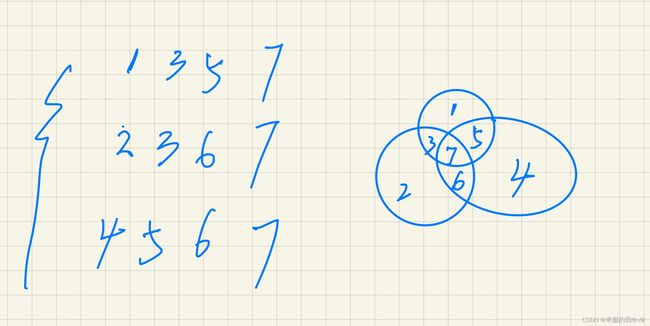

如果只简单的直接校验,一般只能知道错,但不知道是哪位,为了缩小范围,采用分组校验方式,即每一组增加一位校验位,但是这样可能会造成空间的浪费,为了既减少存储空间,又能尽可能地提高检错和纠错能力,采用这种非划分地方法,如果两位出错,找两组中间重叠地部分.......

但是校验位应该放在哪个位置呢? 为了不影响其他组地校验,必须放在和其他组不重叠的地方

第一小组特点是最后一位是1

第二小组特点是倒数第二位是1

第三小组特点是倒数第三位是1

第四小组特点是倒数第四位是1

配置校验码的时候,如果组内1的个数是奇数就1,如果是偶数就是0

机器的配置方法是取异或。

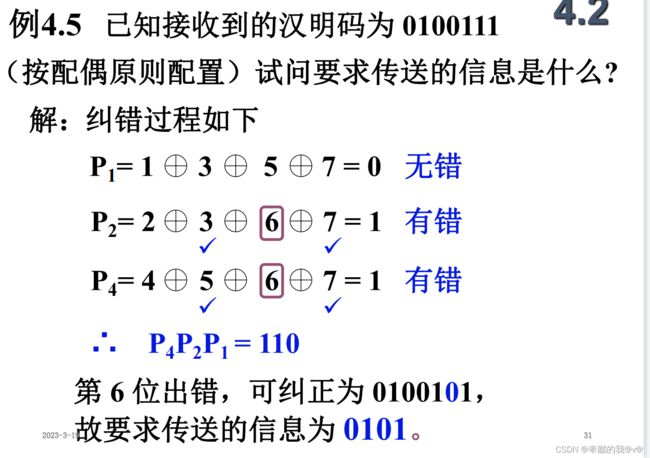

汉明码的纠错

如果是校验位出错可不纠错

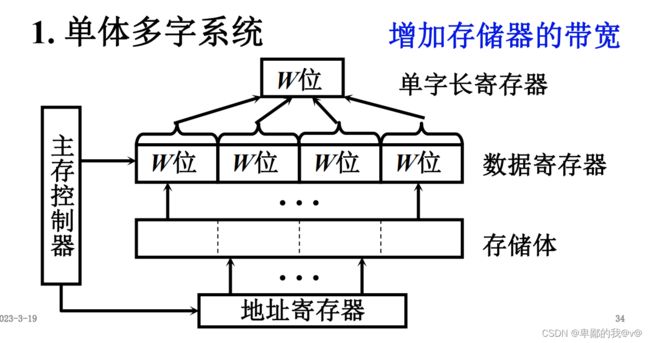

提高访问速度的措施

单体多字和多体并行系统

给一个地址可以连续访问多个字,地址寄存器给一个地址给存储体,根据这个地址在存储体中连续取出四个存储字,数据寄存器连接一个单字长的寄存器,单字长寄存器是送给CPU的,CPU再取后面字的时候不用再给地址了,直接连续访问四个字

这种方法的缺点在于只能访问连续的字

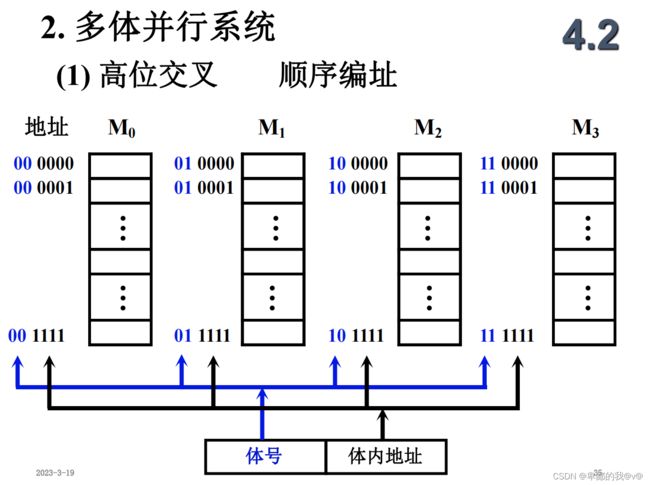

高位体号,低位地址,显然他没有提升带宽

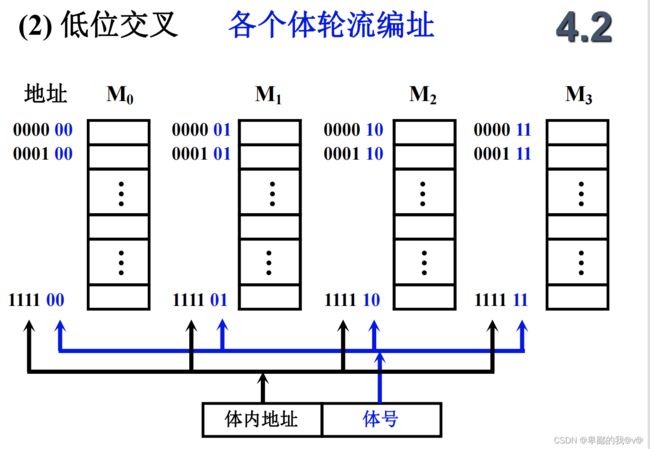

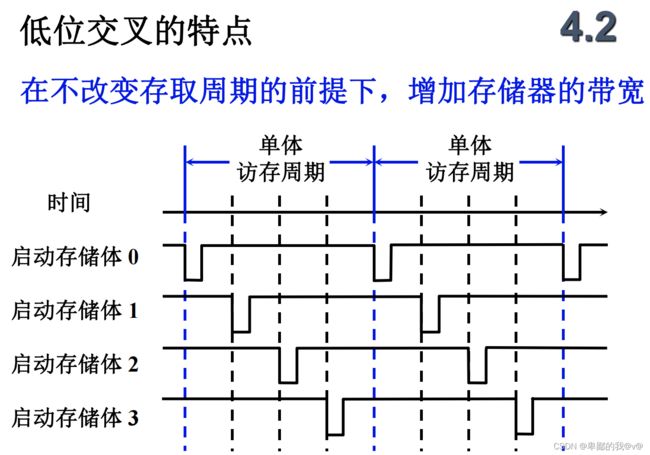

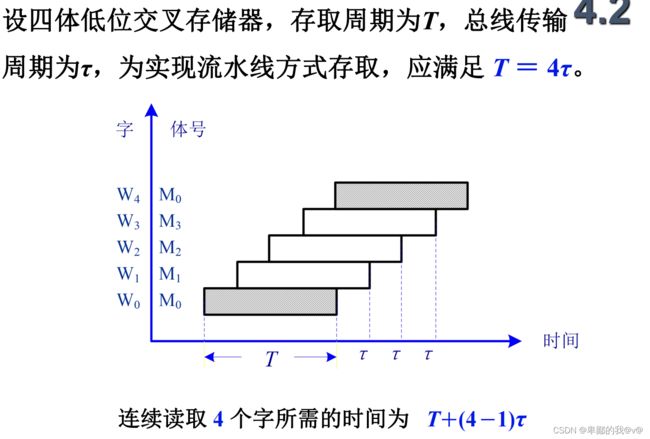

低位体号,高位地址,取出连续的地址的时候多个存储体可以并行工作

低位交叉和流水线

流水线的分类

- 指令

- 浮点

- 作业

- 任务

流水线的特点

- 硬件相互独立

- 任务的划分必须是等划分的

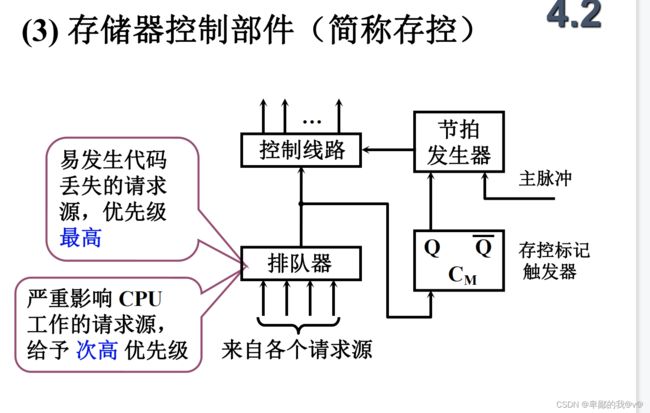

存控

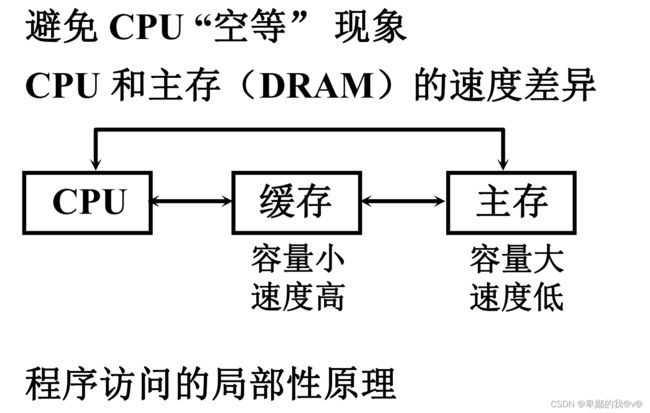

高速缓存器---Cache

引入原因

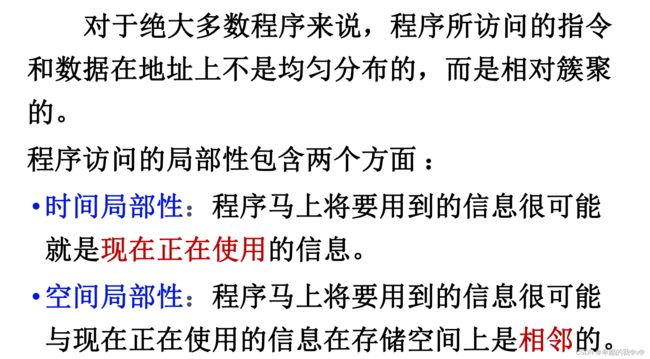

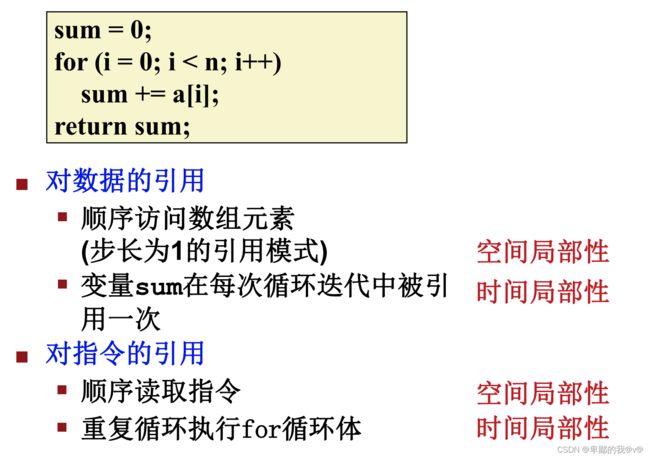

一般情况下cache的命中律更高,这是因为局部性原理

局部性原理

局部性原理一般适用于顺序和循环结构中

举例:

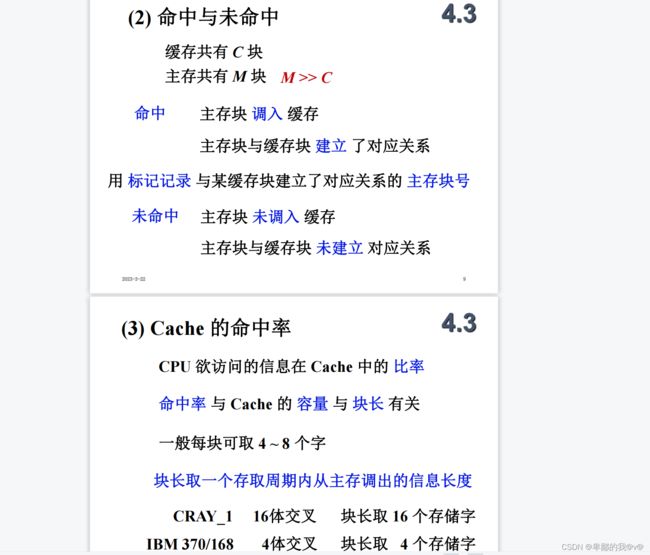

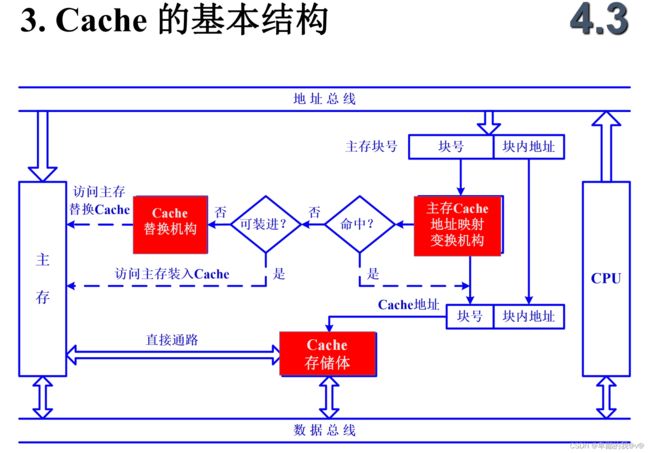

Cache的工作原理

由于程序的局部性原理,当访问主存中某一元素时可以将他相邻的元素复制到cache中,这样可以大大提高访问的效率。但是怎么划分这个局部性呢,我们采用块的方式进行数据传送

映射

![]()

都是按块存储 00 0000 for example 映射关系通过一张表体现

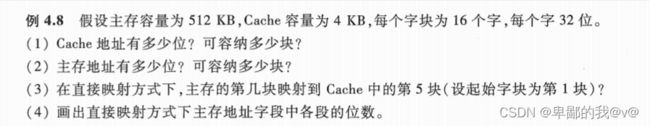

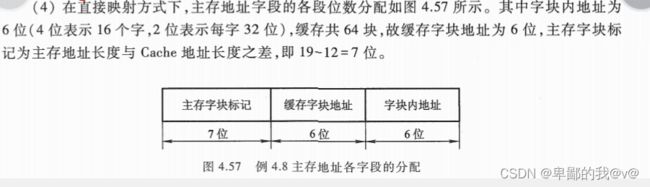

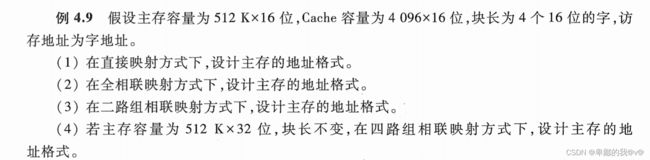

直接映射 主存块标记 cache块标记 块内字标记

- 4KB=

B 所以Cache的地址是12位。由于每个字是32位(4个字节),所以Cache一共有4KB/4B=1K个字,由于每个字块有16个字,所以可容纳1K/16=64块

B 所以Cache的地址是12位。由于每个字是32位(4个字节),所以Cache一共有4KB/4B=1K个字,由于每个字块有16个字,所以可容纳1K/16=64块 - 512KB=

B,主存的地址有19位,每个字是32位(4个字节),所以Cache有128K个字,所以可容纳128K/16=

B,主存的地址有19位,每个字是32位(4个字节),所以Cache有128K个字,所以可容纳128K/16= K块。

K块。 - 5,64+5,2*64+5,

(表示最后一块)

(表示最后一块)

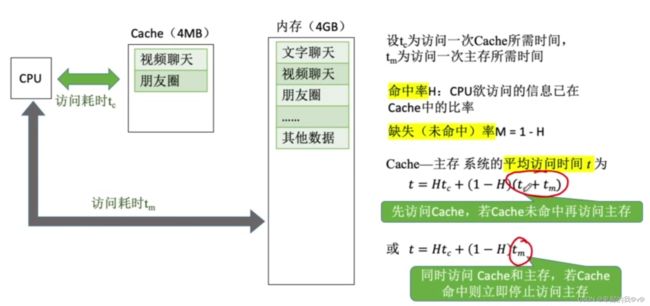

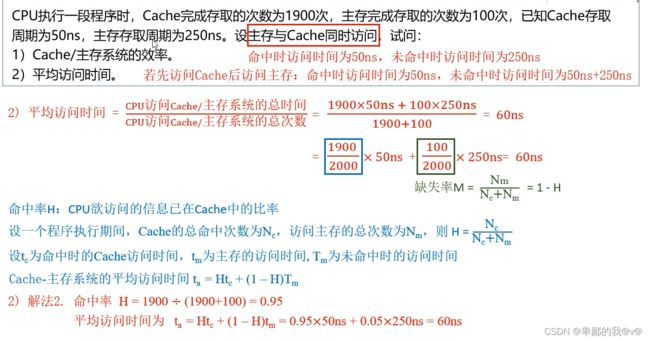

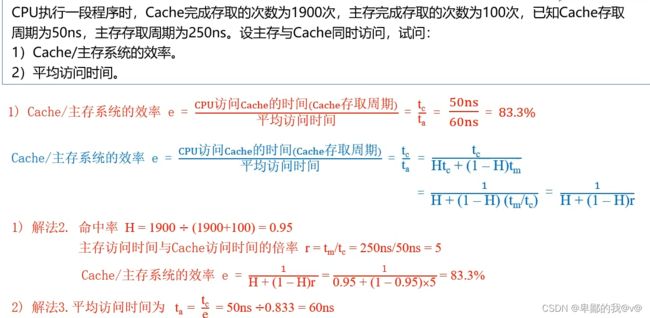

命中和命中律

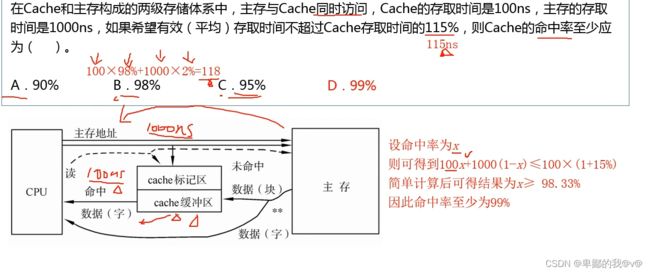

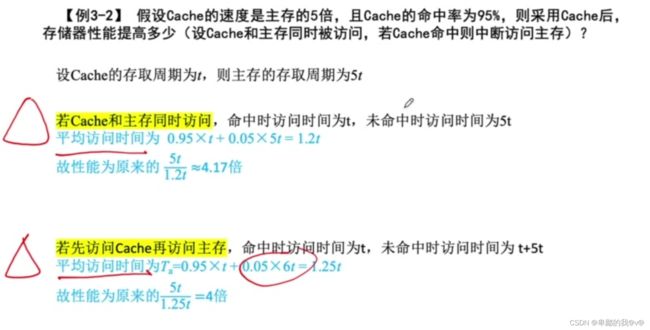

为了表示有多少数据经过Cache进入调度,有多少数据经过主存被访问,因此定义命中率这个关键词,做题的时候一定注意主存和Cache是不是同时访问。

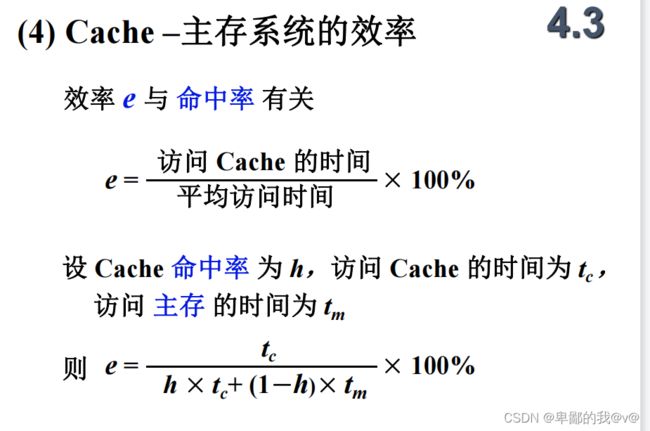

Cache--主存系统效率

性能 提高了多少,访问主存的时间除以平均访问时间-1